本文要点:

3D 集成电路需要一种方法来连接封装中垂直堆叠的多个裸片

由此,与制造工艺相匹配的硅通孔(Through-Silicon Vias,TSV)设计应运而生

硅通孔设计有助于实现更先进的封装能力,可以在封装的不同部分混用不同的通孔设计

3D 集成电路或2.5D 封装方法,以及新的处理器和 ASIC,都依赖于以某种方式来连接封装上相互堆叠的裸片。硅通孔是一种主要的互连技术,用于在 2.5D/3D 封装中通过中介层、基板、电源和堆叠的裸片间提供电气连接。这些通孔提供了与 PCB 中相同的互连功能,但设计方法完全不一样,需要根据它们在制造过程中的不同来设计。

如今,现代集成电路较常使用单一样式的硅通孔,这是因为用于裸片堆叠互连的沉积工艺较难实现。尽管在实现方面没有太多的灵活性,但硅通孔使 2.5D 封装和堆叠式集成电路的规模逐步缩小,在bump 数量增多的情况下,依然可以使bump的中体尺寸变小。在我们为设计选择硅通孔样式之前,需要考虑制造工艺以及硅通孔在制造中的困难。

硅通孔设计

3D 集成封装基于裸片与中介层之间的垂直互连

硅通孔有三种设计样式,用于连接中介层上堆叠的 3D 裸片,需要根据制造过程中的实现情况来选择这些堆叠。硅通孔结构一般用于集成了堆叠逻辑和存储器的 2.5D/3D 集成系统级封装。由于高带宽存储器占用了大量的封装基板面积,针对这些部分使用硅通孔有诸多好处,可以沿着垂直堆叠的方向提供裸片之间的连接。

在 3D 集成电路中使用

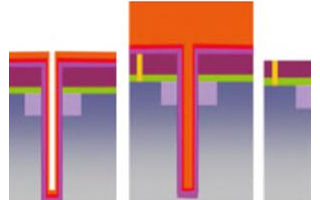

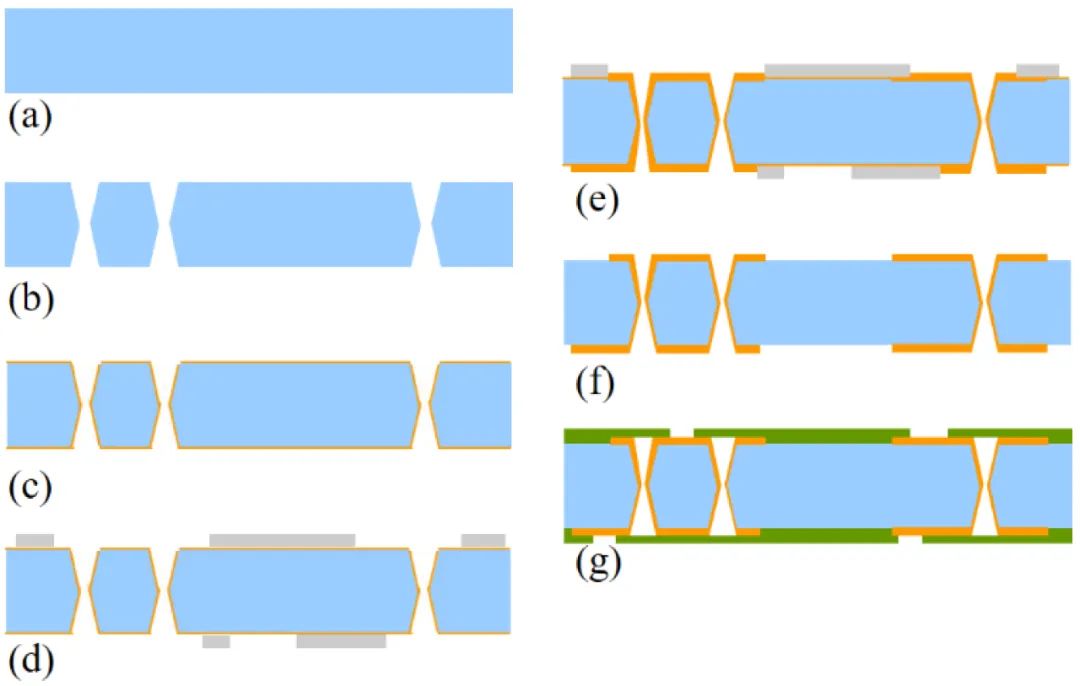

硅通孔可以放置在 3D 集成电路中使用的裸片-裸片/裸片-晶圆工艺中,以定义通过基板和 I/O 的连接。下图是以三种样式实现的硅通孔截面示意图。在这些图中,通孔提供了一个长的垂直连接,垂直横跨基板,并可进入多个裸片层。

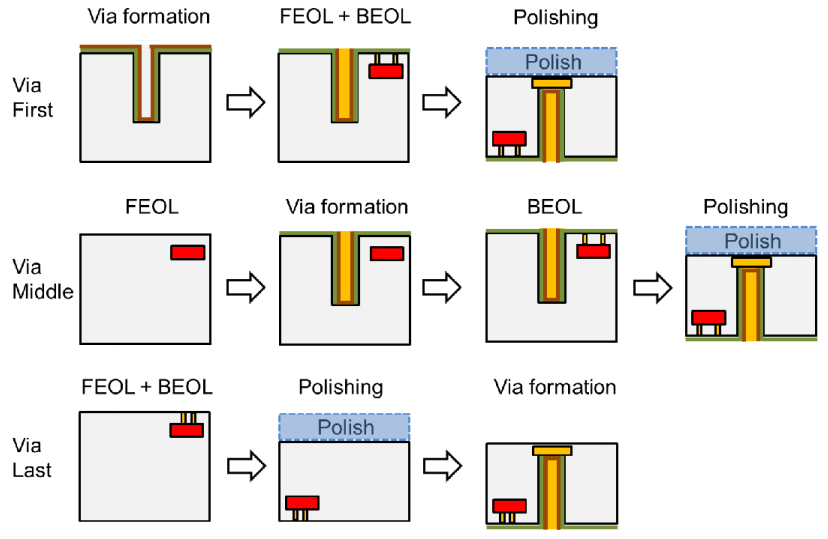

3D 集成电路中的硅通孔可以采用三种方法进行设计和放置:

硅通孔的先通孔、中通孔和后通孔工艺

先通孔

先制作通孔,然后再将元件或键合裸片摆放在中介层上。首先,在通孔中沉积金属,然后覆盖结构的顶部。堆叠裸片之间的金属化连接,用于连接基板层并完成与硅通孔的连接。

放置通孔需要在金属化之前、摆放电路之后进行。在堆叠过程中,通孔结构要达到不同的层,并提供层之间的连接。盲孔、埋孔和通孔版本的硅通孔可以在这个过程中轻松放置。

中通孔

后通孔

顾名思义,通孔是在堆叠和金属化之后形成的,也叫做背面硅通孔。在这个过程中,将一个长的通孔结构沿着封装放置并穿过基板。该过程不影响金属化,也不需要在晶圆减薄过程中纳入显现 (reveal) 工艺。

用于在硅片上形成这些硅通孔的主要活性离子蚀刻工艺,是使用六氟化硫 (SF6) 和 C4F8 钝化的 Bosch 蚀刻工艺。虽然非常大的孔可以由蚀刻掩膜定义并通过这种工艺形成,但蚀刻率对孔的长宽比非常敏感。在蚀刻之后,利用铜的电化学沉积来形成种子层,并通过电镀堆积出孔的结构。

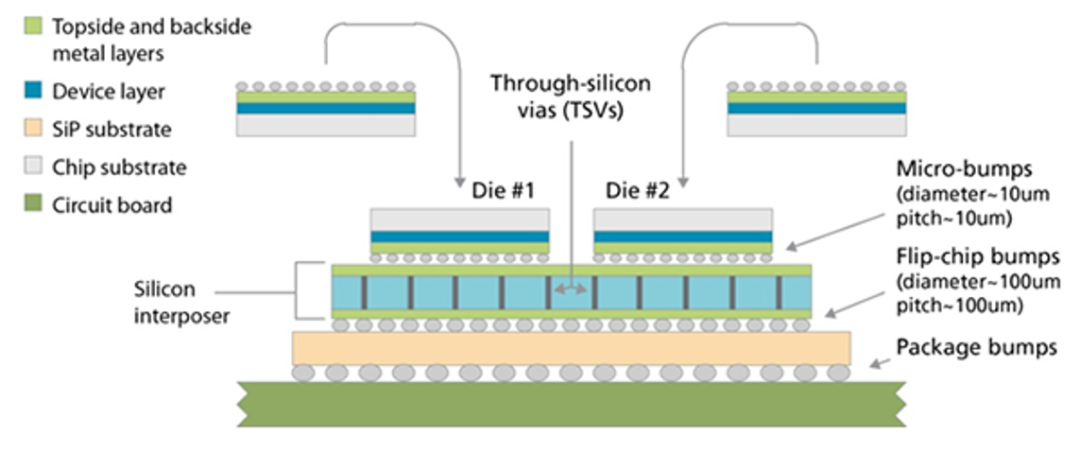

在中介层和晶圆级封装中使用

硅通孔也可用于中介层,将多个芯片或堆叠的裸片连接成 2.5D 封装。摆放在中介层上的单个芯片可以是单片集成电路或硅上堆叠裸片,每个都有自己的硅通孔。这些堆叠的元件也可以是细间距 BGA/倒装芯片封装中的非标准元件,直接粘合在中介层的金属焊盘上。然后,中介层利用倒装芯片 bump 安装到封装基板上,如下图所示:

硅中介层上的 2.5D 集成封装

中介层中硅通孔的制造工艺与单片或裸片堆叠 3D 集成电路(见上文)的制造工艺基本相同,涉及类似的蚀刻和堆积工艺。这种工艺也可以直接在芯片的晶圆上制造通孔和形成封装,称为晶圆级封装。然后,这些晶圆级封装可以粘合到异构 3D 集成电路上,或者可以形成 bump,直接安装到 2.5D 封装中使用的中介层上。

硅通孔对信号完整性有何影响

按照集成电路的尺寸标准,硅通孔的结构非常大,并且长宽比较高,因此在选择硅通孔时要格外关注成本,因为这些大型结构需要更长的加工时间。此外,其直径可以达到几微米,且可能带有扇形轮廓,会带来可靠性问题。然而,尽管制造复杂性有所增加,但考虑到信号和电源完整性,依然利大于弊,包括:

电源损耗更低,因为硅通互连比水平通道要短

沿着互连长度的寄生效应更小

由于寄生电容更少,信号转换更快

对继续进行 3D 集成和异构集成来说是十分必要的

如果 VLSI 设计师想为专门的应用开发更先进的元件,就需要在物理布局中设计硅通孔,并运行基本的信号仿真来验证电气行为。

如果想在设计中实现 2.5D/3D 封装的所有优势,请使用 Cadence 的全套系统分析工具。VLSI 设计师可以将多个特征模块集成到新的设计中,并定义中介层连接,实现持续集成和扩展。强大的场求解器提供全套软件仿真功能,与电路设计和 PCB layout 软件集成,打造了一个完整的系统设计工具包,适用于各类应用和各种复杂程度的设计。

-

集成电路

+关注

关注

5391文章

11618浏览量

363087

发布评论请先 登录

相关推荐

TSV三维堆叠芯片的可靠性问题

用平面锥制造100μm深10μm宽的高纵横比硅通孔

一文了解硅通孔(TSV)及玻璃通孔(TGV)技术

Samsung 和Cadence在3D-IC热管理方面展开突破性合作

借助云计算加速3D-IC可靠性的机械应力模拟

硅通孔技术可靠性技术概述

3D-IC 以及传热模型的重要性

技术资讯 I 3D-IC 中 硅通孔TSV 的设计与制造

技术资讯 I 3D-IC 中 硅通孔TSV 的设计与制造

评论