电路中或传输线上的阻抗失配会产生反射,回到信号源。

当信号反射时,向末端负载传输的功率就会减少。

阻抗匹配发挥了一种双重作用,即通过抑制反射使功率传输到负载。

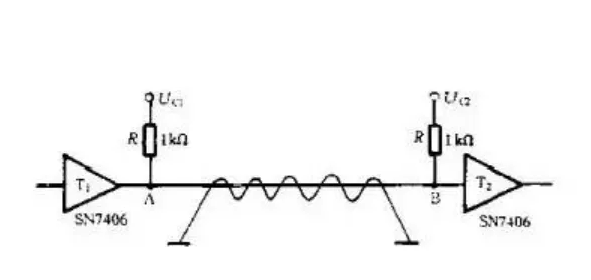

每当电磁信号沿着传输线传播时,都有可能从传输线和负载器件之间的接口上反射回来。负载可以是任何东西:另一段传输线、集成电路、天线......任何有明确阻抗的东西都是负载。当阻抗失配时,就会给信号带来灾难性的影响,导致在传输线末端测得振荡响应或阶梯式响应。

这种效应从何而来,如何通过阻抗匹配来加以解决?虽然信号反射和阻抗失配存在关联,但在线路上观察到的振铃效应往往解释不清,也很难归纳。在本文中,我们将详细解释由于互连中的阻抗失配而导致的信号反射有哪些影响。

端接线路上出现信号反射的原因

根据定义,传输线上的阻抗失配会导致信号反射;任何支持波在线性介质中传播的结构都会这样。信号反射导致在传输线接收端读出的电压出现振荡,或者表现出过长的响应,类似于不同电平之间的阶梯。当反射发生时,传输线上负载器件输入端的电压和电流可能表现出过冲或下冲,具体取决于反射信号相对于输入信号的极性。

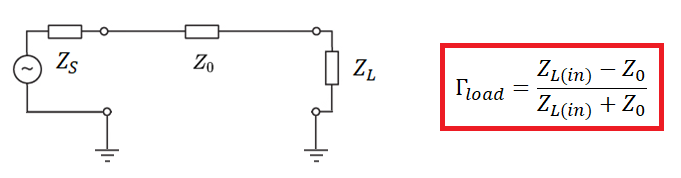

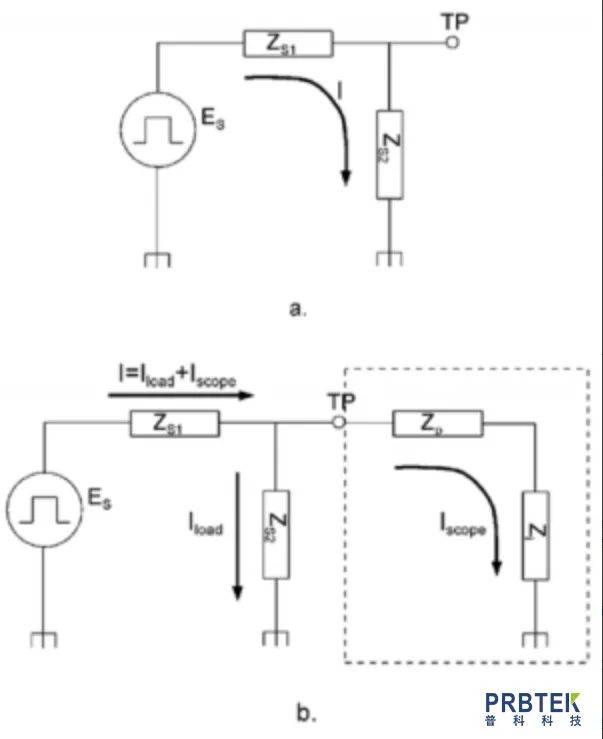

定义反射信号强度的主要方程式是反射系数方程式。对于到达负载输入阻抗的行进信号,在负载输入端的反射系数为:

对于这种典型的传输线配置,其反射系数在器件的负载端定义。对于到达传输线源端的波,也定义了一个类似的方程式。

从这个方程可以看出,如果负载的输入阻抗与线路阻抗失配,在负载处就会发生反射。同样的道理也适用于在源端观察到的输入阻抗。在每次反射后,由于线路两端的连续反射,会出现相位偏移和信号电平降低。

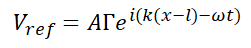

从线路负载端反射的波的方程式

在上述方程中,系数 A 是线路上信号的初始振幅。

这两个方程的有趣之处在于,只要知道上述方程中的系数,它们就能完全描述阻抗失配的信号反射行为。传输线的行为仿真非常麻烦,要么需要使用 3D 电磁场求解器,要么需要等效的集总电路模型。在实践中,可以简单地绘制出输入波及其相位偏移的反射图,就可以获得在时域中的负载输入端测量的波形。基本上,一些 SPICE 模型就是通过这种方法来计算在负载输入端测量的波形。

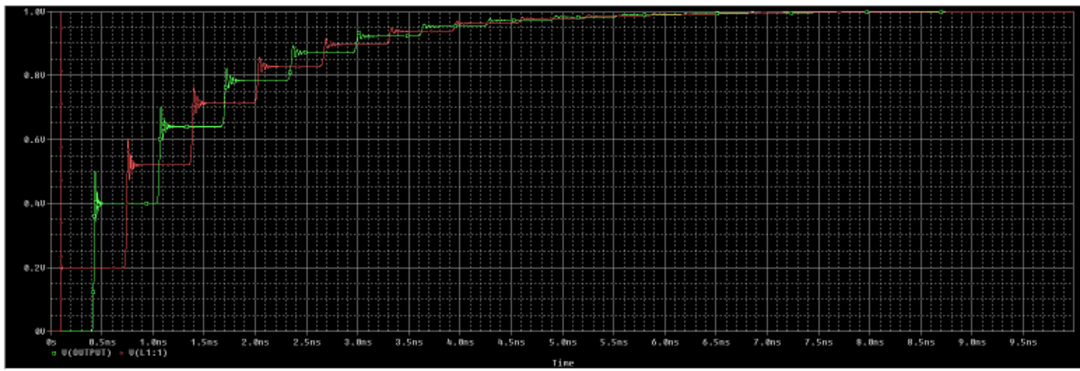

对于高负载阻抗,在负载处观察到的输入信号与反射信号相叠加,将产生一个波形,形状如下图所示:

由于高阻抗负载的信号反射而产生的明显震荡

为什么会出现明显的过阻尼响应?

如果在网上搜索关于信号反射和阻抗失配的资料,绝大多数都是考虑 50 欧姆传输线连接到高阻抗负载的情况,特别是 CMOS 逻辑电路。由于反射系数的原因,反射的信号不会反转。相反,功率只有在线路上来回反射之后才到达负载。然后,我们看到在传输线和负载之间的界面上出现了上述缓慢上升的情况。

低阻抗负载的信号反射和阻抗失配

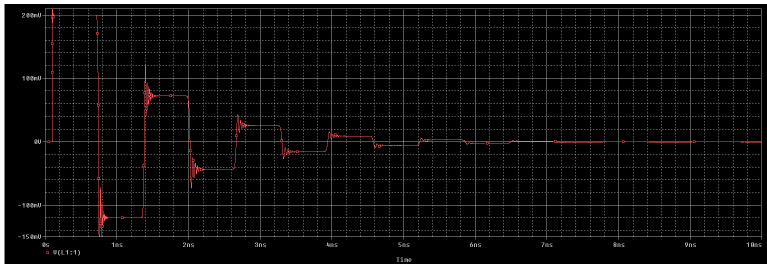

在低阻抗下,输入波最初会反转,因为反射系数小于零。这就产生了明显的下冲。然后,反射波将继续在线路上来回流通,在两端反射和反转,产生如下所示的波形。这看起来很像欠阻尼振荡,但它们不完全是一回事。无损失配不会出现这种行为,这种情况下不会有任何阻尼机制。

由于低阻抗负载的信号反射而产生的明显震荡

与传输线一起使用的现代 IC 通常在驱动端(也可能在接收端)使用片内端接 (ODT)。对于线路驱动器或收发器等原件,线路的源端可能实现 50 欧姆的阻抗。负载器件可能没有使用片内端接,这意味着需要使用一个并联电阻、上拉电阻或 Thevenin 端接。

应用这些终端方案的目的是将信号设置在所需的电平,同时将负载的输入阻抗设置为等于线路的特性阻抗。在线路的负载端应用外部端接,或在低阻抗驱动器的源端应用串联端接之前,请先查阅产品手册,看看该器件是否使用了片内端接。

Cadence Allegro PSpice Simulator 是业界一流的用于电路设计和仿真的PCB 设计和分析软件之一。使用该软件可以模拟到达传输线负载端的波形,以便在设计端接网络时评估任何信号反射和阻抗失配。

-

电磁

+关注

关注

15文章

1133浏览量

51800 -

信号

+关注

关注

11文章

2790浏览量

76736

发布评论请先 登录

相关推荐

高频信号中的阻抗特性 三相电系统中的阻抗分析

技术资讯 I 如何使用 Allegro X PCB Editor 优化RF布线和阻抗

技术资讯 I 信号反射和阻抗失配的联系

技术资讯 I 信号反射和阻抗失配的联系

评论