半导体产业本就是一个下游应用需求拉动的市场。化。

数智化是推动未来经济发展的重要引擎,新能源汽车的暴涨给汽车芯片带来了旺盛的需求。两大风口加持下,也给作为半导体行业底层科技的EDA带来各种变化。在这新春伊始,我们将重点谈谈,由此带来的芯片开发将面临的多重验证挑战。

No.1

两大未来风口:

数智化+汽车芯片

利用大数据、云计算、物联网、AI、5G及自动驾驶等新技术的运用,使得企业整个组织系统和业务链迅速升级,更助推着各细分领域头部的整合。而芯片又为其提供着底层技术的支持。不知不觉,芯片-终端-软件,整个半导体行业已经进入了应用定义硬件的时代。

AI应用不断激增、异构计算需求旺盛,基于智能多元化应用产生的海量数据,无疑推动市场对算力的需求。高性能计算和通信、数据存储等领域逐渐成为下一代风口。

此外,2022年的缺芯危机曾引来一波“投资”高潮。如今潮水褪去,支撑起未来半导体的却是汽车芯片。新能源汽车近年来发展势不可挡,层层剥茧之下,汽车赛道的下半场是智能化的征途,本质还是芯片算力的群雄逐鹿。高算力、高带宽、多核异构的高性能芯片是未来发展的关键,也是决定智能汽车的性能和表现的核心,这也更进一步推动了高性能芯片需求的快速增长。

数智化和汽车芯片,无疑是未来经济增长的两大风口,也是未来半导体产业发展增长的新方向。

No.2

多重验证挑战

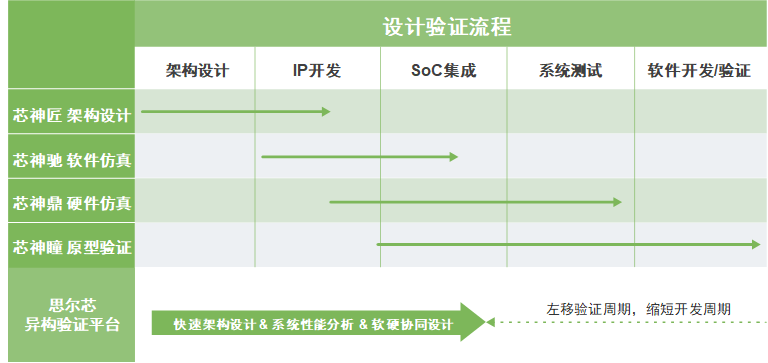

应对这两大风口,半导体产业下游倒逼中游,中游推动上游。无论是支撑高算力的智能芯片,还是适用于汽车的多核异构的高性能芯片,芯片的设计开发,及其支撑技术也因此迎来新的改变,更面临着多重验证挑战。纵观整个芯片开发流程,重中之重的是芯片前期的设计与验证。因为通常芯片验证在整个研发项目进度中占据过半,并且决定了芯片的成败。以研发一颗GPU SoC为例,大约70%的投入都是在数字前端设计。首先,随着芯片设计成本日益高涨,以及算力与储存需求爆发式增长,系统级芯片验证变得极其复杂,先进SoC的验证压力也呈指数及增长。工程师们所需要的验证工具早已不仅仅局限在满足功能验证需求,更多需要从设计、架构、软硬协同、功耗等方面优化探索。

“造芯的第一步是选对芯片架构。”思尔芯总裁林铠鹏表示,“但数智化推动市场快速变化,新技术的到来让应用更多元化,这也让IC设计公司很难根据芯片未来的使用场景明确芯片定位。为了适应其变化,工程师们需要更灵活的架构探索,以及更多重的验证手段。”

例如在现流行的异构集成中,会通过异构计算整合不同架构的运算单元来进行并行计算,这也已经成为当前解决算力瓶颈的重要方式之一。它的出现让整个设计验证流程发生了根本性变化,异构验证是如今的工程师们所期待的新方法。

因为不同的运算单元有不同的架构设计,对信息流也有不同的处理方式,这些都需要针对其特性使用不同验证的方法学。在验证的难度越来越大的今天,单一工具并不能保证设计的可靠性。

此外,EDA服务云计算技术迭代的同时,云计算也在反哺EDA。特别是芯片设计变得愈发复杂之后,算力和存储这两块开始出现了瓶颈,传统的自建数据中心已不堪重负。如何帮助IC设计企业获得算力的充沛及弹性供给,减少IT基础设施,还能获得更多的EDA工具,以及IP相关资源的整合,大幅降低时间与成本,也是如今芯片设计验证面临的挑战。

No.3

异构验证平台

如何应对新风口下的多重验证挑战?思尔芯,这家国产原型验证的龙头企业,最近并购和自研不断,为高算力、多核异构的高性能芯片的验证挑战提供了高效的解决方案。思尔芯董事长兼CEO林俊雄表示,“在芯片设计的不同节点,工程师所用的工具是不一样的。当前思尔芯已有丰富的产品线,覆盖验证云服务、架构设计、软件仿真、硬件仿真、原型验证等工具。广泛应用于物联网、云计算、5G通信、智慧医疗、汽车电子等终端领域。我们的异构验证方法学,在研究怎样降低验证工程复杂度的同时,还能保证验证的可靠性,提升验证效率。”重捋一下芯片设计的流程,思尔芯的验证工具是如何覆盖整个芯片设计验证的全流程?

需求分析与架构设计

芯片设计的起点都是需求分析。在一颗芯片的设计之初,思尔芯的Genesis芯神匠架构设计软件就可以给工程师提供一个建模,分析,仿真和软硬件协作的平台,利用建模方法学实现电子系统级(Electronic System Level,ESL)设计流程,可用于开发半导体、航空和电子系统产品。通过该方案可创建周期精度的模型以便进行早期性能和功耗分析,也可进行时序和功耗的仿真,还能搭配芯神瞳原型验证平台提前进行软硬件协同设计。

面对庞杂的代码,工程师想要确保设计可靠性,这就需要对设计进行验证,即功能验证。软件仿真、硬件仿真和原型验证等方法学基本覆盖了整个功能验证方法,工程师们针对不同阶段需结合使用不同验证的方法学。

软件仿真

软件仿真适合小型设计和模块级仿真。其实从早期的需求分析与架构探索就可以使用,还可以覆盖功能验证中的RTL级仿真、超大容量硬件仿真加速器、快速原型系统等多个应用场景。可以说是每个验证工程师常规必备的EDA工具。

PegaSim 芯神驰是思尔芯近日推出的一款高性能、多语言混合的商用数字软件仿真工具,已得到多家海内外厂商验证。其采用了创新的架构算法,实现了高性能的仿真和约束求解器引擎,对System Verilog语言、Verilog 语言、VHDL语言和UVM方法学等提供了广泛的支持,同时支持时序反标和门级后仿真,并可提供功能覆盖率、代码覆盖率分析等功能。同时创新的软件架构允许仿真器支持不同的处理器架构—— x86-64、RISC-V、ARM等。

此款商用数字软件仿真工具采用创新的商业模式,可以很好地满足企业多样化的需求,帮助企业解决license使用紧张、算力不足、license被设计工程师长期占用等问题。真正为企业做到降本增效,加速芯片设计,确保整个芯片设计流程对需求规格的完整实现,以及项目按照预期的验证计划高效地推进。

硬件仿真

硬件仿真是对完整的SoC设计进行加速仿真并调试,包括SoC设计的系统级功能验证、IP设计验证,多应用于设计前期的RTL功能验证。与原型验证系统相比,最大的优点就是其强大的调试能力,可以检查出有没有深度错误或性能瓶颈。

OmniArk 芯神鼎是近日思尔芯通过并购整合推出的一款企业级硬件仿真系统。其采用超大规模可扩展商用阵列架构设计,最大设计规模可达20亿门,满足从IP级到系统级的功能验证。基于创新的全自动编译流程、高效调试纠错能力、丰富的仿真验证模式,以及千倍以上的仿真加速,让这款企业级硬件仿真系统成为思尔芯开启EDA验证新时代的重磅产品。

原型验证

原型验证通过将RTL移植到现场可编程门阵列来验证芯片功能。它会帮助工程师在芯片设计过程中搭建软硬件一体的系统验证环境,多用于SoC设计后期的系统级功能和性能验证。在流片前工程师们就可以在SoC的基本功能验证通过后,立刻开始驱动和应用软件开发。甚至可以在流片前就给有需求的客户进行芯片演示,进行预售。而且缩短了整个验证周期,加速了产品上市时间。

思尔芯的Prodigy 芯神瞳原型验证解决方案是业内领先的数字集成电路前端验证解决方案,帮助全球顶尖的芯片企业开发IC和验证,适用于验证专门应用的集成电路(ASIC)和片上系统(SoC)的系统级功能和性能验证。还可以帮助芯片开发者提早进行嵌入式软件开发及软硬件协同设计,从而加快芯片产品上市速度,抢占市场先机。该解决方案包含原型验证硬件、自动原型编译软件、深度调试套件、协同仿真套件、云管理软件以及外置应用库。多组合方案能够为开发者提供多种容量范围,并覆盖各类ASIC以及SoC设计的验证需求。

验证云服务

思尔芯还推出了验证云服务,主要用于超大规模数字集成电路前端功能验证,包括架构探索、算法验证、IP/模块级验证、芯片级验证、固件验证、软件验证以及兼容性测试等。通过将验证算力资源的云端虚拟化,实现算力管理、集群管理、多用户管理、虚机/容器资源管理等一系列功能。

在数智化驱动半导体行业快速发展的同时,作为支撑起数字经济的底座科技EDA也在悄然发生改变。在新的一年里,想要大展宏图的芯片开发也正积极应对以上挑战。无论是拓展到更多的领域,还是前瞻未来更多创新领域,思尔芯始终着眼于未来,不断激发研发人员的创新活力,快速响应市场变化,用成熟稳定的产品服务于每一个客户。相信不久的未来,因为有更多像思尔芯这样的活力领军企业,将有一个更好的生态,更辉煌的未来。

//

关于思尔芯S2C

思尔芯(S2C)自2004年设立上海总部以来始终专注于集成电路EDA领域。作为业内知名的EDA解决方案专家,公司业务聚焦于数字芯片的前端验证,已覆盖验证云服务、架构设计、软件仿真、硬件仿真、原型验证等工具。已与超过600家国内外企业建立了良好的合作关系,服务于人工智能、超级计算、图像处理、数据存储、信号处理等数字电路设计功能的实现,广泛应用于物联网、云计算、5G通信、智慧医疗、汽车电子等终端领域。

公司总部位于上海,并建立了全球化的技术研发与市场服务网络,在北京、深圳、西安、香港、东京、首尔及圣何塞等地均设有分支机构或办事处。

思尔芯在EDA领域的技术实力受到了业界的广泛认可,通过多年耕耘,已在原型验证领域构筑了技术与市场的双领先优势。并参与了我国EDA团体标准的制定,承担了多项国家及地方重大科研项目。

-

芯片

+关注

关注

457文章

51345浏览量

428237 -

eda

+关注

关注

71文章

2792浏览量

174068

发布评论请先 登录

相关推荐

苹果无边框OLED iPhone开发面临挑战

AMD MI300X AI芯片面临挑战

7纳米工艺面临的各种挑战与解决方案

解决验证“最后一公里”的挑战:芯神觉Claryti如何助力提升调试效率

大算力芯片面临的技术挑战和解决策略

康谋分享 | 在基于场景的AD/ADAS验证过程中,识别挑战性场景!

LF412用PSPICE验证该运放的SPICE宏模型的遇到的疑问求解

宏景智驾联合芯擎科技打造的“舱泊一体”方案完成实车验证

大规模 SoC 原型验证面临哪些技术挑战?

全光网应用面临的挑战

芯片测试和芯片验证的区别

人工智能芯片在先进封装面临的三个关键挑战

大展宏兔的芯片开发又将面临哪些验证挑战?

大展宏兔的芯片开发又将面临哪些验证挑战?

评论