现代计算机系统的许多接口都采用了 DDR 技术,其中之一涉及到处理器与内存的工作方式,人工智能(AI)、机器学习(ML)和数据挖掘等新应用也在不断推动这种接口突破新的极限。针对高带宽同步动态随机存取存储器(SDRAM)的最新 DDR5 版本 DDR 接口的开发始于 2017 年,而备受期待的 JESD79-5 DDR5 SDRAM 标准于 2020 年 7 月发布。

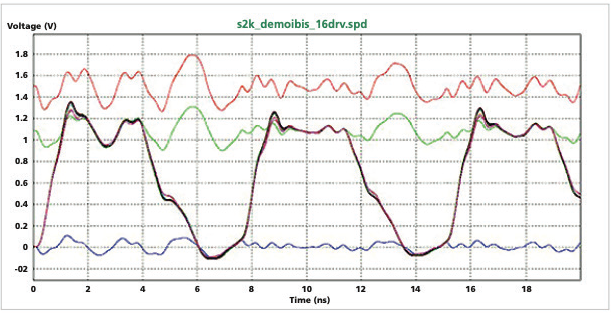

“兼顾电源影响”指的是一种先进的信号完整性仿真方法,可以同时分析信号和电源噪声(图 1)。

图1:兼顾电源影响的信号完整性仿真结果

兼顾电源影响的信号完整性解决方案必须考虑反射、串扰、时序和其他效应,并配备相应的仿真和规则检查技术。这些效应也表明,同步开关噪声(SSN)只能代表信号和电源相互作用引起的一部分问题。SSN 关注于通过正确的返回电流路径同时进行多个信号切换的场景。

另一种需要考虑电源影响的情况是,由信号通过平面空腔耦合引起的平面噪声注入到另一信号,该信号与平行总线连接到同一电源,但不属于 SSN 分析所关注的多开关网络。噪声也可能来自 PCB 上的电压调节器。因此,SSN 仿真只是兼顾电源影响的解决方案的一部分。

最好在规则检查和布线后分析阶段实施兼顾电源影响的解决方案,因为平面和信号的相互作用/耦合发生在布线完成之后。因此,一个完整的兼顾电源影响的解决方案需要提供:

一套针对信号衰减和电源对信号的影响的快速检查方案

能够模拟大型电路的时域仿真器(多个信号网络和电源网络的结果)

电源网络和信号网络的建模

高级输入/输出(I/O)缓冲器建模

借助 Cadence Sigrity X 进行兼顾电源影响的信号完整性(SI)分析,并将其作为 DDR5 应用设计和验证流程的一部分,工程师可以确信最终产品将与规格相符,并实现更好的性能。

Sigrity X 是 Cadence 最新一代信号和电源完整性(SI/PI)解决方案。搭载了全新的用于系统级分析的强大仿真引擎,并采用旗舰 Cadence Clarity 3D Solver 场求解器创新的大规模分布式架构用于超大规模、5G 通信、汽车及航空航天应用。

将系统分析性能提升 10 倍且无损精准度

突破性的大规模分布式仿真实现云端大规模复杂分析

紧密集成、业界领先的 SI/PI 技术在 Cadence 全设计平台可用

带来新的用户体验,用户可以在不同分析工作流程间复用,缩短复杂的系统分析设置时间

-

电源

+关注

关注

184文章

17779浏览量

250857 -

分析

+关注

关注

2文章

134浏览量

33323

发布评论请先 登录

相关推荐

是德示波器在电源完整性分析中的应用

听懂什么是信号完整性

超常材料应用于电路板进行电源完整性、信号完整性、电磁兼容性研究

Introspect DDR5/LPDDR5总线协议分析仪

移远通信《5G RedCap技术发展及应用白皮书》重磅发布

【白皮书】使用 Sigrity X 对 DDR5 应用进行兼顾电源影响的信号完整性分析

【白皮书】使用 Sigrity X 对 DDR5 应用进行兼顾电源影响的信号完整性分析

评论