为了能够让更多工程师朋友了解多核异构处理器,飞凌嵌入式特别推出了【玩转多核异构】专题,帮助大家解决在多核异构处理器的开发过程中遇到的问题。专题持续更新中,欢迎您的订阅关注。

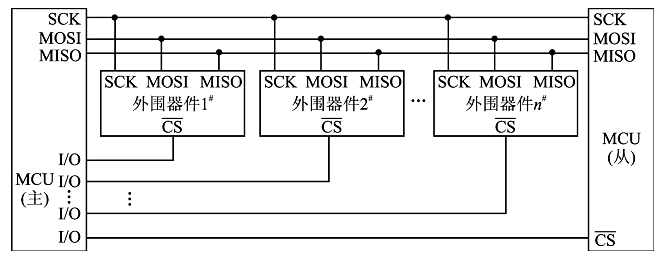

SPI(串行外围设备接口)是一种低成本、易使用的接口协议,具备全双工、高速、通讯简单的特点,被广泛应用于微控制器和外围设备芯片之间的通讯。当SPI接口作为主模式时可以连接Flash存储器、AD采样芯片、实时时钟RTC、LCD显示屏、音频芯片以及各种传感器。

随着产品功能的愈加丰富,多处理器使用SPI接口进行通讯的场景开始出现,而多个SPI设备之间通信必须由主设备(Master)来控制从设备(Slave)。小编手上的OKMX8MP-C开发板基于NXPi.MX8MPlus多核异构处理器设计,它的M核有1路SPI,因而为实现SPI的相互通讯,我们就需要两块OKMX8MP-C开发板的SPI互作主从设备进行通信。本文小编就将从应用角度为大家讲解M核SPI间通讯的实现方式。

一、SPI主模式

1. SPI初始化

SPI初始化主要包括总线时钟、管脚和相应寄存器的初始化。具体如下:

(1)SPI总线时钟:现将SPI总线倍频到800MHz,再10分频到80MHz。

CLOCK_SetRootMux(kCLOCK_RootEcspi2,kCLOCK_EcspiRootmuxSysPll1);//SPI2总线时钟使用PLL1-800MHz

(2)管脚配置:选择SPI2的四个管脚。

IOMUXC_SetPinMux(IOMUXC_ECSPI2_MISO_ECSPI2_MISO, 0U); // SPI2-MISO IOMUXC_SetPinMux(IOMUXC_ECSPI2_MOSI_ECSPI2_MOSI, 0U); // SPI2-MOSI IOMUXC_SetPinMux(IOMUXC_ECSPI2_SCLK_ECSPI2_SCLK, 0U); // SPI2-SCLK IOMUXC_SetPinMux(IOMUXC_ECSPI2_SS0_ECSPI2_SS0, 0U); // SPI2-SSO

(3)SPI速率:设置速率为500K。

#define TRANSFER_BAUDRATE 500000U // 速率 500K

(4)数据长度选择:8bit。

config->burstLength=8;//数据长度8bit

(5)四种模式选择:CPOL和CPHA的四种组合即为SPI的四种模式。

config->clockInactiveState = kECSPI_ClockInactiveStateLow; // 时钟SCL: 活动时低电平,空闲时高电平 config->dataLineInactiveState = kECSPI_DataLineInactiveStateLow;// 数据MOSI&MISO: 活动时低电平,空闲时高电平 config->chipSlectActiveState = kECSPI_ChipSelectActiveStateLow;// 片选SS: 低电平选中,高电平无效 config->polarity = kECSPI_PolarityActiveHigh; // 时钟信号极性,即CPOL为0的话 SCLK高电平有效(空闲的时候为低电平),为1的话SCLK低电平有效(空闲的时候为高电平)。 config->phase = kECSPI_ClockPhaseFirstEdge; // 时钟相位,即CPHA为0的话串行时钟的第一个跳变沿(上升沿或下降沿)采集数据,为1的话串行时钟的第二个跳变沿(上升沿或下降沿)采集数据。

(6)主模式选择:设置SPI为主模式。

config->channelConfig.channelMode = kECSPI_Master; // 主模式

(7)通道选择:一个SPI有四个硬件片选信号,每个片选信号是一个硬件通道,本程序选择通道0。

config->channel = kECSPI_Channel0; // 通道0

(8)关闭自回环:如果开启了自回环,那么SPI数据会在芯片内回环,不会到外部管脚,在程序调试时可以排除外部端子的干扰,但真实应用时,需要关闭自回环,从外部管脚收发数据。

Config->enableLoopBack = false; // 不回环,使用外部管脚

2. SPI收发流程

我们分别将两块OKMX8MP-C开发板命名为开发板1和开发板2,并且将开发板1的SPI接口采用主模式,使能收发中断;将开发板2的SPI接口采用从模式,使能收发中断。

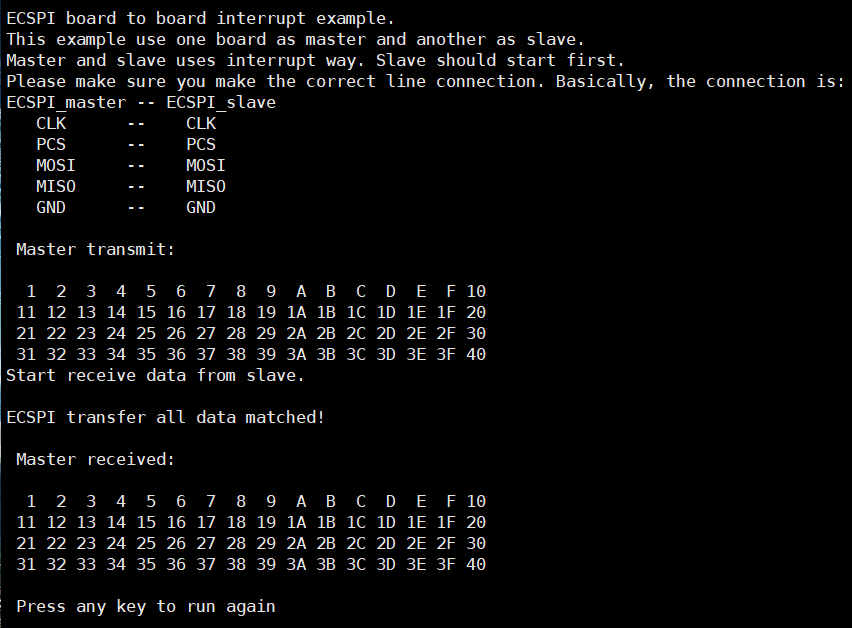

SPI主发送64字节数据,SPI从接收后,将数据回传。SPI主接收回传信息后,比对接收和发送的数据是否一致,输出比对结果。如一致,本次传输结束,等待输入任何按键启动下一次传输。

(1)SPI发送数据:EXAMPLE_ECSPI_MASTER_BASEADDR 表示为SPI2,g_m_handle为SPI实例,包含了发送接收中断及其回调函数,masterXfer为要发送的64字节数据。

ECSPI_MasterTransferNonBlocking(EXAMPLE_ECSPI_MASTER_BASEADDR, &g_m_handle, &masterXfer); //主模式中断方式发送数据

(2)SPI接收数据:SPI总线的发送和接收都是主模式控制的,因此接收函数的过程和发送是一致的。

(3)接收和发送数据对比:

for (i = 0U; i < TRANSFER_SIZE; i++) { if (masterTxData[i] != masterRxData[i]) { errorCount++; } }

二、SPI从模式

1. SPI初始化

SPI从模式初始化与主模式要保持一致,除了将工作模式设为从模式,其他设置均一样。主从模式选择:设置SPI为从模式。

config->channelConfig.channelMode = kECSPI_Slave; //从模式

2. SPI收发流程

开发板2的SPI接口采用从模式,使能收发中断。

SPI从进入等待接收状态,在片选有效后,通过接收中断获取数据,并回传信息,再次进入接收状态。

(1)SPI接收数据:EXAMPLE_ECSPI_SLAVE_BASEADDR表示为SPI2,g_m_handle为SPI实例,包含了发送接收中断及其回调函数,slaveXfer存储接收的数据。

ECSPI_SlaveTransferNonBlocking(EXAMPLE_ECSPI_SLAVE_BASEADDR, &g_s_handle, &slaveXfer); //从模式中断方式接收数据

(2)SPI发送数据:SPI总线的发送和接收都是主模式控制的,因此接收函数的过程和发送是一致的。

三、A核修改

A核设备树中若保留SPI2,内核解析设备树,在/dev下生成设备文件spidev1.0。这样待M核运行后,A核将重新对SPI2初始化,造成M核SPI功能异常,因此需要去除A核对SPI的控制。

1.修改设备树

(1)在设备树OK8MP-C.dts中,删除SPI2设备节点相关信息。

&ecspi2 { #address-cells = <1>; #size-cells = <0>; fsl,spi-num-chipselects = <1>; pinctrl-names = "default"; pinctrl-0 = <&pinctrl_ecspi2 &pinctrl_ecspi2_cs>; cs-gpios = <&gpio5 13 GPIO_ACTIVE_LOW>; status = "okay"; spidev1: spi@0 { reg = <0>; compatible = "rohm,dh2228fv"; spi-max-frequency = <500000>; }; }; pinctrl_ecspi2: ecspi2grp { fsl,pins = < MX8MP_IOMUXC_ECSPI2_SCLK__ECSPI2_SCLK 0x82 MX8MP_IOMUXC_ECSPI2_MOSI__ECSPI2_MOSI 0x82 MX8MP_IOMUXC_ECSPI2_MISO__ECSPI2_MISO 0x82 >; }; pinctrl_ecspi2_cs: ecspi2cs { fsl,pins = < MX8MP_IOMUXC_ECSPI2_SS0__GPIO5_IO13 0x40000 >; };

(2)编译生成新的内核镜像Image及设备树OK8MP-C.dtb。

(3)将生成的OK8MP-C.dtb和Image拷贝至开发板/run/media/mmcblk2p1/目录下,输入sync命令,重启开发板。

(4)输ls /dev查看发现没有SPI2设备文件spidev1.0。

四、程序验证

1.硬件连接

使用杜邦线将两块OKMX8MP-C开发板的SPI一一对应连接,线序如下:

开发板1--SPI主模式 | 开发板2--SPI从模式 | ||

管脚名称 | 开发板位置 | 管脚名称 | 开发板位置 |

MISO | P40-10 | MISO | P40-10 |

MOSI | P40-8 | MOSI | P40-8 |

SCK | P40-1 | SCK | P40-1 |

SS0 | P40-3 | SS0 | P40-3 |

GND | P40-4/P40-7 | GND | P40-4/P40-7 |

2. M核程序

修改uboot环境变量设置M核自启动,同时将M核程序forlinx_m7_tcm_firmware.bin

放到/run/media/mmcblk2p1/目录下。注意,SPI主模式程序须放入开发板1,SPI从模式程序须放入开发板2。

3. 实际测试

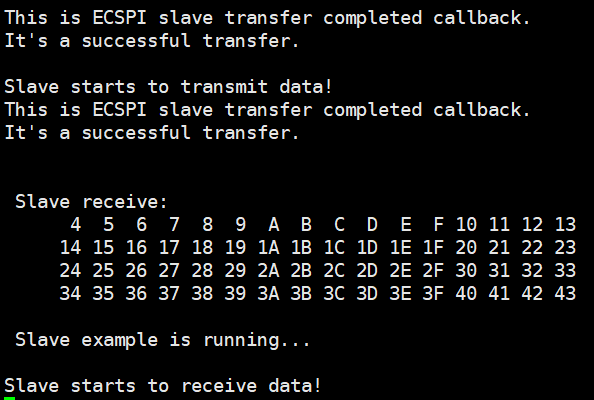

(1)开发板2先上电,M核程序启动,完成SPI初始化后,进入接收等待状态;

(2)开发板1后上电,M核程序启动,完成SPI初始化后,主动发送64字节数据;

(3)开发板2的SPI接收数据,通过串口打印接收的数据,并将接收的数据再次发送;

(4)开发板1的SPI接收到回传信息,通过串口打印接收的数据。和发送数据比对,输出结果。

(5)此时在开发板1调试串口输入任意键,即可开启新一轮的SPI发送和接收流程。

-

ARM

+关注

关注

135文章

9589浏览量

393765 -

NXP

+关注

关注

61文章

1411浏览量

199408 -

SPI

+关注

关注

17文章

1900浏览量

102174 -

多核异构

+关注

关注

0文章

24浏览量

5672

发布评论请先 登录

请问如何使用Flexbuild 将 Debian 镜像刷新到 i.MX8M Plus EVK 上的 eMMC?

如何通过 FPGA 的 QSPI 接口对 MIMX8ML8CVNKZAB 进行 DMA 访问?

将 Linux BSP 用于 i.MX8M Plus 或 i.MX8 Quad Max 平台,遇到的几个问题求解

无法将 FlexCan 与 i.MX 8M Plus EVK 板一起使用,为什么?

如何下载 i.MX 8M Plus SDK?

基于运行 Yocto Kirkstone 的 i.MX8M Mini 平台上遇到以太网配置问题求解

如何在“i.MX 8M Plus EVK Board”上的网络浏览器中打开.html文件?

探索FRDM - IMX8MPLUS开发板:开启嵌入式开发新旅程

既要稳定性,还要性价比的工业级开发板 — 米尔i.MX91

恩智浦FRDM i.MX 8M Plus开发板详解

【飞凌嵌入式】基于i.MX9352开发板M核的FreeRTOS设计例程

【玩转多核异构】i.MX8M Plus开发板的M核SPI主从模式通讯

【玩转多核异构】i.MX8M Plus开发板的M核SPI主从模式通讯

评论