在去年 12 月的国际电子器件大会 (IEDM) 上,有一节关于背面电源分配网络(Backside Power Delivery Networks)的简短课程。主讲人是IMEC(微电子研究中心)的 Gaspard Hiblot,标题为《Process Architectures Changes to Improve Power Delivery(通过改变流程架构来改善电源分配)》;IMEC的高层人员Geert Hellings 和 Julien Ryckaert 也参与了内容创作。该演讲的幻灯片多达 80 页,因此本文不做赘述,只介绍其中的一些重点。

设计技术协同优化(DTCO)

现代工艺设计与设计将要使用的硅结构的某些方面密切相关。这与十年前的情况截然不同,当时制程技术开发团队基本上会交给设计团队一套 SPICE 模型和 layout 设计规则。而我们采用的新方法称为“设计技术协同优化”,简称为 DTCO(Design Technology Co-Optimization)。

这个词首次出现在 2016 年的 CDNLive (即Cadence用户大会的旧称,现称为CadenceLIVE)Europe 会议上,当时 Luca Matti 展示了他在 IMEC 的工作——即将到来的 7nm 和 5nm 制程节点。在 DTCO 的早期发展阶段,重点在于对半导体制程进行一些调整,如有源栅极触点,旨在减少标准单元的轨道数量。

如今,简单的维度缩放(即“摩尔定律”)已成为明日黄花,需要采用 DTCO 方法来保持缩放规律。其中一个巨大的挑战是过孔的电阻。一直以来,我们使用铜材料来制造过孔,因为铜的电阻很低。但铜需要一个扩散阻挡层,如氮化钽 (TaN),这会造成两个问题——首先,阻挡层会占据空间,因此减少了过孔中铜的横截面积;其次,阻挡层位于过孔底部,电流必须流过阻挡层。而阻挡层金属的电阻高于铜,因此会增加过孔电阻。

铜线也有类似的问题,由于铜中的晶粒大小和铜线占据侧壁的空间百分比增加,在 100nm 线宽以下,铜的电阻率开始增加。经常有人提议用钌来解决这个问题,因为它不需要阻挡层,在尺寸极小时电阻率也很低。但据我所知,并没有人用钌代替铜。在最低的过孔中,甚至是 M0 互连中,有些人会使用钴。

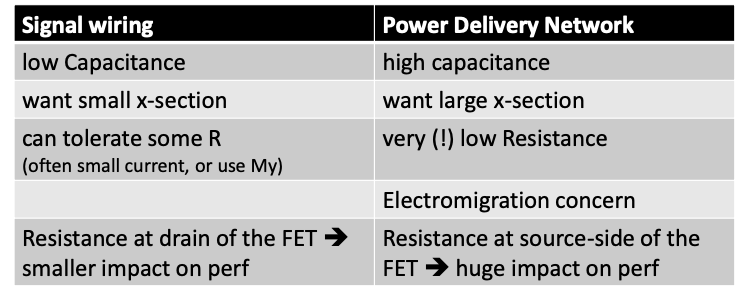

这些与互连有关的问题会影响到信号、时钟和功耗。不过,信号布线和电源分配网络 (PDN) 所面临的权衡取舍是不同的。电源需要低电阻,与电容关系不大(因为电压不变)。与普通信号不同,电源分配网络要传输大电流,这让电迁移成为了一个难题。为此,通常会采用更复杂的制程工艺,来区分电源和信号布线。

背面配电

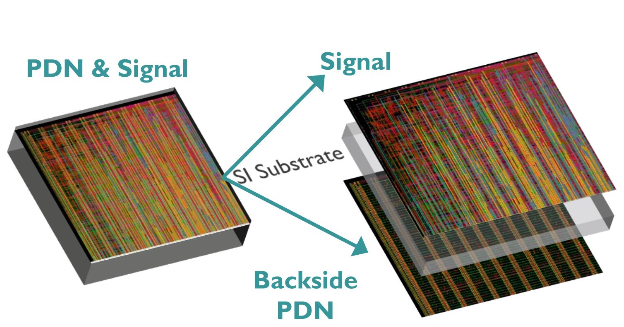

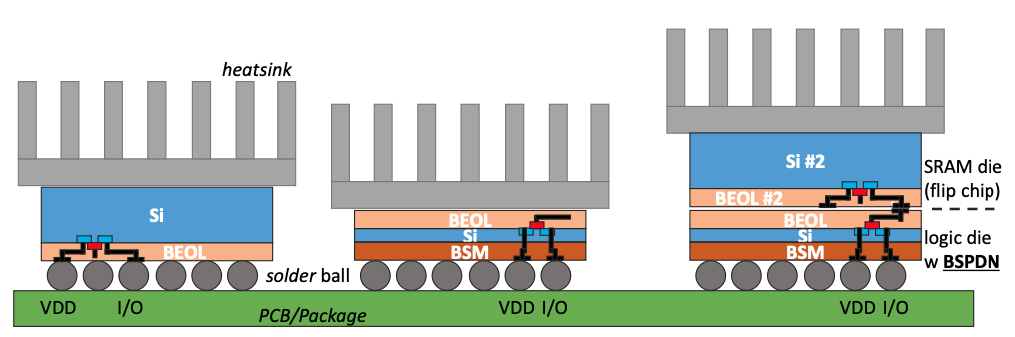

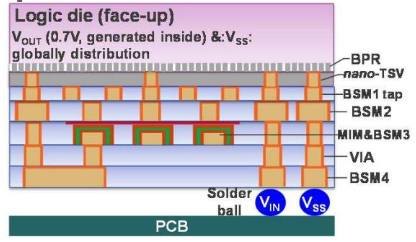

最终的区别在于将 PDN 与信号完全分开,在背面创建 PDN。PDN 位于减薄晶圆的背面,通过硅过孔 (TSV) 连接到晶体管和正面互连。

深入了解背面电源分配网络 (Backside power delivery networks,即 BS-PDN)——

独特优势

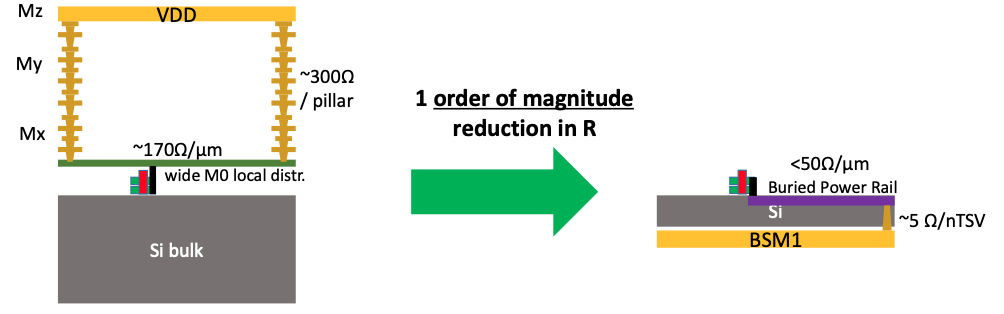

将片上压降减少了一个数量级

如下图所示,约 300Ω 的过孔柱减少到仅为 5Ω 的 TSV,这也大大减少了片上压降。

扩展了芯片面积

这在很大程度上取决于制程工艺的不同方面(如 TSV 周围禁布区的尺寸),也取决于 EDA 工具。

如Cadence Innovus 一类工具中的布线器应该可以更轻松地进行信号布线,PDN 不会在互连堆栈中造成阻碍。但具体的获益有多大,还需要进行实验。

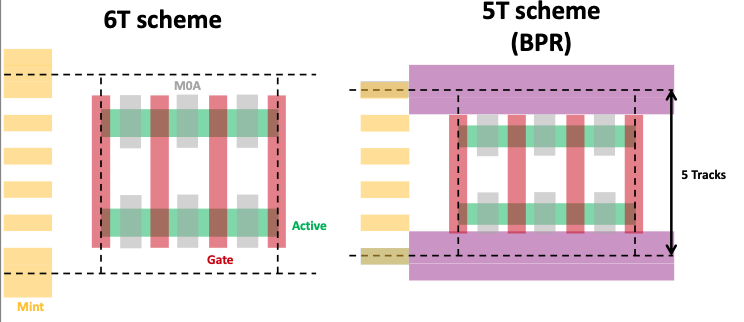

如果使用埋入式电源轨 (BPR),可以减少标准单元中的轨道数量,因此可以将芯片面积扩展大约 15-20%。

降低 BEOL 中精细金属的复杂性

铜经常采用双镶嵌工艺,很难在同一层上混合宽金属线(用于电源)和窄金属线(用于信号)。

更易于实现晶圆对晶圆键合工艺,以便在逻辑上堆叠存储器

倒装 SRAM 裸片由逻辑裸片配电,因此可以有效地由相同的 BS-PDN 配电。

三种基本方法

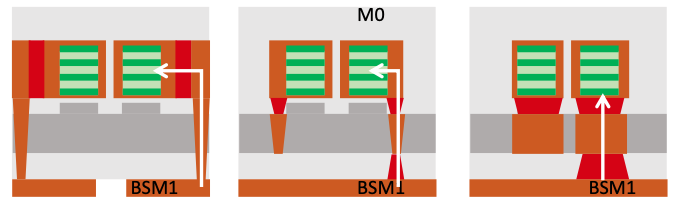

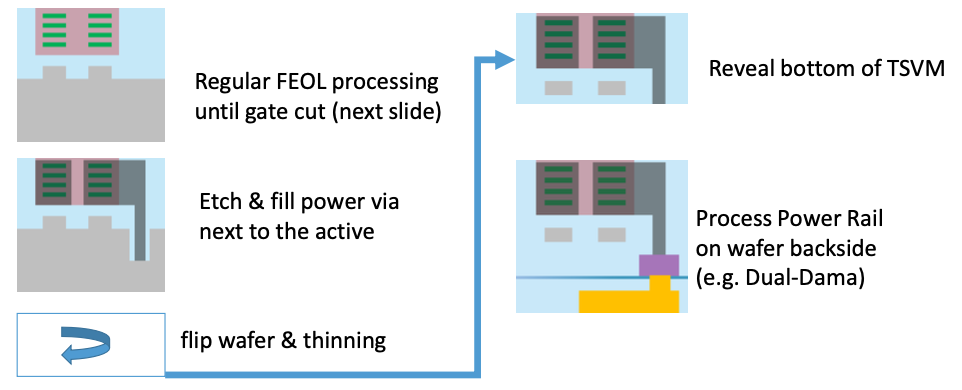

TSV-middle 电源位于有源旁边,并在单元之间共享。BSM1(背面金属 1)与有源对准。

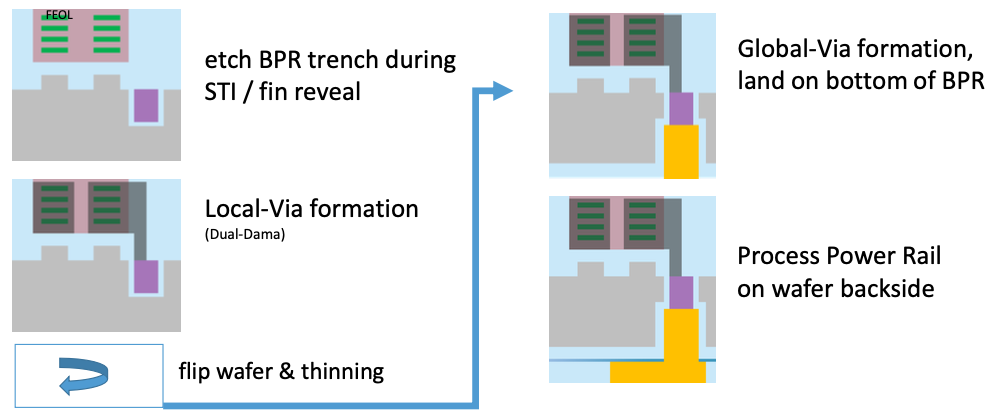

埋入式电源轨 (BPR) 的电源埋在有源器件,VBPR 接入 BPR,BPR 充当 BSM1(因此,有一层“背面”配电网络实际上移到了正面)。

背面接触电源位于有源下方,过孔接入电源轨,BSM1 与栅极对准

这三种方法具有一些共同的挑战——

01

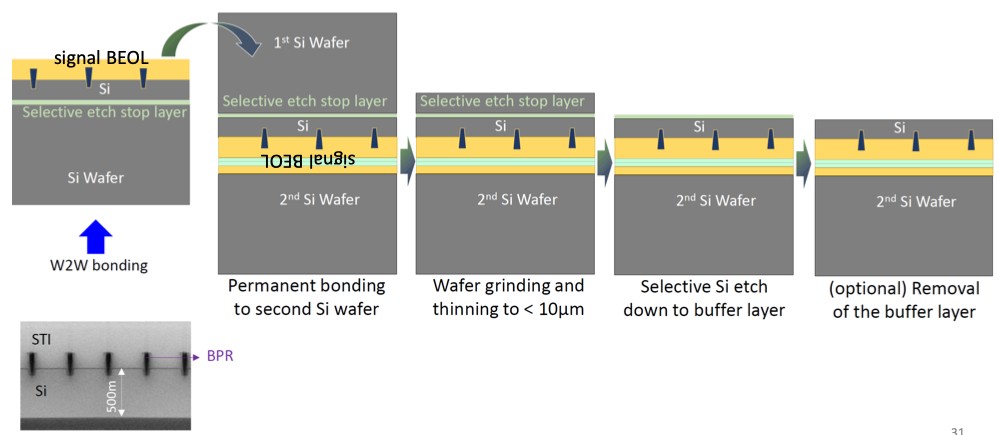

背面配电需要将硅晶圆减薄至小于 10um。

在真正的晶圆被削磨之前,需要将另一个晶圆粘合到真正的晶圆上(用于提供机械支撑和便于操作),如下图所示:

02

将正面和背面对准。

nano-TSV (nTSV) 需要在约 10nm 内对准。

上图是 TSV-middle 的高级流程;下图是BPR(埋入式电源轨)的高级流程。

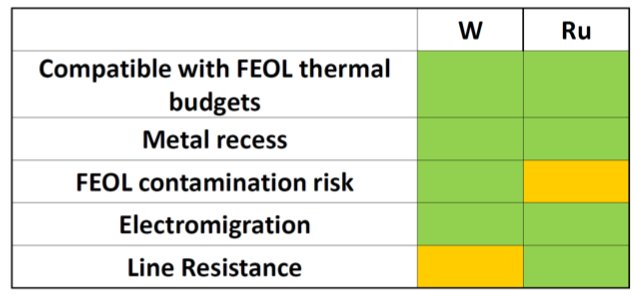

BPR 有两种候选材料:钨 (W) 和钌 (Ru)。钨的污染风险较低,可达到 50Ω/um 的目标电阻;但是钌不需要使用阻挡层,过孔电阻较低。

在此本文不会过多讨论背面接触方法,因为它似乎离实用还有很长的路要走。Gaspard 对 BS-PDN 的总结如下:

超级紧凑(优点)

有许多未解决的挑战(缺点)

背面和正面对准

Rseries

补充 FEOL 缩放

改善压降(优点)

展望未来

演讲的最后一部分对未来的技术发展进行了展望。

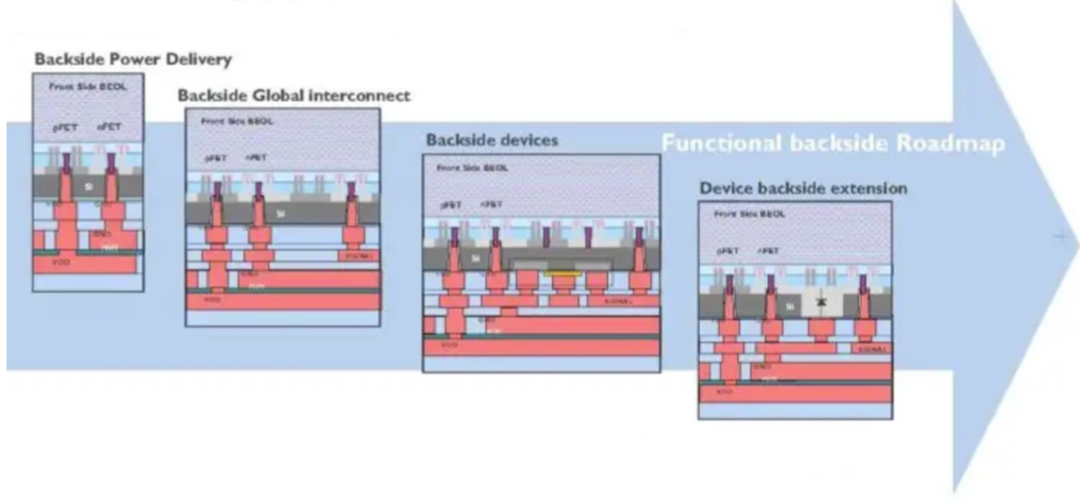

听到“背面配电”,不由得让人联想是否可以再进一步,增强背面的功能,然后将一些系统功能也移到背面。首先是全局互联(不需要在背面摆放器件)。但也有可能出现背面器件。

另一点是在背面创建金属-绝缘体-金属电容器 MIMCAP。鉴于可能涉及较大的功率密度 (1w/mm2),MIMCAP 有助于减少动态压降。

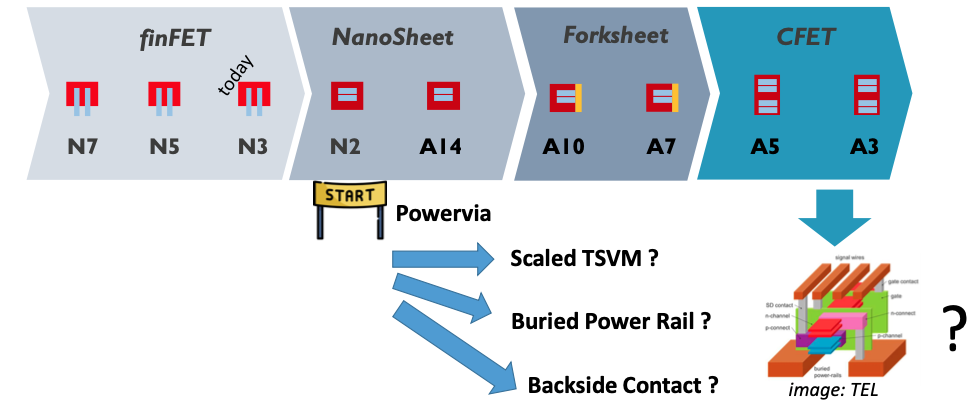

显而易见的是,背面配电技术将继续完善,一如下方逻辑器件路线图。

-

器件

+关注

关注

4文章

312浏览量

27874 -

Layou

+关注

关注

0文章

3浏览量

6800

发布评论请先 登录

相关推荐

碳化硅SiC在电子器件中的应用

功率电子器件控制电路的设计和功能

水井用安全电压操作柱是否可行

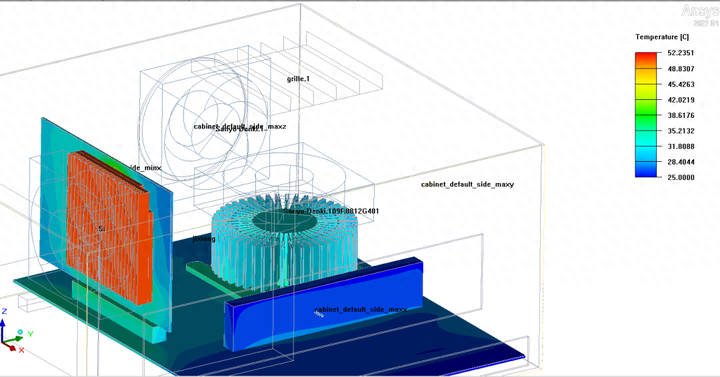

高功率电子器件的散热方案

电压驱动的电力电子器件的种类、工作原理及应用领域

电流驱动型电子器件的基本概念、工作原理及分类

电压驱动型电力电子器件的优点

电压驱动的电力电子器件有哪些

芯片电子器件焊点保护用什么胶水

行业资讯 I 国际电子器件大会:背面配电是否可行?

行业资讯 I 国际电子器件大会:背面配电是否可行?

评论