ESD(Electrostatic Discharge)测试,即静电放电测试,是所有电子设备必须要通过的测试,其目的是仿真操作人员或物体在接触设备时产生的放电以及人或物体对邻近物体之放电,以检测被测设备抵抗静电放电之干扰能力。

比较通用的一个测试标准是国际电工委员会(IEC)于1995年制定的 IEC 61000-4-2。

IEC 61000-4-2定义,ESD分为直接放电和间接放电。

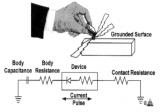

直接放电,即利用放电点击直接对受试设备实施放电,其中又分为接触放电(Contact Discharge)和空气放电(Air Discharge)。

间接放电,即对受试设备附近的耦合板实施放电,以模拟人体对受试设备附近的物体的放电。

淘晶驰电子生产的串口屏通过ESD测试IEC 61000-4-2:2001的标准。有更高需求的客户也可定制更高标准。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ESD

+关注

关注

49文章

2031浏览量

172990 -

串口屏

+关注

关注

8文章

534浏览量

37433

发布评论请先 登录

相关推荐

集成电路电磁兼容性及应对措施相关分析(三)集成电路ESD 测试与分析

测量对于确定IC的EMC特性是必要的。只有准确了解IC的EMC特性,才能在生产前采取有效的预防措施,提高产品的抗ESD能力和EMC性能,避免后期因ESD干扰导致的产品故障和成本增加等问题集成电路ESD

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析

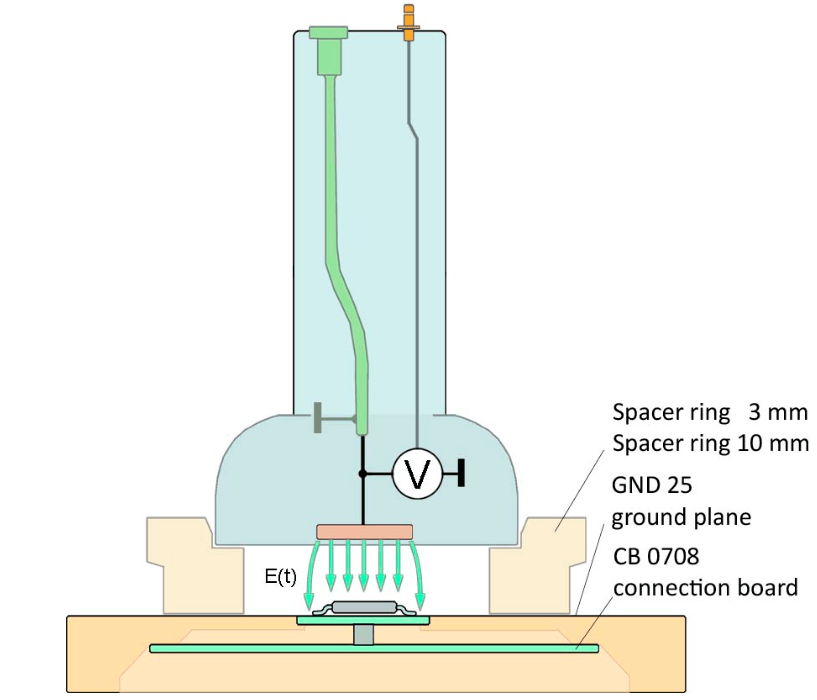

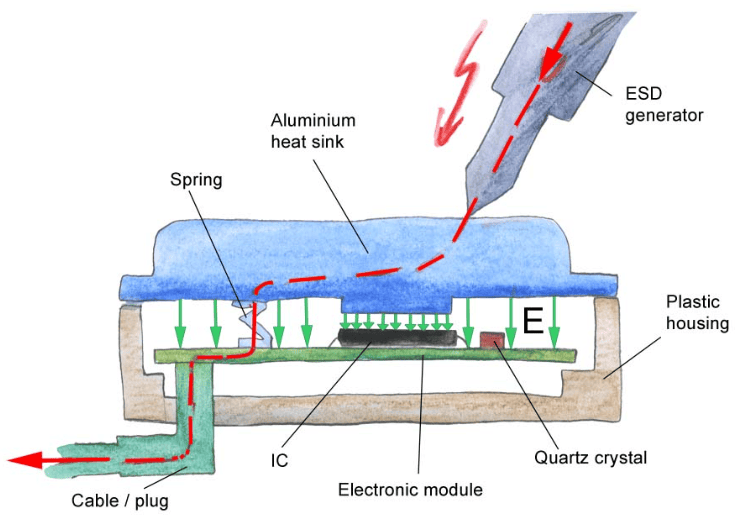

和成本增加等问题 。 三、集成电路ESD 测试与分析 1、测试环境与电场产生 图5 使用 ESD 发生器的测量设置l 测试环境,集成电路(I

集成电路电磁兼容性及应对措施相关分析(一) 电子系统性能要求与ESD问题

此专题将从三个方面来分享:一、电子系统性能要求与ESD问题二、集成电路ESD问题应对措施三、集成电路ESD测试与分析工业、消费及汽车电子模块开发的EMC问题会导致极高的开发成本和时间浪

ESD测试模式简介

在电子领域,有一个常常被忽视却又可能带来巨大危害的“隐形杀手”——ESD(Electrostatic Discharge,静电放电)。静电放电产生的瞬时高电压和大电流可能会直接损坏电子元件,使其失去

集成电路电磁兼容性及应对措施相关分析(一) — 电子系统性能要求与ESD问题

此专题将从三个方面来分享: 一、电子系统性能要求与ESD问题 二、集成电路ESD问题应对措施 三、集成电路ESD 测试与分析 工业、消费及汽车电子模块开发的 EMC 问题会导致极高的开

ESD器件的测试方法和标准

静电放电(ESD)是指由于静电积累而产生的电荷突然释放现象。在电子制造和使用过程中,ESD可能会导致器件损坏、性能下降甚至系统故障。 ESD测试的重要性 保护电子设备 :通过

ESD测试仪器的使用方法

在现代电子制造领域,静电放电(ESD)是一个不可忽视的问题。ESD可能导致设备性能下降、数据丢失甚至设备损坏。因此,对电子设备进行ESD测试是确保其在实际使用中能够抵抗静电干扰的重要环

ESD测试是什么?CW32能扛8000V?

ESD测试,即静电放电测试(Electrostatic Discharge Testing),是一种用于评估电子设备或组件在静电放电环境下的性能稳定性和可靠性的测试方法。以下是关于

求助,关于LM393B输入电压问题求解

(0.32V-0.24V);

请问:一般来说这两Pin的电压差多少合适 以及 这么小的电压差会不会存在什么异常(比如ESD测试时导致其输出截然相反);

发表于 07-31 08:17

运算放大器:4 kV HBM ESD TOLERANCE是什么意思

放电的模型。4 kV HBM ESD容差意味着该器件在模拟人体模型静电放电测试中能够承受最高4千伏的静电放电,而不会损坏或失效。 具体解释 HBM(Human Body Model):HBM是一种

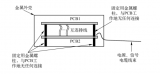

PCB工作地与金属外壳连接对ESD干扰影响的实例分析

图中有两条ESD共模干扰路径,即图中左边ICM1所在路径和右边ICM2路径。

很明显,第二条干扰路径才是ESD测试不通过的主要原因。

发表于 03-05 10:28

•2320次阅读

电磁兼容测试是干啥的 影响emc测试的因素有哪些

ESD测试用于检验设备对静电放电的抵抗能力,如人体静电放电或静电放电设备引起的放电。这项测试可以确保设备在实际使用时不会受到静电干扰的影响。

ESD测试是什么?

ESD测试是什么?

评论