多核的微控制器(MCU)向来是设计上的一大挑战,尤其是多核异构的设计。而MCU双核作为其中的精简版本,凭借其超强的处理性能和便捷开发的特性,很快受到业界的好评。先楫半导体先后推出了几款高性能MCU双核产品,集成 2 个 RISC-V 处理器,其中HPM6700系列两个核的最高主频都可以达到816MHz。本文通过对先楫HPM6000系列双核的使用方法、工程编译与调试、双核通信方式和资源分配等内容的介绍,全方位给大家介绍双核的使用和操作,让大家轻松玩转双核,完成更多的片上系统功能开发。

接下来,让我们看一看HPM6000系列双核MCU是如何玩转起来的吧~

双核简介

Introduction

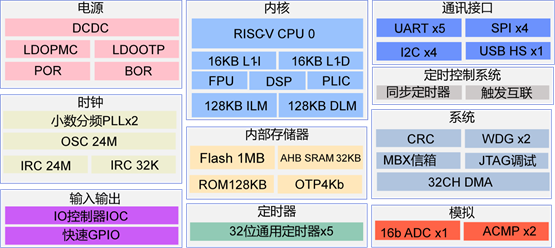

HPM6000系列的双核配置,均集成 2 个 RISC-V 处理器,双核采用主从结构。CPU0 和 CPU1 采用相同配置,如下:

● 支持相同指令集

● 相同容量的 L1 指令和数据缓存

– 32KB L1 I-Cache,4-way,128x 64B cache line per way

– 32KB L1 D-cache,4-way,128x 64B cache line per way

● 相同容量的指令和数据本地存储器:256 KB ILM 和 256 KB DLM

CPU0 和 CPU1 采用相同的存储器映射,以下为例外:

● CPU 自身的指令/数据本地存储器 ILM / DLM 为私有;

● FGPIO 为私有

● 软件中断控制器 PLICSW 为私有

● 机器定时器 MCHTMR 为私有

双核的三种使用方法推荐

Recommendation

不论是在RAM中运行,还是片上Flash运行,双核固件均是存储在Flash上。客户根据应用场景,选择在上电后将双核各自的镜像从Flash中装载到RAM中执行或者基于Flash片上执行。

根据应用场景,选择合适的运行方式,推荐以下几种:

方案一:Core0 加载到RAM运行,Core1加载到RAM运行

RAM区域可以是各自的ILM,也可以片上的SRAM,或者是SDRAM。当然,装载CODE的RAM区域各自都是独立的。此方案应用与双核固件均占用小,可完全装载到RAM中运行。

固件存储位置:Core0和Core1的固件均存放在Flash指定区域(Flash分区规划)。上电后,BootRom 从指定Flash区域装载Core0镜像到指定RAM运行(type:debug/release),Core0运行后从指定Flash 区域装载Core1镜像到指定RAM,然后运行Core1。

方案二:Core0基于flash xip(flash片上执行)运行,Core1加载到RAM运行

此方案应用与Core0核固件占用大, Core1核固件占用小。通常将Core0用来做应用复杂交互,Core1用来做高实时性,高性能的触发逻辑。

固件存储位置:

1). Core0和Core1的固件各自存放在Flash的指定区域(Flash分区规划)。

优点:Core0和Core1可单独OTA。

缺点:需要维护两个固件BIN文件,并存放到各自的区域中。

2). Core1的固件以数组(只读区)镜像的方式存储在Core0的固件中,Core0固件存放在Flash指定区域;官方例程中使用此方案。

优点: 只维护一个固件。

缺点:Core0和Core1不可单独OTA。

方案三:Core0基于flash xip0(flash片上执行)运行,Core1基于flash xip1(flash 片上执行)运行

此方案应用与Core0核和Core1核固件均很大,双核均无法满足放到RAM中运行。

注意:由于双核均基于flash片上执行,如果使用同一个flash XPI,会出现并发访问Flash的情况导致未知异常发生;如果强制顺序访问,访问效率极低,严重拖垮CPU运行速率;故不建议两个核使用同一个flash XPI片上执行。建议使用XPI0和XPI1各自外挂一个FLASH,分别用于Core0 Flash xip0和Core1 Flash xip1。

固件存储位置:Core0和Core1的固件存储在各自外挂的Flash的指定区域中。

双核工程编译与调试

Compilation and Debugging

HPM双核是集成了两个RISC-V 处理器,是两个完全独立的CPU,故HPM双核工程是Core0工程和Core1工程两个独立的工程。因此HPM双核工程编译,其实是两个独立的单核工程的编译。用户只需要建立core0和core1的各自工程编译调试即可。

由于HPM-SDK例程中使用的是方案二,且Core1的固件以数组(只读区)镜像的方式存储在Core0的固件中,导致Core1工程为Core0工程的关联工程。因此在构建工程时,必须先构建生成Core0工程,作为关联工程Core1工程会自动生成。由于Core1的固件是Core0工程中的只读数组,故必须先编译Core1工程生成只读数组镜像后,再编译Core0工程。

如下构建编译调试双核hello world工程:

A. 构建工程

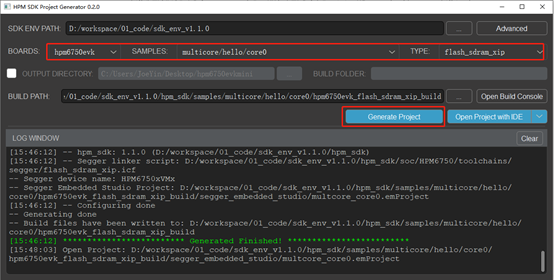

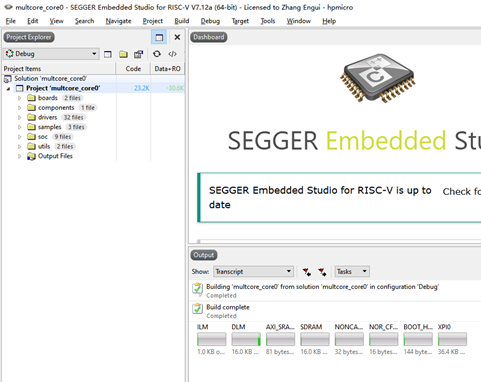

先构建生成Core0工程:

由于Core0是flash片上执行,故type选择:flash_sdram_xip或flash_xip

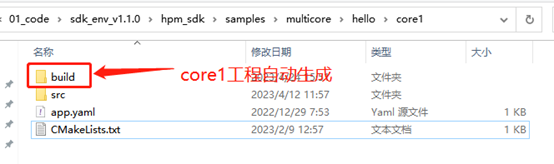

作为关联工程Core1工程会自动生成:

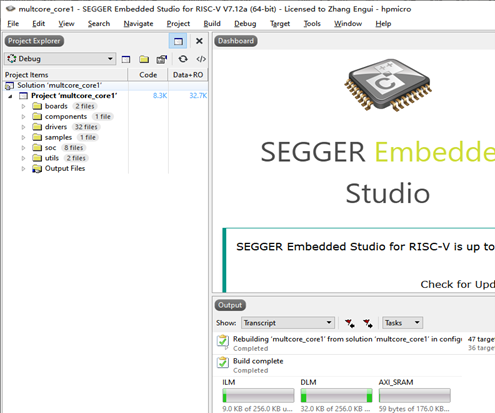

B. 编译工程

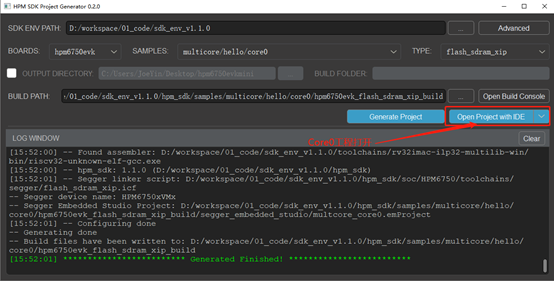

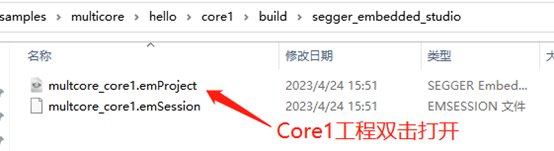

打开各自的工程(Core0通过GUI工具直接点击Open Project with IDE, Core1对应目录下双击打开工程)。

用SES编译各自的工程即可。

C. 工程调试

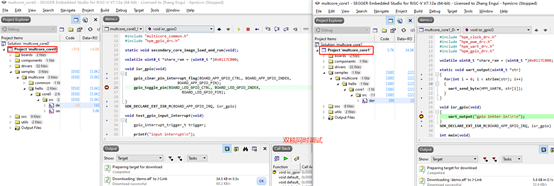

一、双核同时调试

基于OpenOCD调试(FT2232/DAP-LINK等)。

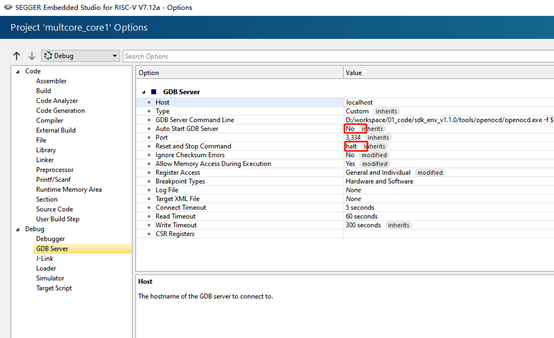

为了达到Core0和Core1同时调试,基于OpenOCD调试在HPM-SDK例程中,对Core1的Debug做了如下限制:

1)Core1不启动GDB Server,连接Core0启动的GDB Server。当然使用不同的port来区分是Core0(Port:3333)还是Core1(Port:3334)。

2)Reset 和 Stop时,直接hart停止运行。

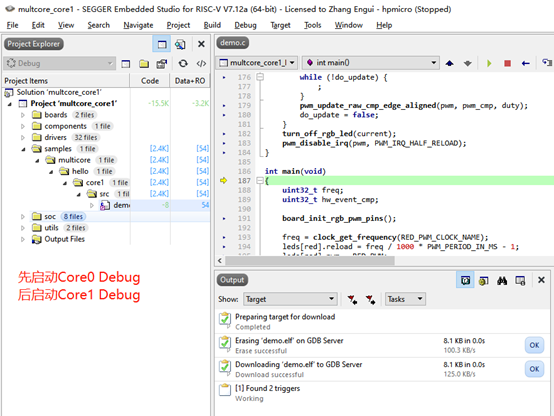

如下图:

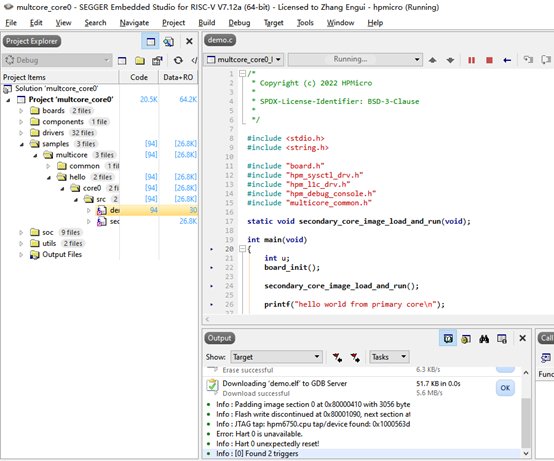

因此,调试HPM-SDK双核例程,步骤如下:

步骤1:Core0的工程调试,和正常的单核调试相同,正常SES启动debug即可。

步骤2:Core1的工程调试,由于上述限制(为了双核同时调试),必须先将Core0的工程Debug运行,然后在启动Core1的Debug仿真。

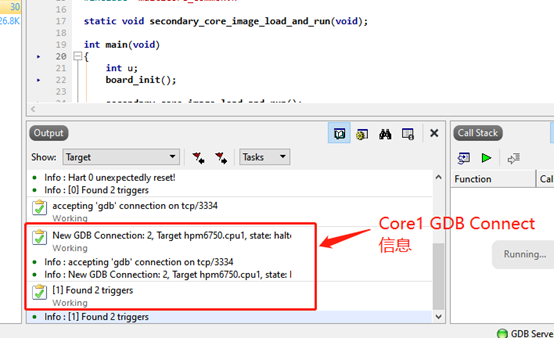

可在Core0 SES终端看到Core1 GDB connect信息:

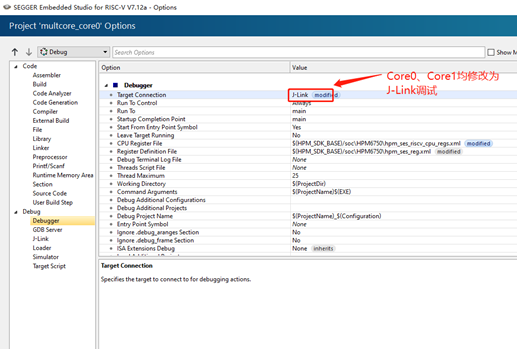

基于Jlink 调试

基于Jlink调试,对Core0和Core1的Debug做如下修改:

1. Core0 修改Debug连接target为:J-Link

2. Core1修改Debug连接target为:J-Link

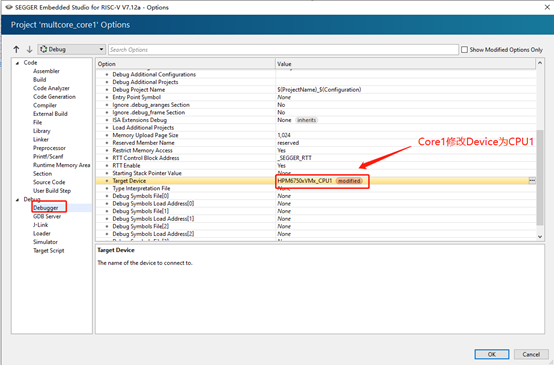

3. Core1修改Debug Device为:HPM6750xVMx_CPU1

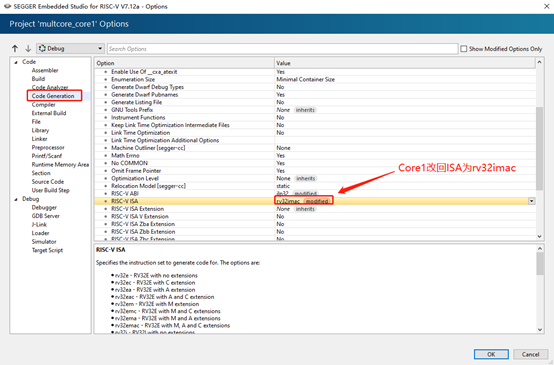

4. 由于SES修改Device为CPU1(上一步骤修改),联动修改ISA为:rv32i,导致编译等异常。故在Code Generation下改回ISA为:rv32imac。

5. 通常初始化时钟等外设在Core0中完成,故为了双核能同时调试,需先运行Core0 Debug至完成时钟等外设初始化后,方可Core1 Debug运行。

二、双核单独调试

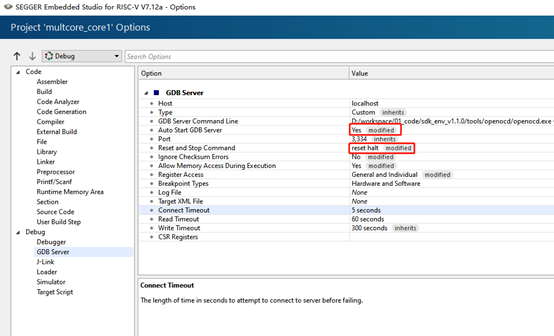

基于 OpenOCD 调试

如果只用来单独调试Core1(Core0的单独调试不做任何修改即可),可修改Core1的Debug配置,如下:

Auto Start GDB Server: Yes

Reset and Stop Command: reset halt

修改后, 可直接启动Core1 Debug运行。

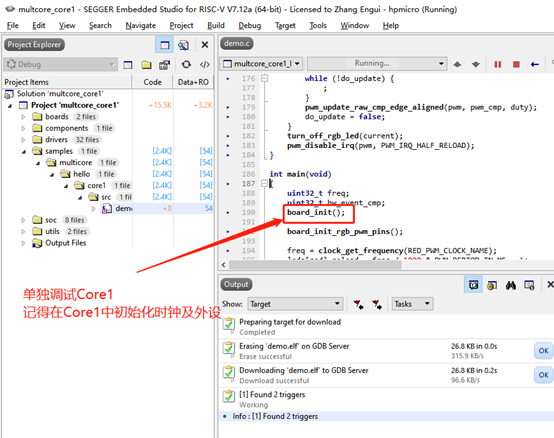

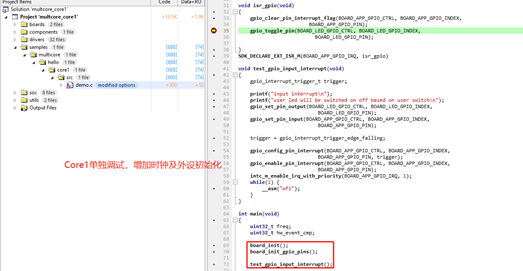

注意:由于CPU0,CPU1主从架构,通常外设等时钟初始化会在Core0中完成。如果是单独调试Core1,为了确保程序能正常运行,需在Core1工程中初始化时钟等外设。如下:

基于 Jlink 调试

单独调试Core1 (Core0的单独调试不做任何修改即可),JLink修改同双核JLink修改一致(可参考上方介绍的内容)。

同样为了确保Core1能正常运行,需在Core1工程中初始化时钟等外设。

下一篇,我们将会给各位小伙伴们介绍双核的通信方式、资源分配和双核应用eRPC架构,敬请期待。

-

mcu

+关注

关注

146文章

16848浏览量

349791 -

先楫半导体

+关注

关注

10文章

214浏览量

2048

发布评论请先 登录

相关推荐

先楫HPM6E00技术日 | 百人研讨共话工业应用创新及发展趋势

有奖提问!先楫半导体HPM6E00系列新品发布会!!

先楫高性能MCU HPM6800系列产品生态绽放,共链未来

芯原2.5D GPU IP赋能先楫半导体HPM6800系列RISC-V MCU

【先楫HPM5361EVK开发板试用体验】先楫HPM5361EVK开发板初体验

【先楫HPM5361EVK开发板试用体验】认识和了解先楫HPM5361EVK开发板

先楫半导体发布多个系列高性能微控制器产品

文档上新|HPM16 位 ADC+ENET 开发案例

2分钱/MHz!轻松入手先楫高性能MCU——HPM5301打破芯纪录

2分钱/MHz!轻松入手先楫高性能MCU——HPM5301打破芯纪录

玩转MCU双核(上) 先楫HPM6000系列双核怎么玩?答案超乎你想象!

玩转MCU双核(上) 先楫HPM6000系列双核怎么玩?答案超乎你想象!

评论