在验证过程中让DUT进入特定场景只是验证的重要部分之一,验证环境还应该检查来自DUT的输出响应。可以使用两种类型的自动检查机制:

断言--源于规范或设计实现,确保正确的时序行为。断言通常侧重于信号级。可重用的断言也是可重用验证组件的一部分,当然设计也可以将断言放在DUT RTL中。

数据检查器-确保DUT整体的正确性。

Scoreboards

self-checking验证环境的一个重要部分是Scoreboards。通常情况下,Scoreboards在功能层面上验证设计的正确操作。Scoreboards承担的责任因实现方式而异。下面展示一个Scoreboards的例子,它验证了一个UBus slave interface。

UBus Scoreboard 示例

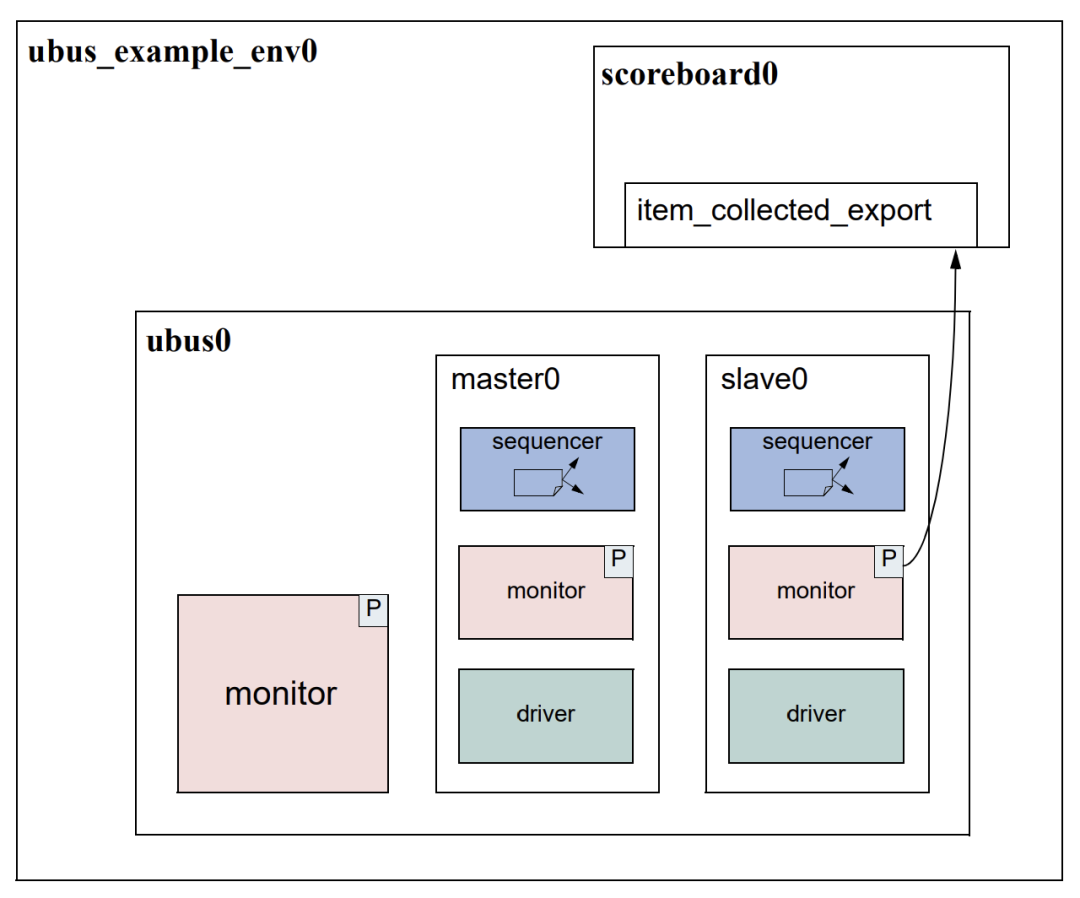

写到一个地址的数据应该在读取该地址时返回,验证环境的拓扑结构如下图所示:

在这个例子中,创建了一个top-level environment,其中有一个UBus environment,包含bus monitor,一个master agent,和一个slave agent。

定义Scoreboard:

添加必要的TLM export,以便与monitor进行通信。

执行TLM export的方法,定义export被调用时的行为。

向uvm_scoreboard添加Exports :

在上图的例子中,monitors提供了一个TLM uvm_analysis_port(s)接口, scoreboard需要提供TLM uvm_analysis_imp。

1 classubus_example_scoreboardextendsuvm_scoreboard; 2 uvm_analysis_imp#(ubus_transfer,ubus_example_scoreboard) 3 item_collected_export; 4 ... 5 function new (string name, uvm_component parent); 6 super.new(name, parent); 7 endfunction : new 8 function void build_phase(uvm_phase phase); 9 item_collected_export = new("item_collected_export", this); 10 endfunction 11 ...

第2行声明了uvm_analysis_export。第一个参数ubus_transfer,定义了通过这个TLM接口通信的uvm_object。第二个参数定义了父类类型。

第9行创建item_collected_export实例。

由于scoreboard提供了一个 uvm_analysis_imp,scoreboard必须实现该export所要求的所有方法。这意味着需要定义write virtual function的实现:

virtual function void write(ubus_transfer trans); if (!disable_scoreboard) memory_verify(trans); endfunction : write

write()的实现定义了在这个接口上接收到数据时的行为。如果disable_scoreboard为0,就会以transaction为参数调用memory_verify()函数。

将Scoreboard添加到Environment中

一旦定义好scoreboard,就可以添加到UBus的 top-level environment中。首先,在ubus_example_env类中声明ubus_example_scoreboard。

ubus_example_scoreboard scoreboard0;

scoreboard可以在build() phase构建:

function ubus_example_env::build_phase(uvm_phase phase);

...

scoreboard0 = ubus_example_scoreboard::create("scoreboard0",

this);

...

endfunction

在UBus environment中连接slaves[0] monitor到scoreboard的export上。

function ubus_example_env::connect_phase(uvm_phase phase); ... ubus0.slaves[0].monitor.item_collected_port.connect( scoreboard0.item_collected_export); ... endfunction

总结下,添加scoreboard的过程:

声明scoreboard组件

添加必要的exports。

实现所需的方法来执行特定的功能。

将scoreboard添加到environment中

声明并实例化scoreboard组件。

连接TLM port

审核编辑:刘清

-

RTL

+关注

关注

1文章

386浏览量

60146 -

UVM

+关注

关注

0文章

182浏览量

19272 -

TLM

+关注

关注

1文章

33浏览量

24811 -

DUT

+关注

关注

0文章

190浏览量

12573

原文标题:uvm中的Scoreboards

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

数字IC验证之“典型的UVM平台结构”(3)连载中...

什么是uvm?uvm的特点有哪些呢

如何构建UVM寄存器模型并将寄存器模型集成到验证环境中

谈谈UVM中的uvm_info打印

UVM中seq.start()和default_sequence执行顺序

数字IC验证之“典型的UVM平台结构”(3)连载中...

UVM中uvm_config_db机制背后的大功臣

如何用Verdi查看UVM环境中的变量?

uvm中的Scoreboards介绍

uvm中的Scoreboards介绍

评论