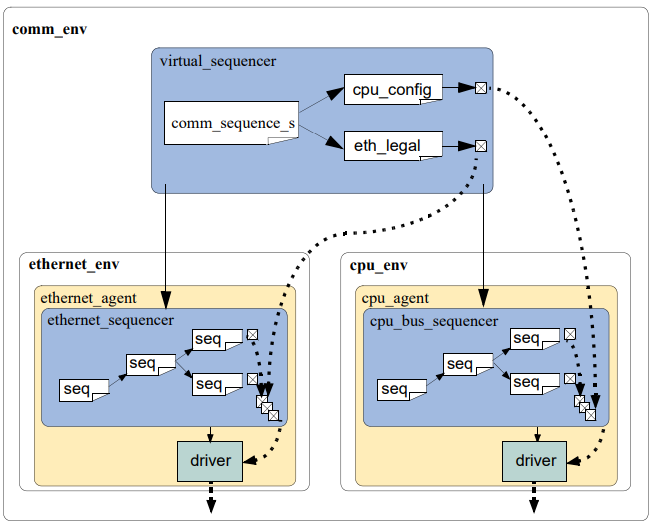

在一个系统级的验证环境中,多个验证组件并行地产生激励。测试用例开发者可能希望协调多个通道激励之间的时序和数据。

Virtual sequences与virtual sequencer相关联,用于协调测试平台中的激励生成。一般来说,一个virtual sequencer包含对其子sequencer的引用,即driver sequencers或其他virtual sequencers。

Virtual sequences可以调用其他virtual sequences,以及每个子sequencer中的sequences(driversequences)。

在下图中,virtual sequencer在ethernet和cpu验证组件上调用配置sequences。这些配置sequences是在模块级测试期间开发的,可以在系统级测试时复用。

有三种方式可以让virtual sequencer与它的subsequencers交互:

Virtual sequencers和subsequencers同时发送激励。

禁用subsequencers。Virtualsequencers是唯一的驱动。

使用grab()和ungrab()--Virtualsequencers在有限的时间内控制激励发送。

当使用virtual sequences时,大多数测试用例开发用户都会只从virtual sequences中调用sequences。要调用sequences,需要执行以下操作之一:

使用'uvm_do宏 。

使用sequence start()方法。

创建一个Virtual Sequencer

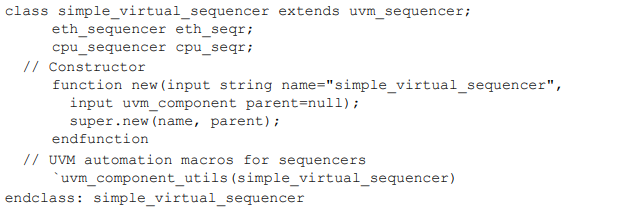

为了从一个sequencer中对多个sequencers进行控制,可以使用一个不附属于driver的sequencer,这就是virtual sequencer。要创建一个virtual sequencer,需要:

从uvm_sequencer类派生出一个virtual sequencer类。

在virtual sequencer中添加对其他subsequencer的指针(在更高层次的验证组件(通常是top-level environment)中)。

下面的例子声明了一个有两个subsequencers的virtual sequencer。

Subsequencers可以是driver sequencers或其他virtual sequencers。

创建一个Virtual Sequence

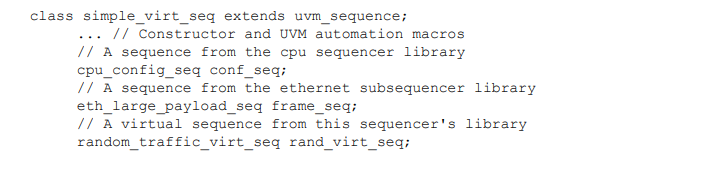

要创建一个virtual sequence:

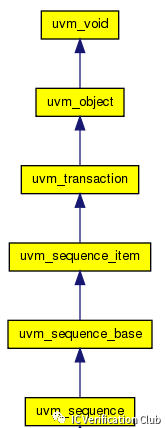

从uvm_sequence派生出一个sequence类。

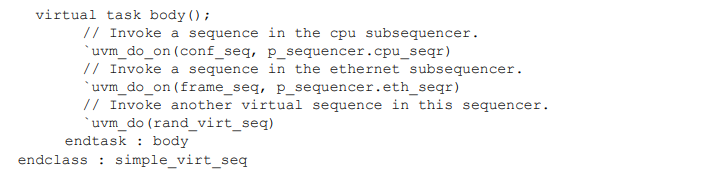

定义一个body()方法。

使用`uvm_ do_on(或` uvm_do_on_with)宏来调用subsequencers的sequences。

使用`uvm_do(或`uvm_do_with)宏来调用当前virtual sequencer中的其他virtual sequences。

一个virtual sequence不能使用`uvm_do或`uvm_do_with来执行数据项的发送,只能执行sequences。

下面的例子显示了一个简单的virtual sequence控制两个subsequencers:cpu sequencer和ethernet sequencer。假设cpu sequencer有 一 个 cpu_config_seq sequence,ethernet sequencer有一个 eth_large_payload_seq序列。

控制其他Sequencers

当使用virtual sequencer时,需要考虑subsequencers和virtualsequence之间的关系。有三种典型的可能性:

virtual sequencer和subsequencers同时产生激励。subsequencers产生的数据项和virtual sequencer产生的数据项被混合在一起,并由driver以任意顺序执行。

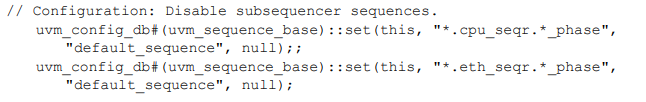

禁用subsequencers。使用uvm_config_db::set将subsequencers的default_sequence属性设置为null。

使用grab()/lock()和ungrab()/unlock()。在这种情况下,一个virtual sequence可以在有限的时间内实现对其subsequencers的完全控制,然后让原始sequences继续工作。grab和lock防止其他sequence在被锁定的sequencer上被执行。

grab()方法将lock request放在sequencer仲裁队列的头部,允许调用者阻止当前等待授予的数据项被处理,而lock()方法将lock request放在队列的末端,允许数据项在授予lock之前被处理。

将Virtual Sequencer连接到Subsequencers上

要连接一个virtual sequencer和它的subsequencers,需要在验证环境的connect()phase将sequencer的实例赋值给virtual sequencer中指定的sequencer指针。

v_sequencer.cpu_seqr = cpu_seqr; v_sequencer.eth_seqr = eth_seqr;

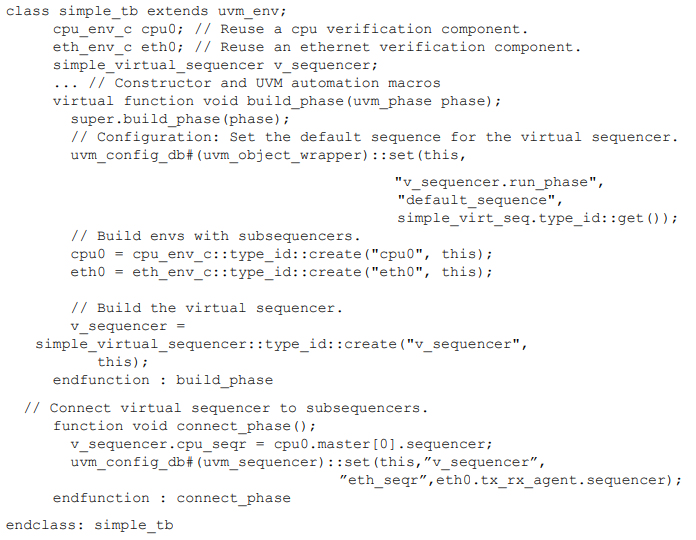

下面这个例子显示了一个top-level environment,它实例化了ethernet和cpu验证组件以及控制这两个组件的virtual sequencer。

在top-level environment中,各个组件内部的sequencers的路径是已知的,可以根据该路径将sequencers连接到virtual sequencer上。

审核编辑:刘清

-

连接器

+关注

关注

98文章

14488浏览量

136443 -

UVM

+关注

关注

0文章

182浏览量

19167 -

sequence

+关注

关注

0文章

23浏览量

2840

原文标题:UVM中的Virtual Sequences

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IC验证"UVM验证平台加入factory机制"(六)

IC验证“UVM验证平台加入objection机制和virtual interface机制“(七)

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

什么是uvm?uvm的特点有哪些呢

UVM sequence分层有哪几种方式呢

请问一下在UVM中的UVMsequences是什么意思啊

谈谈UVM中的uvm_info打印

virtual sequence和virtual sequencer的操作步骤

为什么需要使用virtual,不用可不可以?

UVM中uvm_config_db机制背后的大功臣

UVM中uvm_config_db机制背后的大功臣

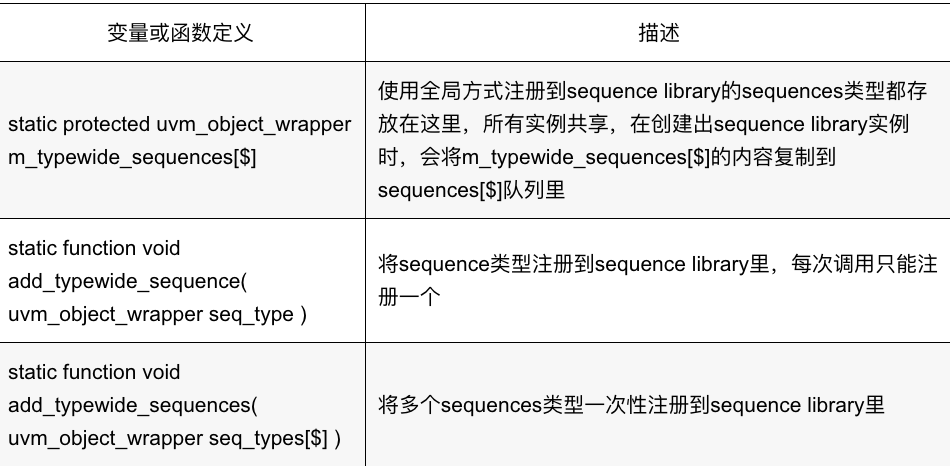

如何将sequences类型添加或注册到sequence library里呢?

浅析UVM中的Virtual Sequences

浅析UVM中的Virtual Sequences

评论