在干法蚀刻中,气体受高频(主要为 13.56 MHz 或 2.45 GHz)激发。在 1 到 100 Pa 的压力下,其平均自由程为几毫米到几厘米。

主要有三种类型的干法蚀刻:

• 物理干法蚀刻:加速粒子对晶圆表面的物理磨损

• 化学干法蚀刻:气体与晶圆表面发生化学反应

• 化学物理干法蚀刻:具有化学特性的物理蚀刻工艺

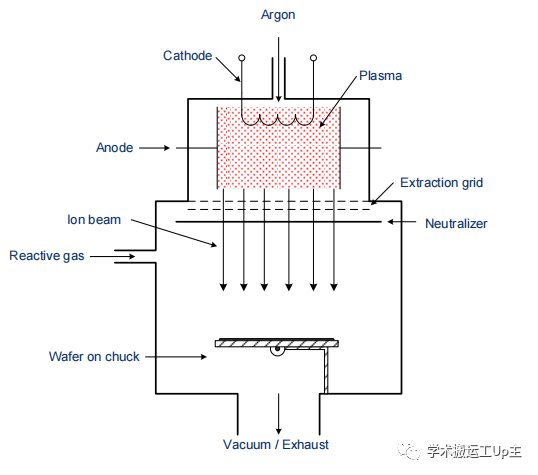

1.离子束蚀刻

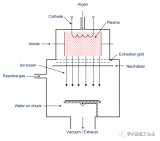

离子束蚀刻 (Ion beam etch) 是一种物理干法蚀刻工艺。由此,氩离子以约1至3keV的离子束辐射到表面上。由于离子的能量,它们会撞击表面的材料。晶圆垂直或倾斜入离子束,蚀刻过程是绝对各向异性的。选择性低,因为其对各个层没有差异。气体和被打磨出的材料被真空泵排出,但是,由于反应产物不是气态的,颗粒会沉积在晶片或室壁上。

为避免颗粒,将第二种气体引入腔室。该气体与氩离子发生反应并引起物理化学蚀刻过程。部分气体与表面反应,但也与打磨出的颗粒反应形成气态副产物。几乎所有材料都可以用这种方法蚀刻。由于垂直辐射,垂直壁上的磨损非常低(高各向异性)。然而,由于低选择性和低蚀刻速率,该工艺在当今的半导体制造中很少使用。

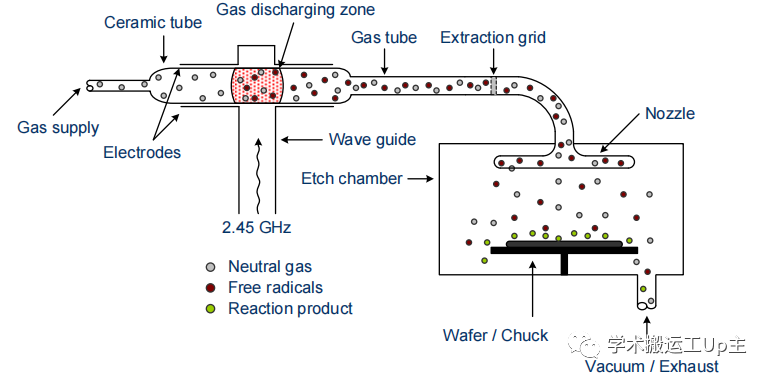

2.等离子刻蚀

等离子刻蚀(Plasma etch)是一种绝对化学刻蚀工艺(化学干法刻蚀,Chemical dry etch)。优点是晶圆表面不会被加速离子损坏。由于蚀刻气体的可移动颗粒,蚀刻轮廓是各向同性的,因此该方法用于去除整个膜层(如热氧化后的背面清洁)。

一种用于等离子体蚀刻的反应器类型是下游反应器。从而通过碰撞电离在2.45GHz的高频下点燃等离子体,碰撞电离的位置与晶片分离。

在气体放电区域,由于冲击存在各种颗粒,其中有自由基。自由基是具有不饱和电子的中性原子或分子,因此非常活泼。作为中性气体,例如四氟甲烷CF4被引入气体放电区并分离成CF2和氟分子F2。类似地,氟可以通过添加氧气 O2 从 CF4 中分离出来:

2 CF4 + O2 --->2 COF2 + 2 F2

氟分子可以通过气体放电区的能量分裂成两个单独的氟原子:每个氟原子都是一个氟自由基,因为每个原子都有七个价电子,并希望实现惰性气体构型。除了中性自由基之外,还有几个部分带电的粒子(CF+4、CF+3、CF+2、...)。然后,所有粒子、自由基等都通过陶瓷管进入蚀刻室。带电粒子可以通过提取光栅从蚀刻室中阻挡或者在它们形成中性分子的途中重新组合。氟自由基也有部分重组,但足以到达蚀刻室,在晶圆表面发生反应并引起化学磨损。其他中性粒子不是蚀刻过程的一部分,并且与反应产物一样被耗尽。

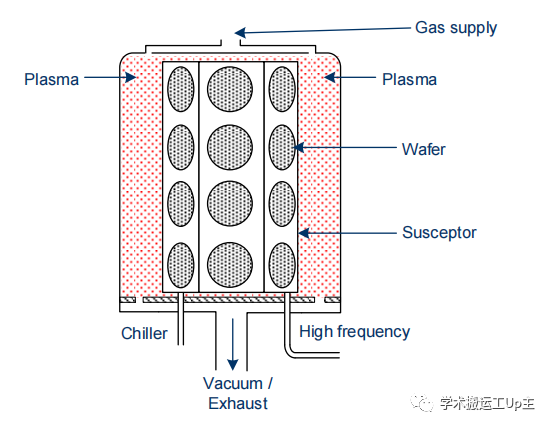

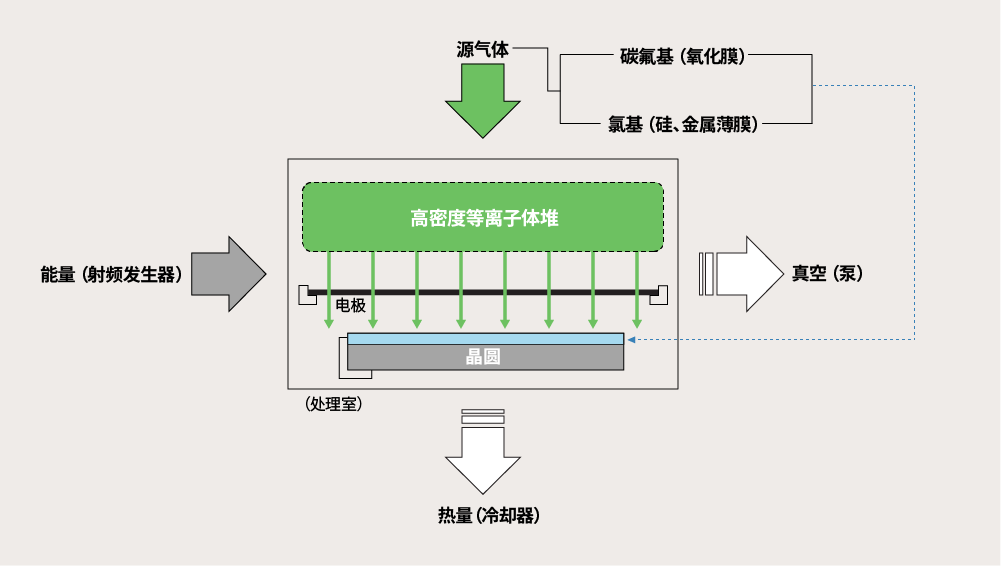

可在等离子蚀刻中蚀刻的薄膜示例: • 硅: Si + 4F---> SiF4 • 二氧化硅: SiO2 + 4F---> SiF4 + O2 • 氮化硅: Si3N4 + 12F---> 3SiF4 + 2N23.反应离子蚀刻蚀刻特性: 选择性、蚀刻轮廓、蚀刻速率、均匀性、可重复性 - 均可以在反应离子蚀刻 (Reactive ion etch) 中非常精确地控制。各向同性蚀刻轮廓以及各向异性是可能的。因此,RIE 工艺是一种化学物理蚀刻工艺,是半导体制造中用于构造各种薄膜的最重要工艺。 在工艺室内,晶圆放置在高频电极(HF电极)上。通过碰撞电离产生等离子体,其中出现自由电子和带正电的离子。如果 HF 电极处于正电压,则自由电子会在其上积聚,并且由于它们的电子亲和力而无法再次离开电极。因此,电极充电至 -1000 V(偏置电压)。不能跟随快速交变场的慢离子向带负电的电极移动。

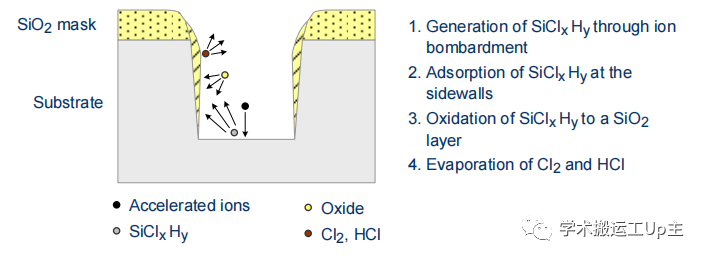

如果离子的平均自由程高,则粒子以几乎垂直的方向撞击晶片表面。因此,材料被加速离子(物理蚀刻)从表面击出,此外,一些粒子与表面发生化学反应。横向侧壁不受影响,因此没有磨损并且蚀刻轮廓保持各向异性。选择性不是太小,但是,由于物理蚀刻进程,它也不是太大。此外,晶圆表面会被加速离子损坏,必须通过热退火进行固化。 蚀刻工艺的化学部分是通过自由基与表面以及物理铣削材料的反应来完成的,这样它就不会像离子束蚀刻那样重新沉积到晶圆或腔室壁上。通过增加蚀刻室中的压力,颗粒的平均自由程减少。因此会有更多的碰撞,因此粒子会朝着不同的方向前进。这导致较少的定向蚀刻,蚀刻过程获得更多的化学特性。选择性增加,蚀刻轮廓更加各向同性。通过在硅蚀刻期间侧壁的钝化,实现了各向异性的蚀刻轮廓。因此,蚀刻室内的氧气与磨出的硅反应形成二氧化硅,二氧化硅沉积垂直侧壁。由于离子轰击,水平区域上的氧化膜被去除,使得横向的蚀刻进程继续进行。

蚀刻速率取决于压力、高频发生器的功率、工艺气体、实际气体流量和晶片温度。各向异性随着高频功率的增加、压力的降低和温度的降低而增加。蚀刻工艺的均匀性取决于气体、两个电极的距离以及电极的材料。如果距离太小,等离子体不能不均匀地分散,从而导致不均匀性。如果增加电极的距离,则蚀刻速率降低,因为等离子体分布在扩大的体积中。对于电极,碳已证明是首选材料。由于氟气和氯气也会攻击碳,因此电极会产生均匀的应变等离子体,因此晶圆边缘会受到与晶圆中心相同的影响。

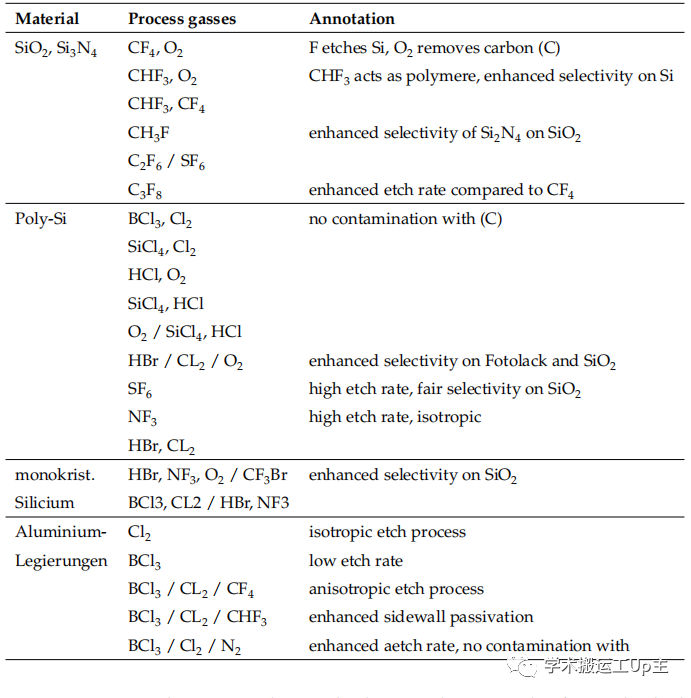

选择性和蚀刻速率在很大程度上取决于工艺气体。对于硅和硅化合物,主要使用氟气和氯气。

蚀刻工艺不限于一种气体、气体混合物或固定工艺参数。例如,可以首先以高蚀刻速率和低选择性去除多晶硅上的原生氧化物,而随后以相对于下方层的更高选择性蚀刻多晶硅。

-

半导体

+关注

关注

334文章

27442浏览量

219457 -

晶硅

+关注

关注

1文章

48浏览量

22705 -

刻蚀

+关注

关注

2文章

189浏览量

13127

发布评论请先 登录

相关推荐

半导体八大工艺之刻蚀工艺:干法刻蚀

释放MEMS机械结构的干法刻蚀技术

6英寸半导体工艺代工服务

【转帖】干法刻蚀的优点和过程

释放MEMS机械结构的干法刻蚀技术

两种基本的刻蚀工艺:干法刻蚀和湿法腐蚀

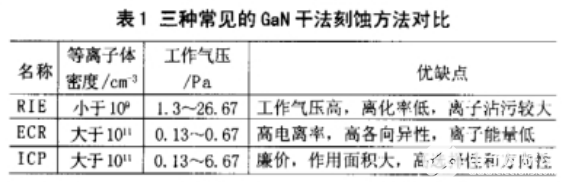

GaN材料干法刻蚀工艺在器件工艺中有着广泛的应用

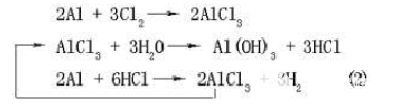

干法刻蚀之铝刻蚀的介绍,它的原理是怎样的

半导体八大工艺之刻蚀工艺-干法刻蚀

半导体八大工艺之刻蚀工艺-干法刻蚀

评论