本文的关键要点

・漏极和源极间的浪涌是由各种电感分量和MOSFET寄生电容的谐振引起的。

・在实际的版图设计中,很多情况下无法设计出可将线路电感降至最低的布局,此时,尽可能在开关器件的附近配备缓冲电路来降低线路电感,这是非常重要的。

首先,为您介绍SiC MOSFET功率转换电路中,发生在漏极和源极之间的浪涌。

·漏极和源极之间产生的浪涌

·缓冲电路的种类和选择

·C缓冲电路的设计

·RC缓冲电路的设计

·放电型RCD缓冲电路的设计

·非放电型RCD缓冲电路的设计

·封装引起的浪涌差异

SiC MOSFET的漏极

和源极之间产生的浪涌

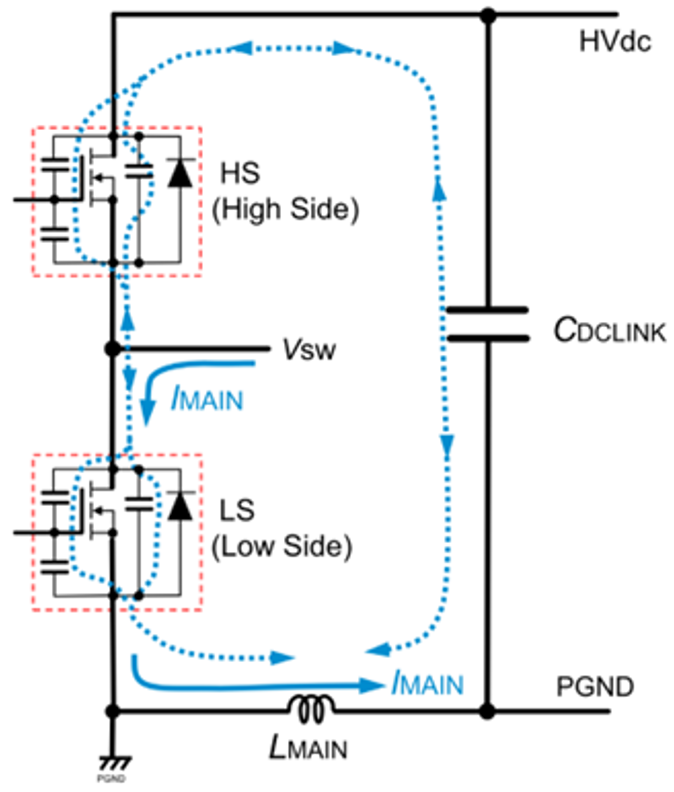

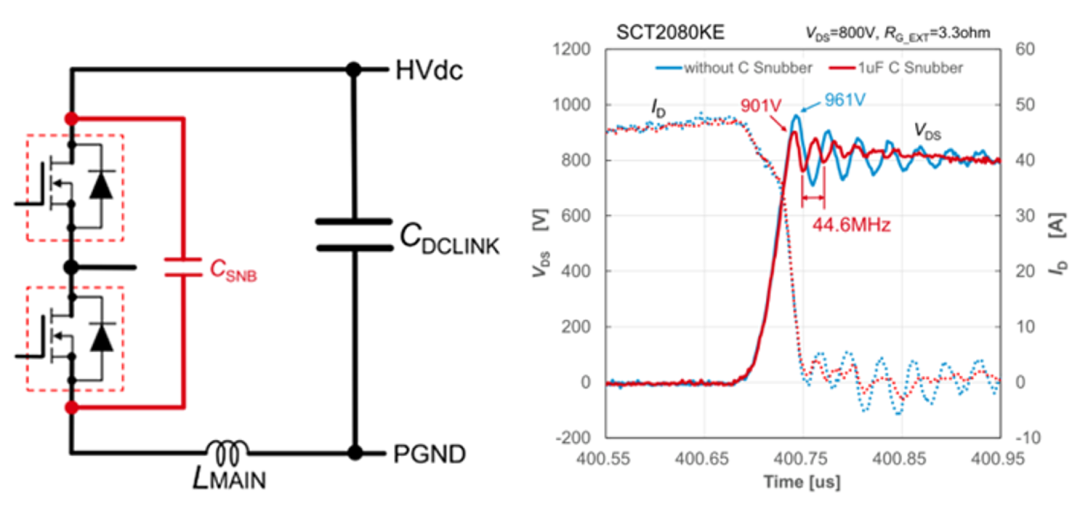

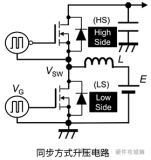

开关导通时,线路和电路板版图的电感之中会直接积蓄电能(电流能量)。当该能量与开关器件的寄生电容发生谐振时,就会在漏极和源极之间产生浪涌。下面将利用图1来说明发生浪涌时的振铃电流的路径。这是一个桥式结构,在High Side(以下简称HS)和Low Side(以下简称LS)之间连接了一个开关器件,该图是LS导通,电路中存在开关电流IMAIN的情形。通常,该IMAIN从VSW流入,通过线路电感LMAIN流动。

图1:产生关断浪涌时的振铃电流路径

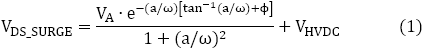

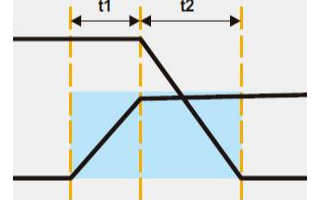

接下来,LS关断时,流向LMAIN的IMAIN一般是通过连在输入电源HVdc和PGND之间的大容量电容CDCLINK,经由HS和LS的寄生电容,按照虚线所示路径流动。此时,在LS的漏极和源极之间,LMAIN和SiC MOSFET的寄生电容COSS(CDS+CDG)就会产生谐振现象,漏极和源极之间就会产生浪涌。如果用VDS_SURGE表示施加在HVdc引脚的电压,用ROFF表示MOSFET关断时的电阻,则该浪涌的最大值VHVDC可以用下述公式表示(*1)。

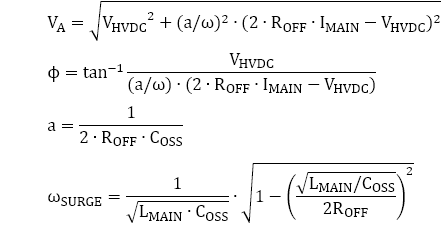

图2是使用SiC MOSFETSCT2080KE进行测试时关断时的浪涌波形。当给HVdc施加800V的电压时,可以算出VDS_SURGE为961V,振铃频率约为33MHz。利用公式(1),根据该波形,可以算出LMAIN约为110nH。

图2:关断浪涌波形

再接下来,增加一个图3所示的缓冲电路CSNB,实质性地去掉LMAIN后,其关断浪涌的波形如图4所示。

图3:C缓冲电路

图4:通过C缓冲电路降低关断浪涌

可以看到,增加该CSNB之后,浪涌电压降低50V以上(约901V),振铃频率也变得更高,达到44.6MHz,而且包括CSNB在内,整个电路中的LMAIN变得更小。

同样,利用公式(1)计算LMAIN,其结果由原来的110nH左右降低至71nH左右。原本,最好是在进行版图设计时,将线路电感控制在最低水平。但是,在实际设计过程中,往往会优先考虑器件的散热设计,所以线路并不一定能够按照理想进行设计。

在这种情况下,其对策方案之一就是尽可能在开关器件附近配置缓冲电路,使之形成旁路电路。这样既可以将线路电感这一引发浪涌的根源降至最低,还可以吸收已经降至最低的线路电感中积蓄的能量。然后,通过对开关器件的电压进行钳制,就可以降低关断浪涌。

*1:“开关转换器基础”P95-P107,P95~P107 作者:原田耕介、二宫保、顾文建,出版社:CORONA PUBLISHING CO., LTD. 1992年2月

了解碳化硅功率元器件及其应用案例

介绍了在电源产品的小型化、降低功耗和提高效率方面具有巨大潜力的碳化硅(SiC)的基本物理特性,以及SiC二极管和晶体管的使用方法及其应用案例。

漏极和源极之间产生的浪涌

相关文章一览

·SiC MOSFET:缓冲电路的设计方法 —前言—

·缓冲电路的种类和选择

·C缓冲电路的设计

·RC缓冲电路的设计

·放电型RCD缓冲电路的设计

·非放电型RCD缓冲电路的设计

·封装引起的浪涌差异

· SiC MOSFET:缓冲电路设计方法 —总结—

END✦

咨询或购买产品

扫描二维码填写相关信息

将由工作人员与您联系

点击阅读原文 了解更多信息

-

罗姆

+关注

关注

4文章

408浏览量

66323

原文标题:R课堂 | 漏极和源极之间产生的浪涌

文章出处:【微信号:罗姆半导体集团,微信公众号:罗姆半导体集团】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

mos管源极和漏极电流相等吗

mos管连续漏极电流是什么

mos管漏极电压增大,为什么沟道变窄

晶体管的漏极与源极有什么区别

MOS管源极和漏极是什么意思

场效应管栅源极电压的影响因素

mosfet漏极外接二极管的作用 mosfet源极和漏极的区别

为什么叫源极跟随器 源极跟随器的作用和特点

R课堂 | 漏极和源极之间产生的浪涌

R课堂 | 漏极和源极之间产生的浪涌

评论