IP核配置

定制输出数据位宽

这里的输出数据指的是输出的波形数据,其位宽相关参数介绍如下:

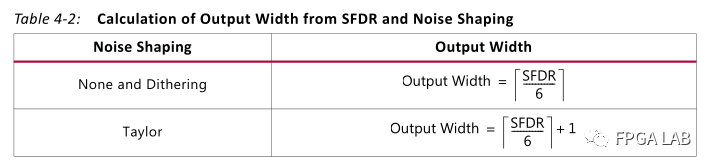

可见,输出数据宽度和SFDR以及Noise Shaping有关,你可先不必知道Noise Shaping和SFDR是什么?只需要暂时知道在IP核定制时需要选择即可,如果Noise Shaping选择了None and Dithering,则输出数据宽度为:

如果为Taylor:

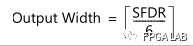

而Spurious Free Dynamic Range (SFDR)翻译为无杂散动态范围,和输出数据宽度以内部总线宽度以及各种实现策略有关;假设我需求的数据宽度为10位,Noise Shaping选为None,则SFDR为60,输入IP定制页面:

查看输出是否为10bit:

定制相位位宽(或频率分辨率)

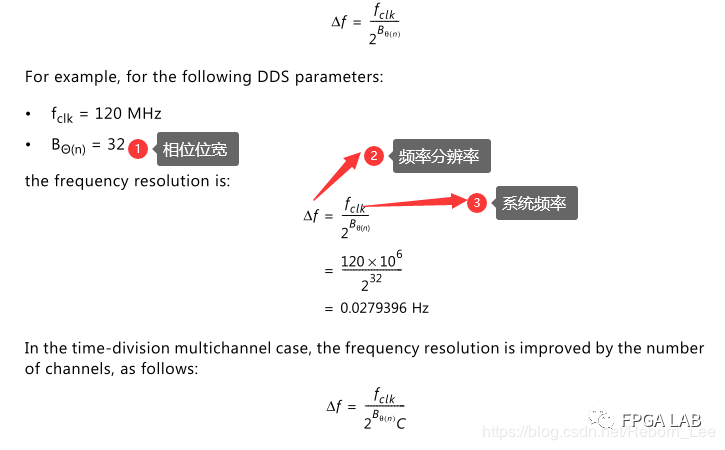

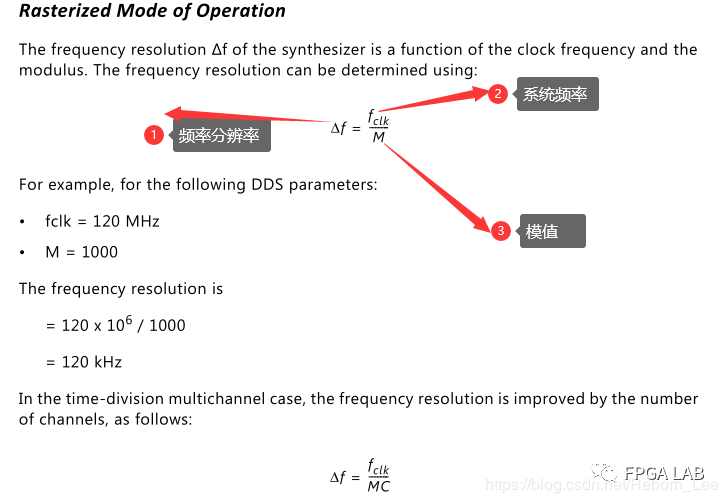

根据数据手册对频率分辨率的描述:

频率分辨率:以赫兹为单位指定,指定最小频率分辨率,用于确定相位累加器使用的相位宽度及其相关的相位增量(PINC)和相位偏移(POFF)值。较小的值可提供较高的频率分辨率,并且需要较大的累加器。较大的值会减少硬件资源。根据噪声整形的选择,可以增加相位宽度,并且频率分辨率高于指定的分辨率。

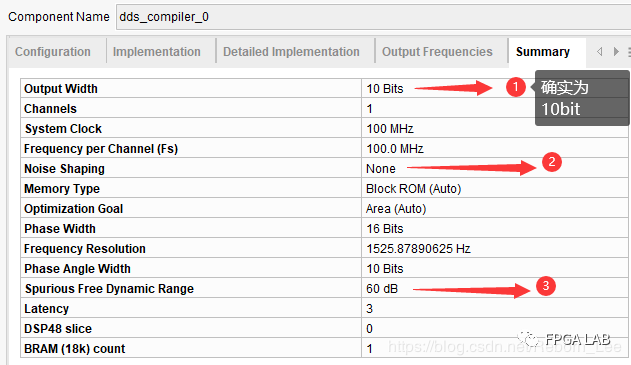

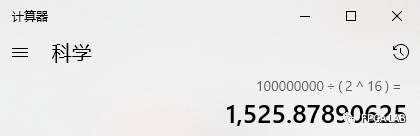

对于光栅化模式(rasterized mode),频率分辨率由系统时钟、通道数和所选模数固定。从这段描述,我们得出信息,频率分辨率可以用来控制相位位宽。如果操作模式选择标准模式,如下IP 核定制页面:

频率分辨率可以这样计算:

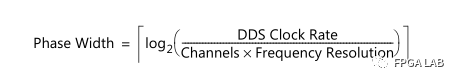

我们先给定需求的相位宽度,又已知系统频率值,根据公式就可以算出频率分辨率;将频率分辨率代入IP核定制页面,即可自动得到相位宽度。 其实从上式也可以直接推出相位宽度:

本例我们的系统频率为100MHz,如果想要相位宽度为16位,则频率 分辨率为:

在IP核定制页面,如下图,我们输入频率分辨率的值:

查看相位宽度为16位:

上面选择的是标准模式,如果选择另一种模式呢?Rasterized Mode of Operation:光栅化操作模式;我们可以根据下面公式得到频率分辨率, 但和相位宽度没有直接关系 ,为了知识完整性,简介如下:

在IP核定制页面提现如下:

输出频率

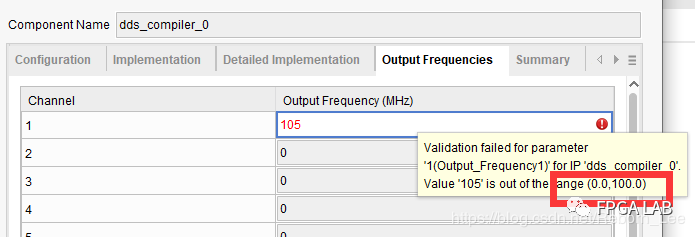

本示例选择的是单通道,也即通道数为1,因此输出频率也只能选择一个:

输出频率值也不是随便选择的,而是有其范围的,例如我输入105MHz,则通过不了:

提示超出范围,范围为(0,100).

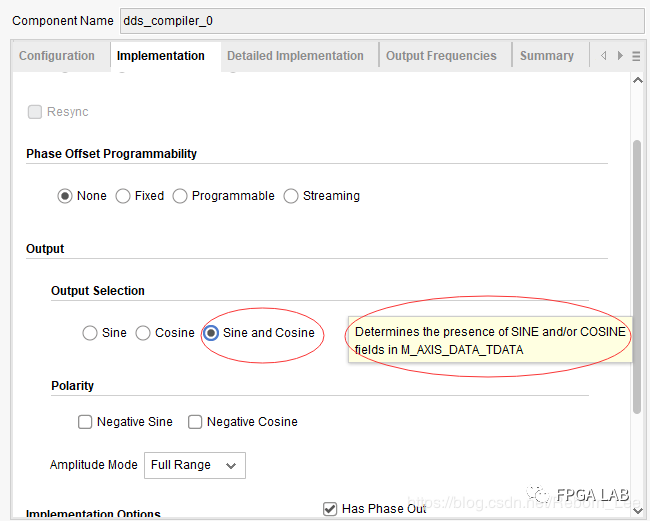

输出正余弦选择以及数据格式

可以在IP核定制页面选择输出正弦还是余弦还或者是都输出:

本示例选择输出正余弦,由于输出采用的是axi总线,因此输出数据位于M_AXIS_DATA_TDATA中,那么正余弦输出结果是如何组合成M_AXIS_DATA_TDATA的呢?

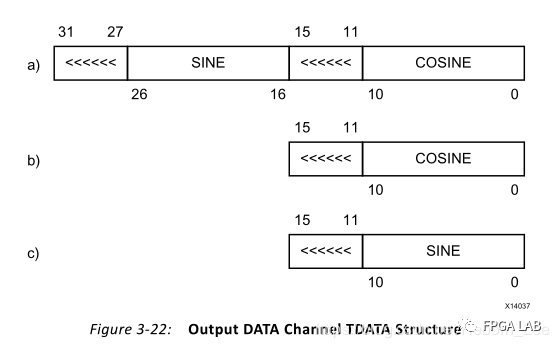

数据手册给出解释:

输出DATA通道TDATA结构将正弦和余弦输出字段符号扩展到下一个字节边界,然后以最低有效部分的余弦进行连接,以创建m_axis_data_tdata。如果仅选择正弦或余弦之一,则将其符号扩展并放入m_axis_data_tdata的最低有效部分。

下图显示了这三种配置的TDATA的内部结构。正交输出,仅余弦和仅正弦。例如,在图中显示了11位输出,符号扩展到16位。<<<表示符号扩展名:

因此我们可以这么认为,由于存在扩展符号位的关系,我们可以提取低一半的数据为COS,高一半的数据未SIN。

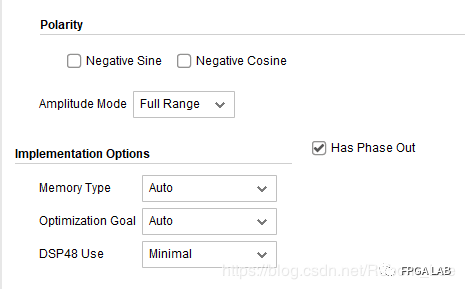

其他设置

有了上面的定制参数,输出波形是没有问题了,至于其他的定制参数,本文选择默认:

点击OK,等待IP核定制完成。

电路设计

本示例设计十分简单,就是单纯例化下IP核:

复制例化模板:

给出设计文件:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: Reborn Lee

// Module Name: waveform_gen

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: Reborn Lee

// Module Name: waveform_gen

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module waveform_gen(

input i_clk,

output o_data_valid,

output [31 : 0] o_data,

output o_phase_valid,

output [15 : 0] o_phase

);

dds_compiler_0 inst_dds (

.aclk(i_clk), // input wire aclk

.m_axis_data_tvalid(o_data_valid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(o_data), // output wire [31 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(o_phase_valid), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(o_phase) // output wire [15 : 0] m_axis_phase_tdata

);

endmodule

求一种基于DDS IP核的任意波形发生器设计方案

求一种基于DDS IP核的任意波形发生器设计方案