引言

类似于电源域(电源规划与时钟规划亦是对应的),假如设计中所有的 D 触发器都使用一个全局网络 GCLK ,比如 FPGA 的主时钟输入,那么我们说这个设计只有一个时钟域。假如设计有两个输入时钟,分别给不同的接口使用,那么我们说这个设计中有两个时钟域,不同的时钟域,有着不同的时钟频率和时钟相位。

在实际的 FPGA 系统设计中,经常有多个不同的时钟源的参与,比如 FPGA 内部的 Clock Wizard 时钟分频 IP 核,连接到许多不同的频率输入的 IP 模块,这个在视频显示系统中是很常见的,毕竟,不同的视频显示格式需要不同的像素频率,也就需要不同的输入时钟。例如 640X480@60Hz 需要 25.175MHz 时钟,而 1280X720@60Hz 需要 74.2MHz 时钟等等。

一、跨时钟域处理方式

1、对于单比特数据的跨时钟域: 打两拍 (即定义两级寄存器对输入数据进行延拍,这个在解决 “亚稳态” 方式的随笔中已经提及)。

2、对于多比特数据的跨时钟域: 异步 FIFO(异步双口 RAM) 。例如前面一个模块的数据发送速率为 100MHz,而后面一个模块的数据接收速率为 50MHz,这样就是数据速率传输的不同步,那么,我们可以在中间插入一个异步 FIFO,一端接收前面的 100MHz 速率的数据进行缓存,另一端发送 50MHz 速率的数据,从而达到数据的同步接收与发送。当然,这里的 FIFO 的深度就需要自己计算了。

3、 握手协议 。由于两个异步时钟的频率关系不确定,所以,也就无法保证能否满足触发器之间的建立时间和保持时间,如果违反了建立时间或者保持时间的要求,那么接收域将会采样到处于亚稳态的数据,那么系统就可能崩溃了。

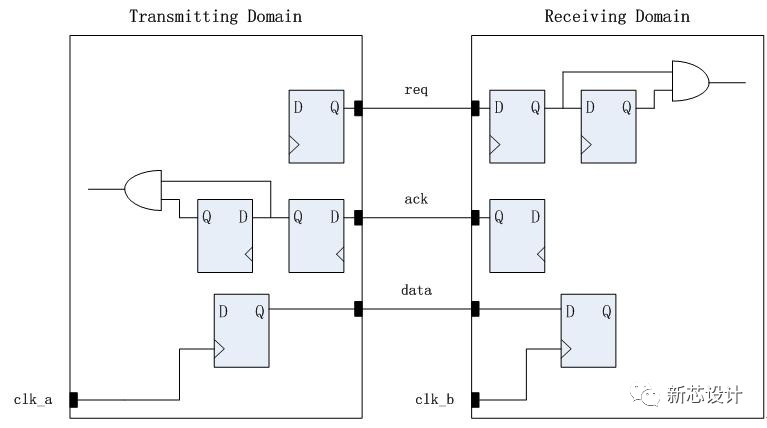

因此,我们可以使如下用握手协议方式处理跨时钟域数据传输,只需要对双方的握手信号(req 和 ack)分别使用脉冲检测方法进行同步。如下所示,假设 req、ack、data 总线在初始化时都处于无效状态,发送域先把数据放入总线,随后发送有效的 req 信号给接收域,接收域在检测到有效的 req 信号后锁存数据总线,然后回送一个有效的 ack 信号表示读取完成应答,发送域在检测到有效 ack 信号后撤销当前的 req 信号,接收域在检测到 req 撤销后也相应撤销 ack 信号,此时完成一次正常握手通信。

基于握手协议的跨时钟域处理方式

此后,发送域可以继续开始下一次握手通信,依次循环。该握手协议方式能够保证接收到的数据稳定可靠,有效的避免了亚稳态的出现,但是,控制信号握手检测会消耗通信双方较多的时间和资源。这样的通信协议类似于 AXI4-Stream 流协议,当然,前者是一次握手发送一次数据,后者是一次握手可以连续发送数据,AXI4-Stream 流协议的主要通信信号为 tvalid 和 tready,这个协议在视频流传输中非常重要且实用,大家可以去学一学。

-

FPGA

+关注

关注

1634文章

21819浏览量

607399 -

fifo

+关注

关注

3文章

391浏览量

44017 -

时钟

+关注

关注

11文章

1752浏览量

132018 -

触发器

+关注

关注

14文章

2024浏览量

61445

发布评论请先 登录

相关推荐

跨时钟域处理方式

跨时钟域处理方式

评论