一、锁相环是什么?

锁相环是一种利用相位同步产生电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。

锁相环就是通过负反馈控制系统,让压控振荡器的固有振荡频率fo 和输入的参考信号fi 的相位保持在误差允许范围内,从而让振荡频率fo达到和参考信号fi 同步相位频率的目的。一般来说,参考信号fi 的信号特性更好,通过锁相系统提高振荡频率fo的信号特性,同时还可以将参考信号fi 转化为你想要的任意(最好整数倍)频率信号。

二、基本理论

1.工作原理

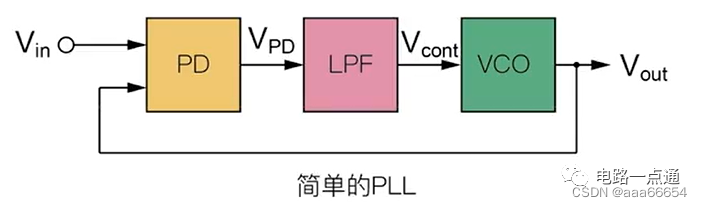

最基础的锁相环系统主要包含三个基本模块:鉴相器(Phase Detector:PD)、环路滤波器(L00P Filter:LF)其实也就是低通滤波器,和压控振荡器(Voltage Controlled Oscillator:VCO)。有了这三个模块的话,最基本的锁相环就可以运行了。但我们实际使用过程中,锁相环系统还会加一些分频器、倍频器、混频器等模块。(这一点可以类比STM32的最小系统和我们实际使用STM32的开发板)

我们从锁相系统开始运行的那一刻进行分析,这个时候鉴相器有两个输入信号,一个是输入

的参考信号Vin,另一个是压控振荡器的固有振荡信号Vout。这个时候由于两个信号的频率不

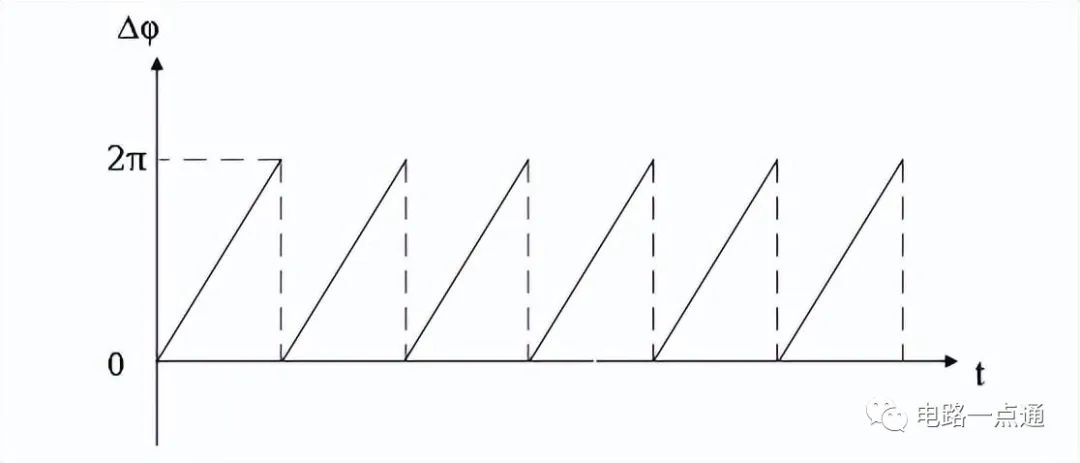

相同,会因为频差而产生相位差,如果不对压控振荡器进行任何操作,那么相位差会不断累积,从而跨越2Π角度,从零重新开始测相位,如图3所示。这便是测量死区,明明相位在不断变大,但鉴相器只能测出0~2Π的范围,测出的相位差最大便是2Π,这样就导致了鉴相器的输出电压只能在一定的范围内波动。理想状态是让这两个信号的相位差一直保持在2Π的范围内,不进入测量死区。那么在系统刚开始的时候,鉴相器测出两个信号的相位差,将相位差时间信号转化为误差电压信号输出(具体转化过程见鉴相器讲解)。通过环路滤波器转化为压控电压加到压控振荡器上,使压控振荡器的输出频率Vout逐步同步于输入信号Vin,直到两个信号的频率逐渐同步,相位差也在测量误差范围内,那么整个系统就稳定下来了。两个信号的相位差不会累积变大,而是保持相对固定的相位差。(不是常规意义上的固定不变,而是在误差允许范围内的微小波动)

2.鉴相器(PD)

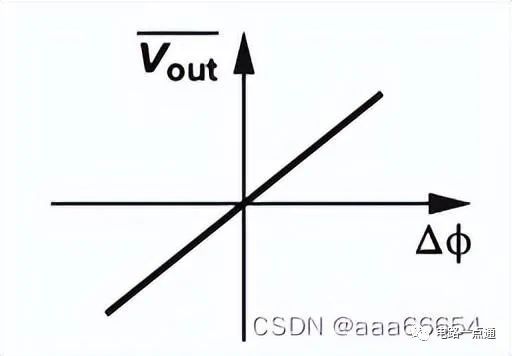

鉴相器的作用就是将相位差信号转化为误差电压信号。那么它的传递关系理想上是图所示,最好有一定的线性关系。

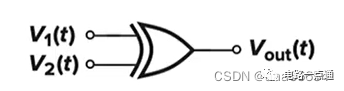

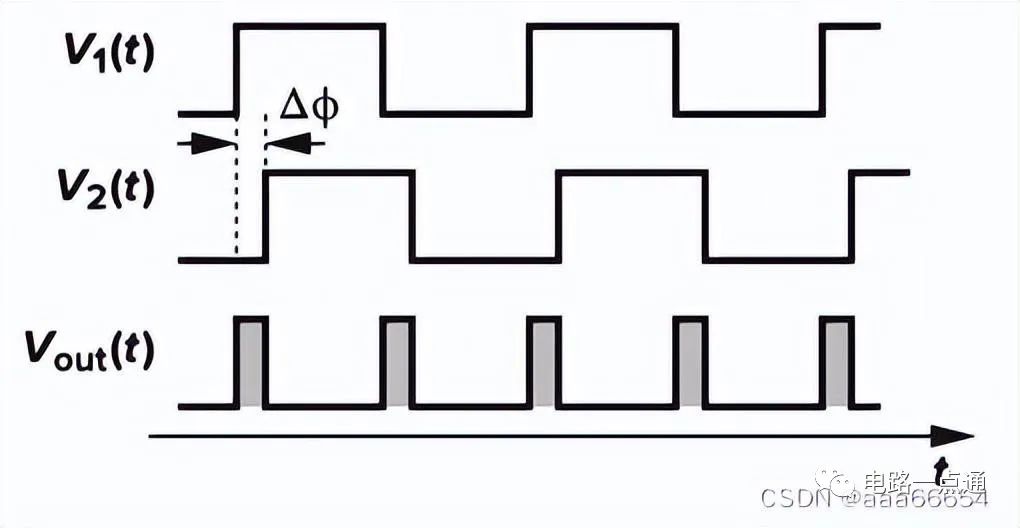

那么鉴相器可以鉴别两个信号的相位差,它是如何实现的?其实很简单,异或门就可以实现,如图5,6所示。鉴相器的输入端是两个信号,只要两个信号异或不为零,就说明有相位差,异或出来的信号就是含有它们相位差信息的电压信号。

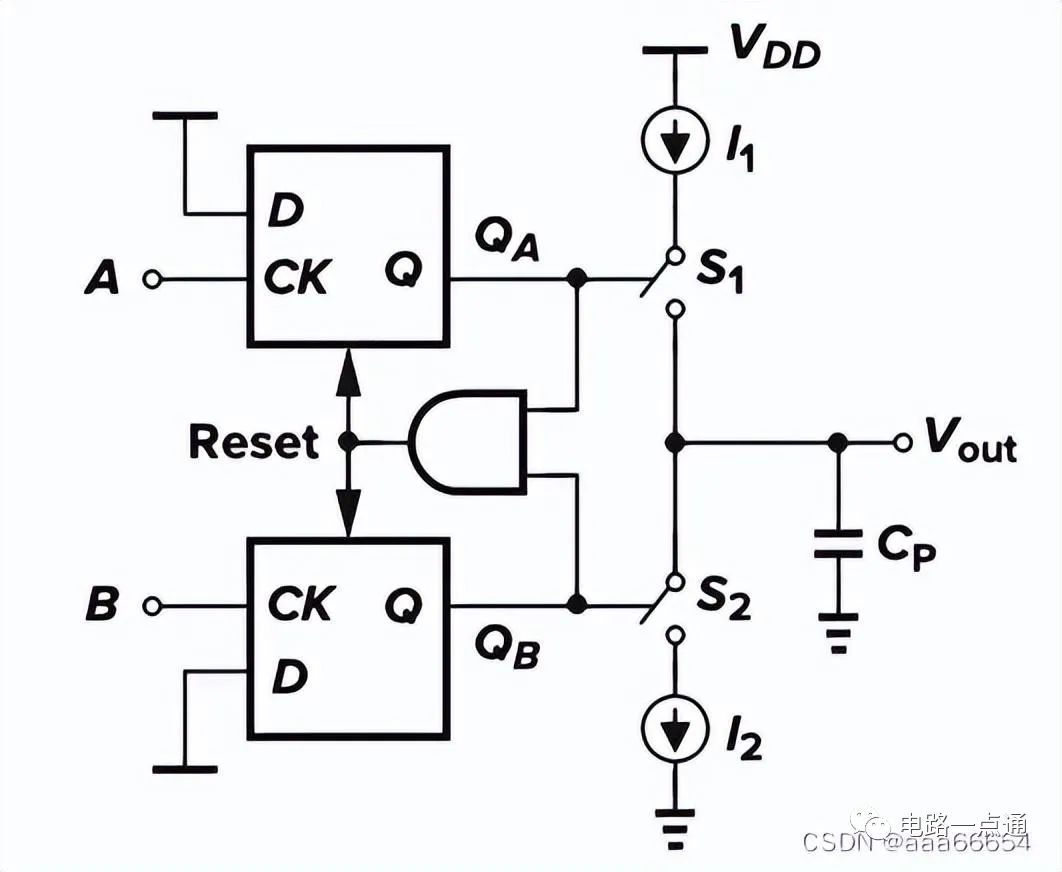

实际使用的鉴相器不是简单的异或门,有非时钟PD、预充电PD等多种形式,这些我没用到,所以没有具体理解。这里讲解我项目用到的一款锁相芯片AD9517(后面会讲,嗯,算是我给自己挖的第一个坑,哈哈),这款芯片是带电荷泵的鉴相鉴频器,如图7所示。为什么使用的是鉴相鉴频器呢?是因为PLL刚开始工作的时候,它的VCO的工作频率可能和输入频率偏差很大,仅仅检查相位偏差,捕获范围较小,PLL需要很长的时间才能进入锁定状态。所以为了提高PLL的响应速度,提高捕获范围,使用鉴相鉴频器。

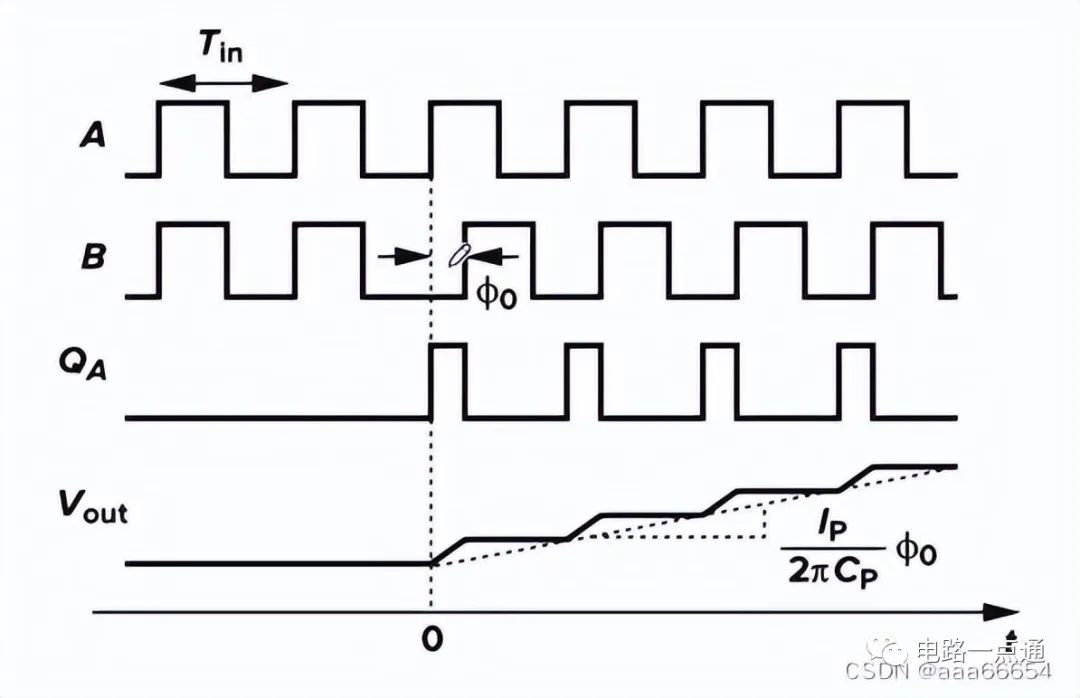

两个D触发器的D端都是接电源端,当A信号相位超前于B信号,那么它的高电平先到来,则A的D触发器输出高电平,S1开关闭合,上面电荷泵开始灌电流。当B信号高电平到来,则B的D触发器输出高电平,而QA和QB一旦同时为高,则中间的与门就会输出高电平,就会使两个D触发器复位,从而都输出低电平,两个门都处于断开状态。同理,当B信号相位超前于A信号,那么它的高电平先到来,则B的D触发器输出高电平,S2开关闭合,下面电荷泵开始拉电流。当A的信号高电平到来,则A的D触发器输出高电平,而QA和QB一旦同时为高,则中间的与门就会输出高电平,就会使两个D触发器复位,从而都输出低电平,两个门都处于断开状态。(一般中间的与门和RESET端中间会加DELAY电路,这样是为了避免实际使用中两个信号都出现高电平,而由于电路的延时不确定性,导致到复位端的电平不确定而形成毛刺干扰的问题)

这样就把相位差信号通过电荷泵充电时间长短,转化电流的大小,这里简单的推一下它的线性模型。如图8所示。由相位差

相位差为

则相位差对应的时间为

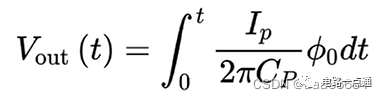

那么在这段时间内输出电压增加

基于此我们可以计算出

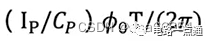

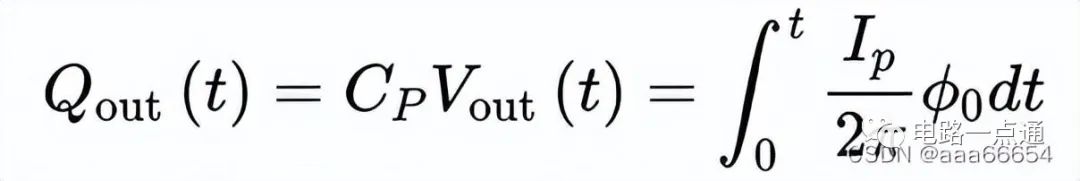

那么输出的电荷表示为

有了电荷,我们就可以计算输出电流,

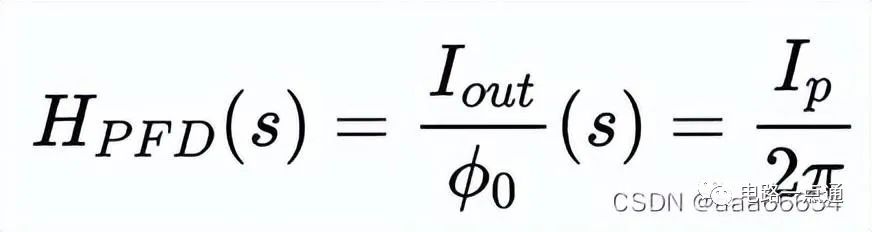

我们可以看到这是一个相位差和输出电流的关系式,鉴相鉴频器就可以看作是一个相位差为输入,电荷泵输出电流为输出的器件,我们就可以计算出该传输函数为

这个值我们也可以看作是鉴相鉴频器的增益。那么鉴相鉴频器就介绍到这里了,总的来说,鉴相鉴频器就是将相位差数据转化为了和它有线性关系的输出电流。但压控振荡器是受电压变化来改变输出频率的,所以还需要在鉴相鉴频器和压控振荡器之间加一个环路滤波器,将电流信号转化为电压信号,同时还可以滤除鉴相鉴频器中电荷泵的开关打开关闭所带来的纹波噪声以及毛刺,让压控电压更加平滑。

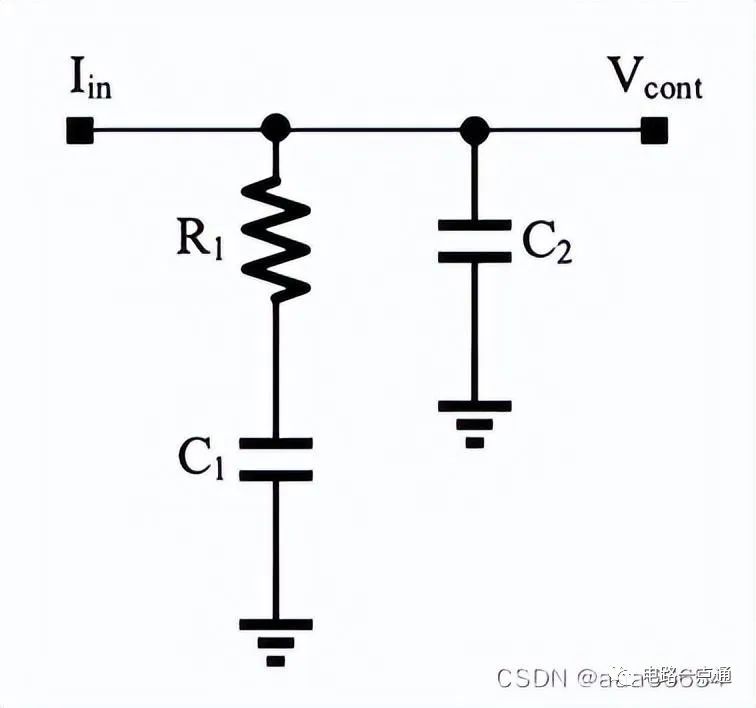

3.环路滤波器(LF)

为了提升系统稳定性和减小输出控制电压的纹波,会在鉴相鉴频器后加一个环路滤波器。一阶的环路滤波器只是一个电容,见图7的Cp,一阶的易使整个系统不稳定,现在基本看不到了,这里详细介绍二阶环路滤波器。

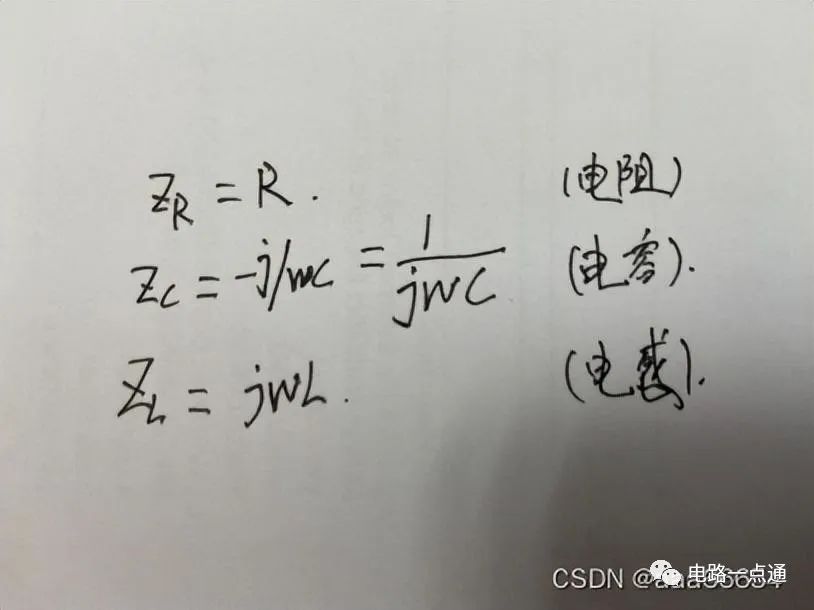

这里详细推导一下它的传递关系式,电阻电容电感的阻抗计算

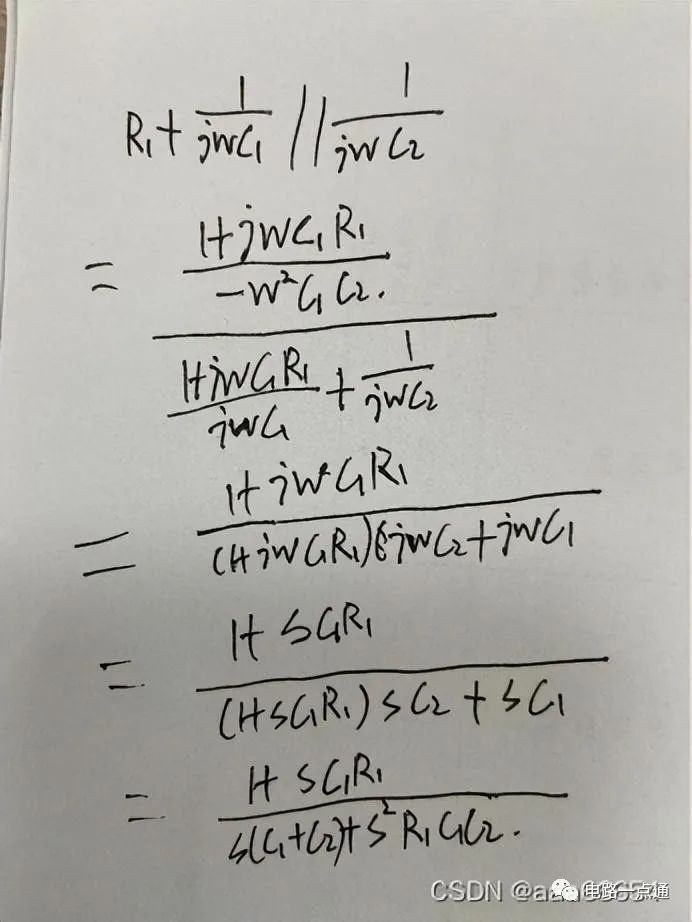

那么根据这个我们计算出它的传递函数

审核编辑:汤梓红

-

锁相环

+关注

关注

35文章

583浏览量

87687 -

控制系统

+关注

关注

41文章

6537浏览量

110460 -

滤波器

+关注

关注

160文章

7725浏览量

177630 -

振荡器

+关注

关注

28文章

3811浏览量

138859 -

负反馈

+关注

关注

6文章

216浏览量

30016

原文标题:锁相环原理与公式讲解

文章出处:【微信号:电路一点通,微信公众号:电路一点通】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

软件锁相环的设计与应用

锁相环原理

数字锁相环(DPLL),数字锁相环(DPLL)是什么?

模拟锁相环,模拟锁相环原理解析

详解FPGA数字锁相环平台

锁相环原理与公式讲解

锁相环原理与公式讲解

评论