你手上的样片,是什么类型的样片?如果是未经过Corner验证和可靠性测试的,需要多注意~ 这也是很多公司喜欢选择被头部企业验证过的量产芯片原因;

今天,小二和大家介绍下,芯片设计完成后,一般会经过的几次关键投片

1

什么是MPW,为什么要MPW

MPW和电路设计PCB的拼板打样类似,全名叫Multi Project Wafer,多项目晶圆,是将不同芯片公司基于相同工艺设计的芯片放在同一晶圆上流片;

晶圆厂每年都会有固定的几次MPW机会,叫Shuttle (班车),到点即发车,是不是非常形象

不同公司拼Wafer,得有个规则,MPW按SEAT来锁定面积,一个SEAT一般是3mm*4mm的一块区域,一般晶圆厂为了保障不同芯片公司均能参与MPW,对每家公司预定的SEAT数目会限制;(其实SEAT多了,成本也就上去了,MPW意义也没有了)

因为是拼Wafer,因此通过MPW拿到的芯片数目就会很有限,主要用于芯片公司内部做验证测试,也可能会提供给极少数的头部客户;

从这里大家可能已经了解了,MPW是一个不完整的,不可量产的投片;

那,为什么要做MPW呢?

因为芯片投资太贵了,而基于新工艺或者变化较大的新设计,如果设计有问题,投片的最差结果可能是无法点亮,或者关键的功能,性能不及预期,小则几百万,多则上千万打水漂;

MPW投片成本小,一般就小几十万,可以很好降低风险;

需要注意的是,因为MPW从生产角度是一次完整的生产流程,因此其还是一样耗时间,一次MPW一般需要6~9个月,会带来芯片的交付时间后延;

2

晶圆生产角度真正了解MPW

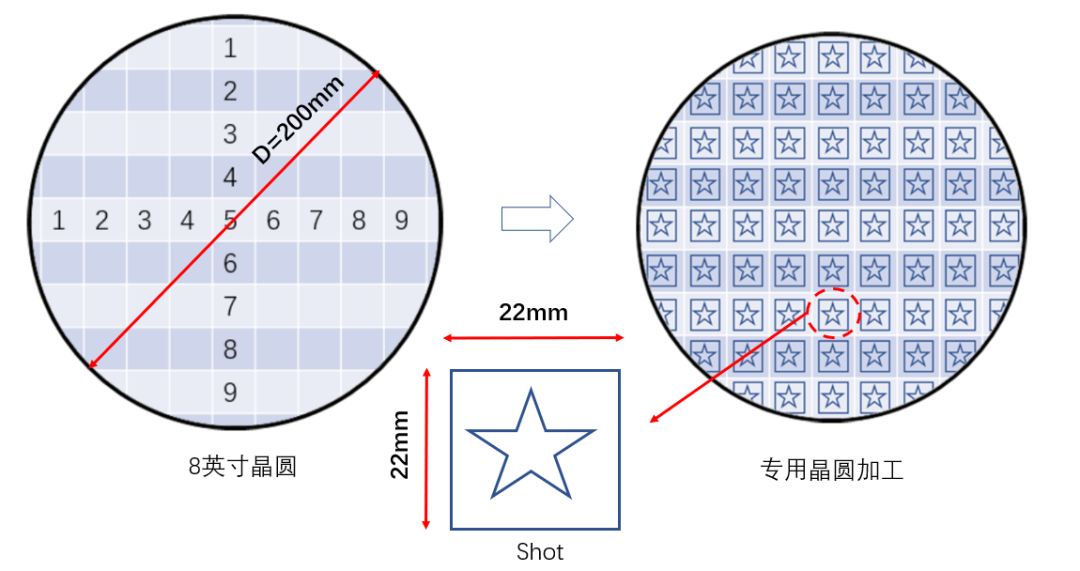

毕竟芯片加工还是一个相对复杂的过程,我相信很多朋友看完第一节,和小二之前理解的晶圆结构,是下图的,一个框归属于一个芯片公司

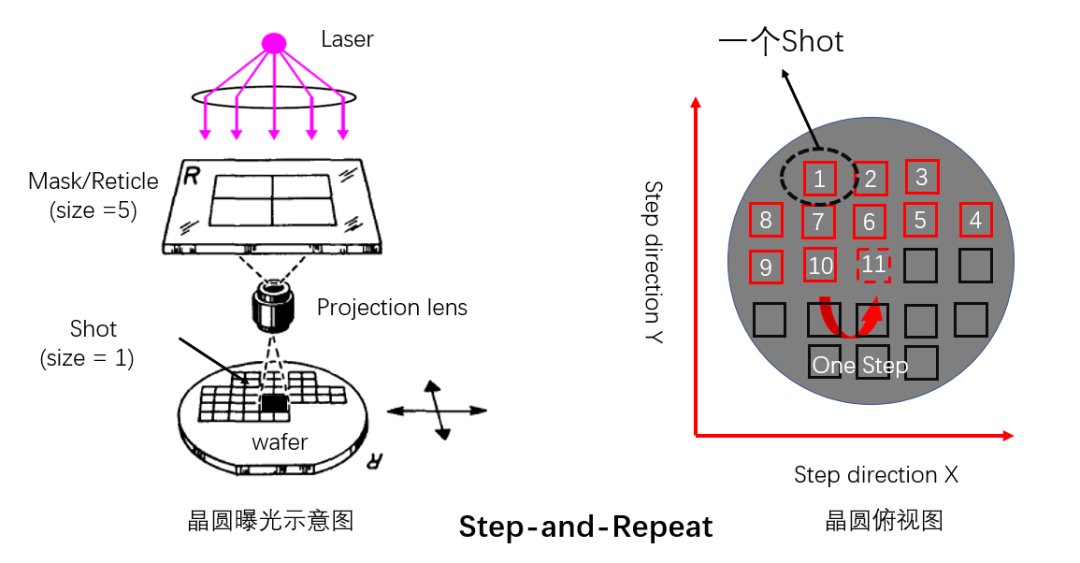

图片:CUMEC服务平台 实则不然,这就需要和晶圆的生产流程的光刻技术相关了; 现阶段的光刻技术DUV/EUV等,大多采用缩影的方式进行曝光,如下图所示

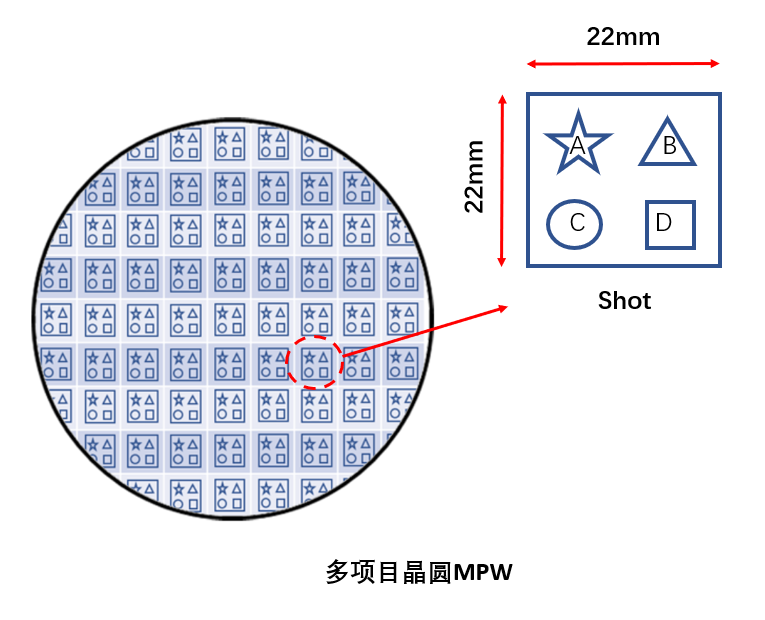

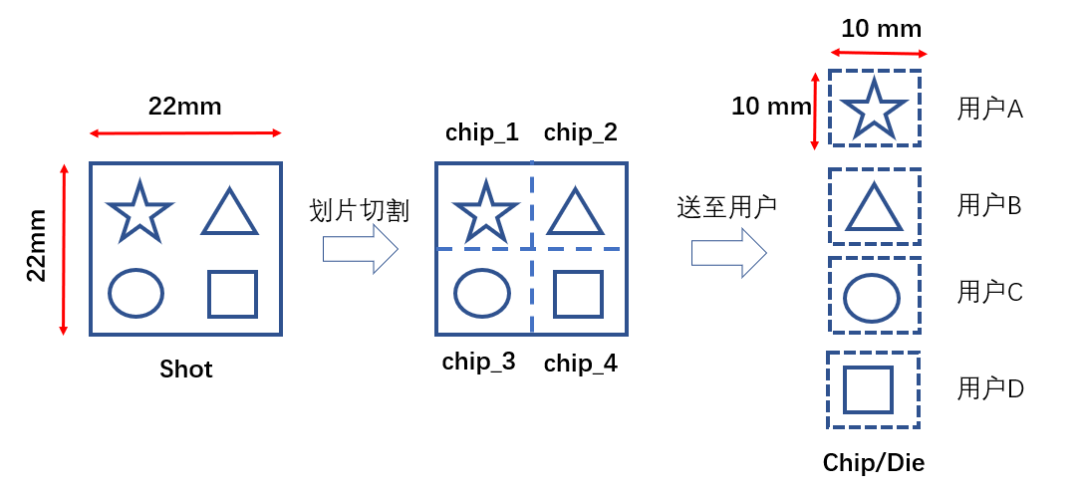

图片:CUMEC服务平台 采用1:5 放大的mask,对晶圆进行曝光,一次曝光的矩形区域通常称为一个shot,完成曝光后,***自动调整晶圆位置,对下个shot进行曝光,如此循环(Step-and-Repeat),直到整个晶圆完成曝光,而这一个Shot的区域,则是大家一起分担SEAT的区域; 如下示意图中,一个Shot里面划分4个小格,每个格子给到一家厂商的设计

图片:CUMEC服务平台

图片:CUMEC服务平台

一般而言,MPW晶圆一般最多20个用户分享;

3

什么是FullMask

FullMask,“全掩膜”,即制造流程中的全部掩膜都为某个设计服务,即上节中所有Shot里都是同一家的;

图片:CUMEC服务平台

FullMask的芯片,一片晶圆可以产出上千片DIE;然后封装成芯片,可以支撑大批量的客户需求;

4

什么是ECO

如果MPW或者FullMask的芯片,验证有功能或者性能缺陷,就需要改版了,也经常会用到ECO这个词;

ECO,即EngineeringChange Order的缩写,指工程改变命令,简单来说就是手动修改集成电路的过程,换句话说,就是直接手动修改netlist。

ECO可以发生在Tapeout之前,过程中,或者之后;Tapeout之后的ECO,改动少的可能仅需要改几层Metal layer,改动大的话可能需要动十几层Metal layer,甚至重新流片;

有的芯片设计公司,芯片可以ECO 5次以上,也是刷新了小二的认知;

5

什么是Corner片

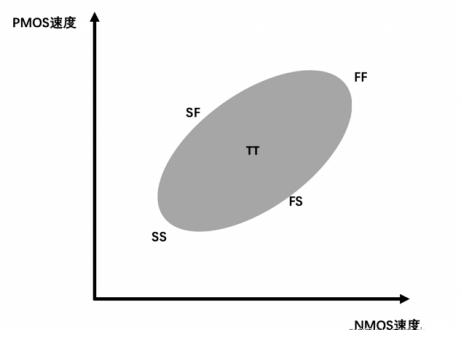

大家知道,芯片的生产制造是一个化学&物理过程,

工艺偏差(包括掺杂浓度、扩散深度、刻蚀程度等)会导致不同批次晶圆之间,同一批次不同晶圆之间,同一晶圆不同芯片之间的性能都是不相同的

在一片wafer上,不可能每点的载流子平均漂移速度都是一样的,随着电压、温度不同,它们的特性也会不同,把他们分类就有了PVT(Process,Voltage,Temperature)

而Process又分为不同的corner:

TT:Typical N Typical P

FF:Fast N Fast P

SS:Slow N Slow P

FS:Fast N Slow P

SF:Slow N Fast P

为了保证性能,在正式量产前,芯片都会投专门的Corner片,用于验证工艺偏差在设计范围内;

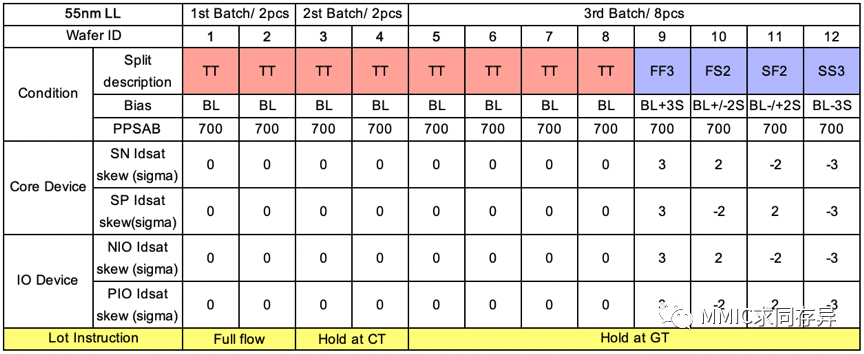

如下是55nm Logic工艺片的例,拟定的corner split table

转自 MMIC求同存异

#1 & #2 两片pilot wafer,一片盲封,一片测CP

#3 & #4 两片hold在Contact,为后道改版预留工程wafer,可以节省ECO流片时间

#5~#12 八片hold在Poly,等pilot的结果看是否需要调整器件速度,并验证corner

除了留有足够的芯片用于测试验证,Metal Fix,还应根据项目需求,预留尽可能多的wafer作为量产出货

MMIC求同存异:流片Corner Wafer介绍

你手上的样片,是什么类型的样片?如果是未经过Corner测试和可靠性测试的,需要多注意~ 这也是很多公司喜欢选择被头部企业验证过的量产芯片原因;

-

芯片

+关注

关注

455文章

50786浏览量

423457 -

晶圆

+关注

关注

52文章

4908浏览量

127963 -

芯片设计

+关注

关注

15文章

1019浏览量

54891

原文标题:芯片量产前:多次投片,走过漫长的路

文章出处:【微信号:IC大家谈,微信公众号:IC大家谈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

两家公司倒在量产前夕,垂直GaN为什么落地难

adc12d1800两个通道采样,Q路正常,I路异常,为什么?

昕感科技完成晶圆厂首批投片

芯片量产前:多次投片,走过漫长的路

芯片量产前:多次投片,走过漫长的路

评论