MicroBlaze CPU 是可修改的拖入式预设 32 位/64 位 RISC 微处理器配置系列。

MicroBlaze 处理器能满足众多多样化的应用程序的不同需求,惠及工业、医疗、汽车、消费品和通信市场。MicroBlaze 使用哈佛 (Harvard) 架构,此架构的 PL 内通常包含双 LMB BRAM。

但在本篇博文中,我们将探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用。

退出复位时,MicroBlaze 将从 MicroBlaze 配置中的 C_BASE_VECTORS 参数内指定的存储器地址提取其指令。在本例中,此 C_BASE_VECTORS 将设置为 PSU DDR 内的某个区域。

但根据采用的启动流程,这样可能导致潜在问题,即 PSU DDR 可能无法先于 PL 完成配置。这可能导致 MicroBlaze 挂起。为避免此现象,我们可以使用 MicroBlaze 上的“Reset Mode”(复位模式)信号。

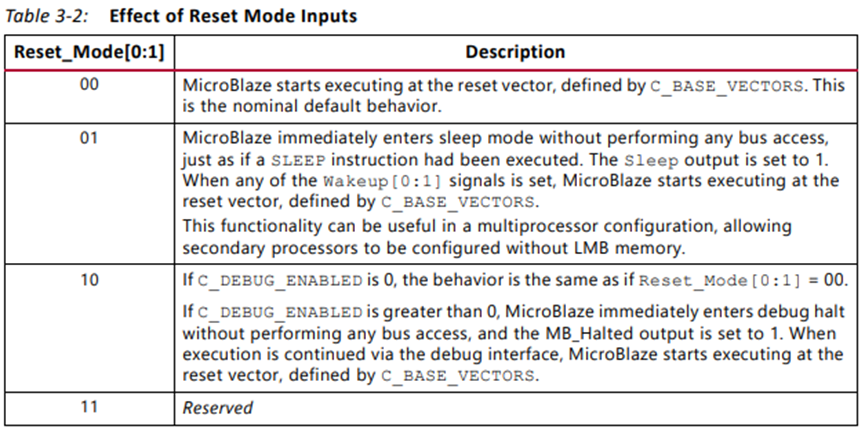

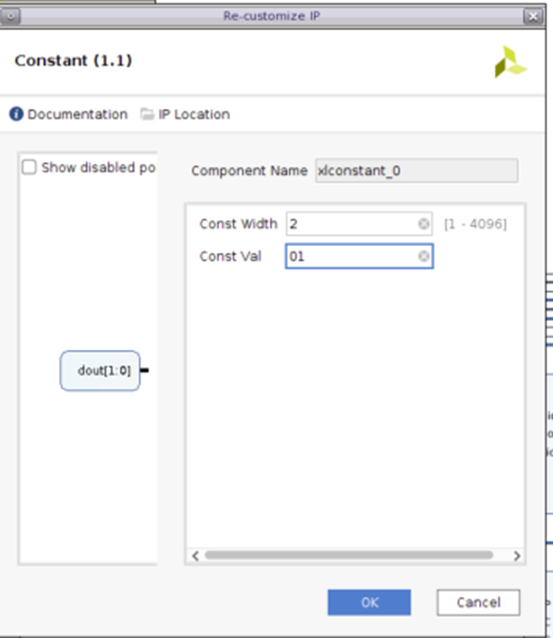

在上表中,可以看到各种 reset_mode 配置。最适合我们的用例的配置为“01”,其中 MicroBlaze 将保持处于复位状态,直至我们准备就绪为止。我们将在 PSU 上通过 EMIO 来使用 GPIO 对 MicroBlaze 进行解复位。

创建硬件:

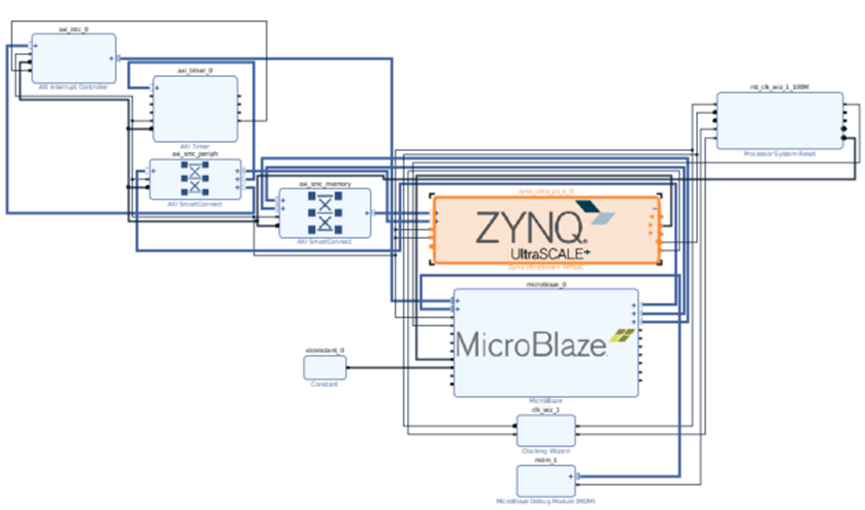

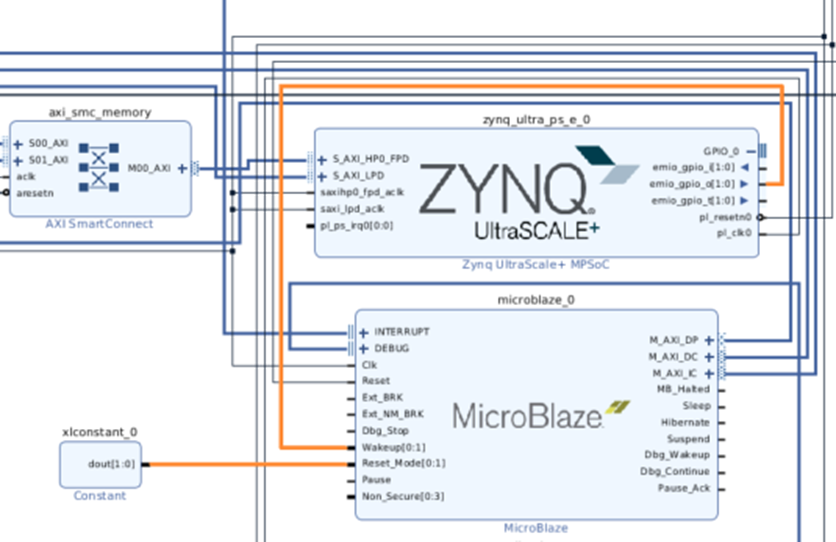

Vivado IP integrator 块设计如下所示:

用户可以根据自己认为合适的方式来自定义设计。

关键组件配置如下所述。

MicroBlaze 配置:

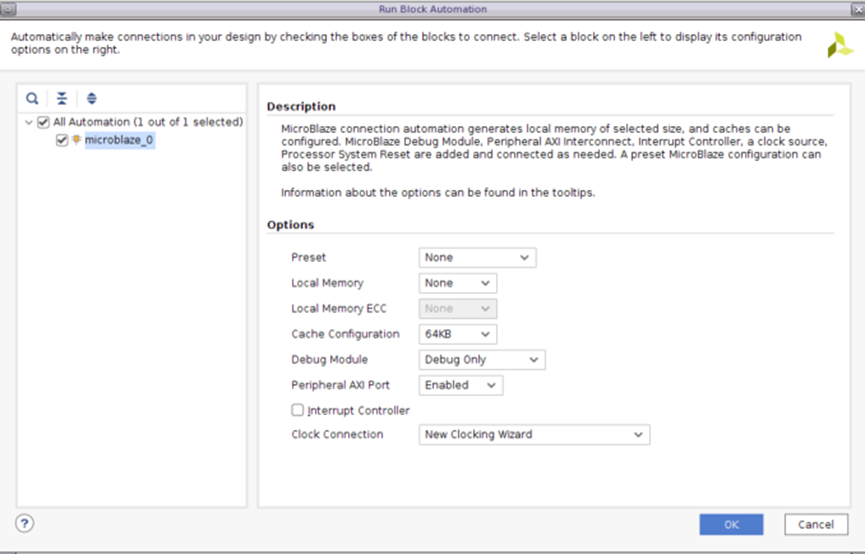

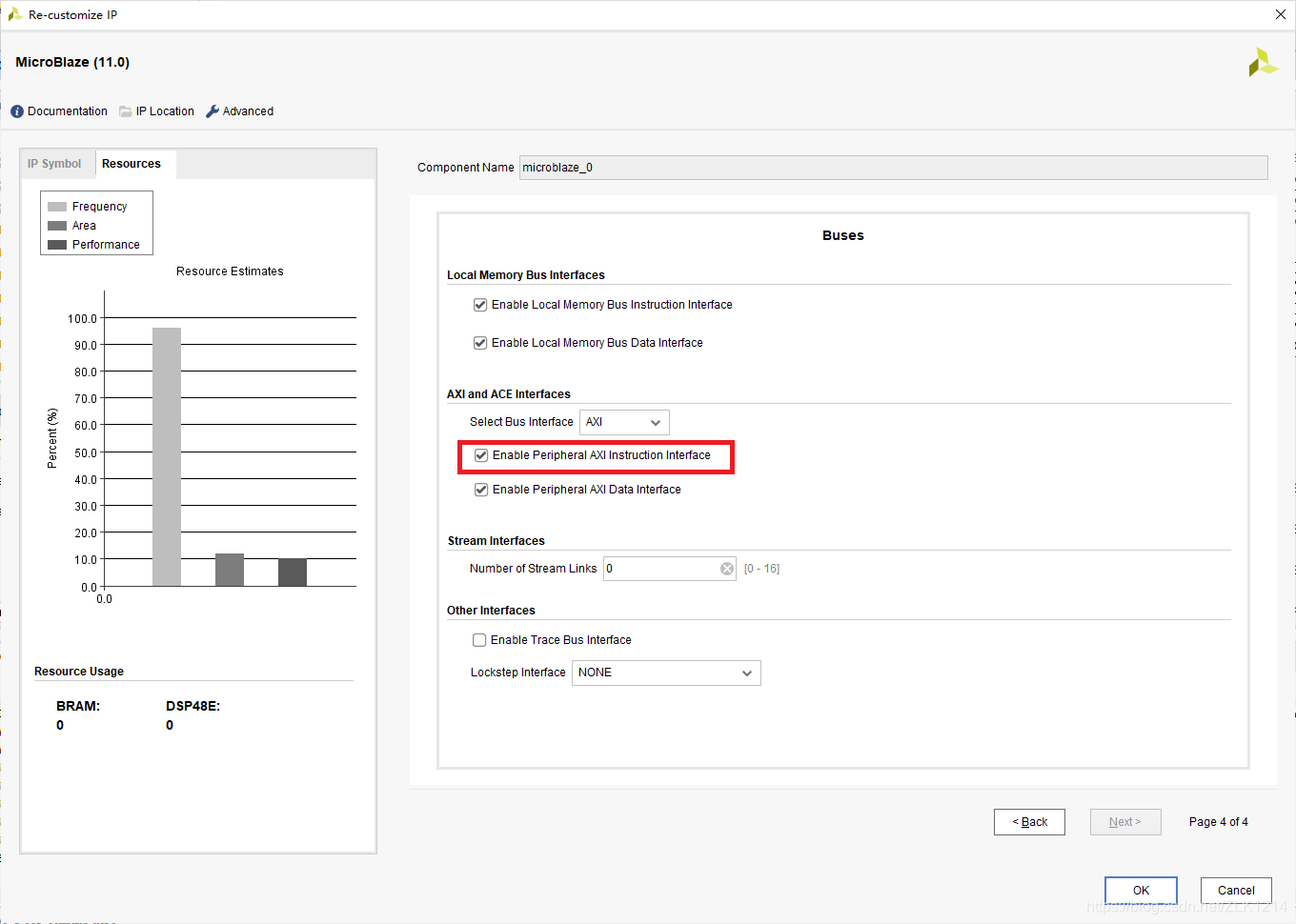

在 Vivado IP integrator 中使用“Block Automation”(块自动化设置)工具来对 MicroBlaze 进行初始配置,如下所示。此处移除了本地存储器,改为使用 64K 高速缓存:

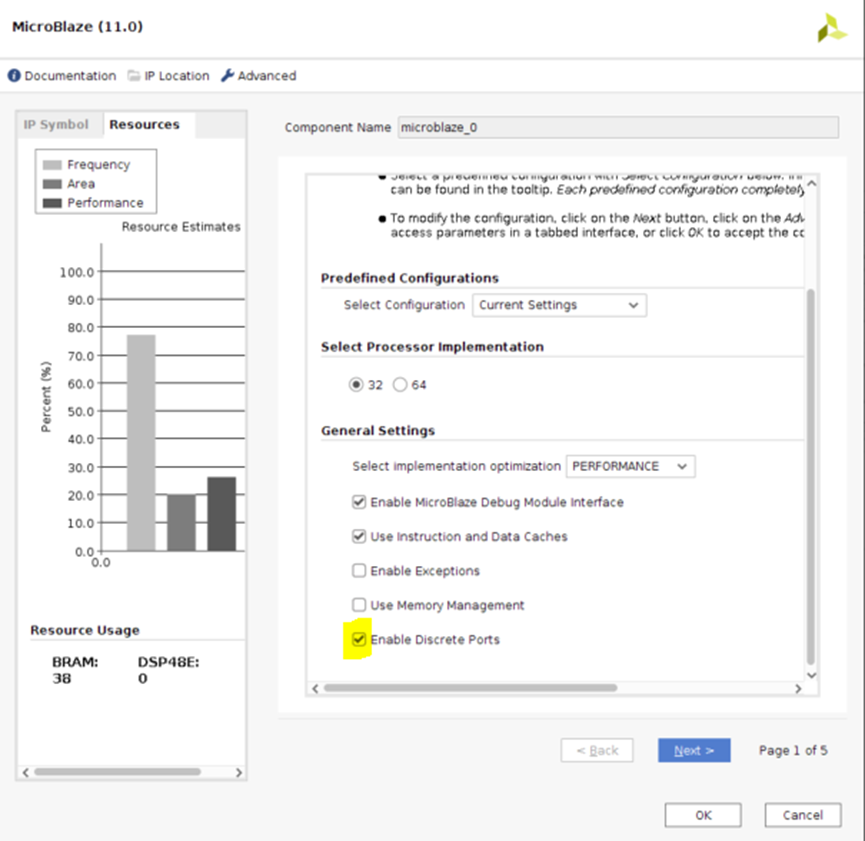

要启用 reset_mode 和 wakeup 管脚,用户需在 MicroBlaze 配置中选中“Enable Discrete Ports”以启用离散端口:

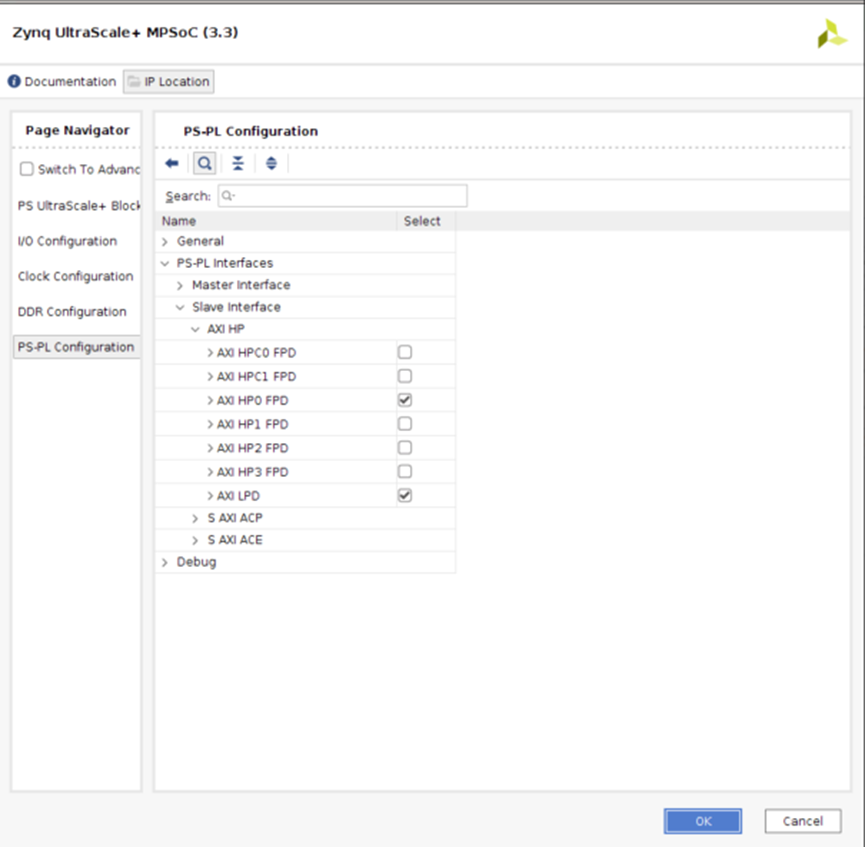

在 Zynq UltraScale PS 配置中,启用两个从端口;一个用于存储器,另一个用于外设:

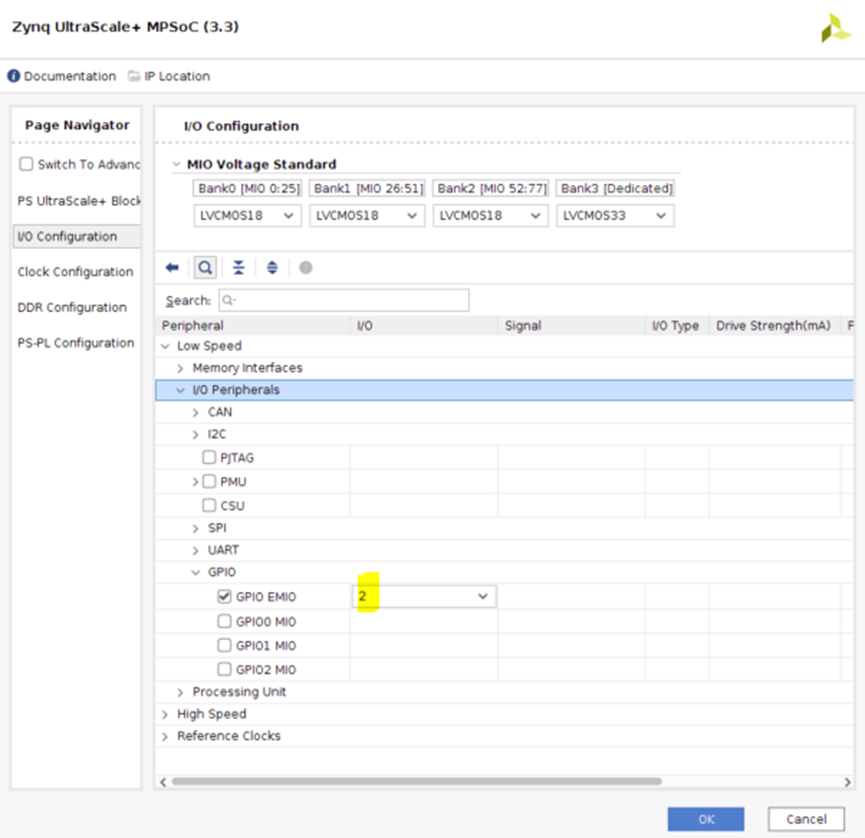

通过 EMIO 启用 GPIO,这样就可以控制 MicroBlaze 的 wakeup 管脚:

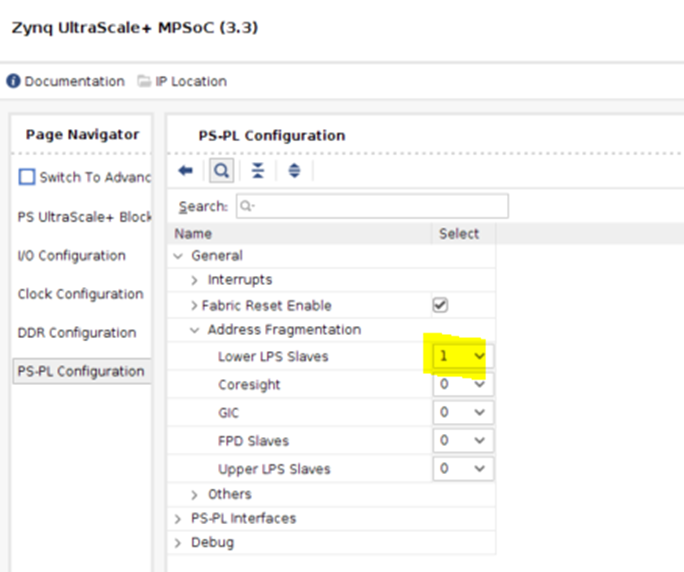

我们还可访问已从 MicroBlaze 启用的所有 Zynq UltraScale IP。为此,请启用“Address Fragmentation”(地址分段):

在上文中我们讨论了复位模式。接下来,MicroBlaze 将保持复位状态,直至我们准备就绪为止。

要使 MicroBlaze 保持复位,可以使用 IP 目录中的“Constant IP”:

最后,连接 GPIO 和 Constant IP:

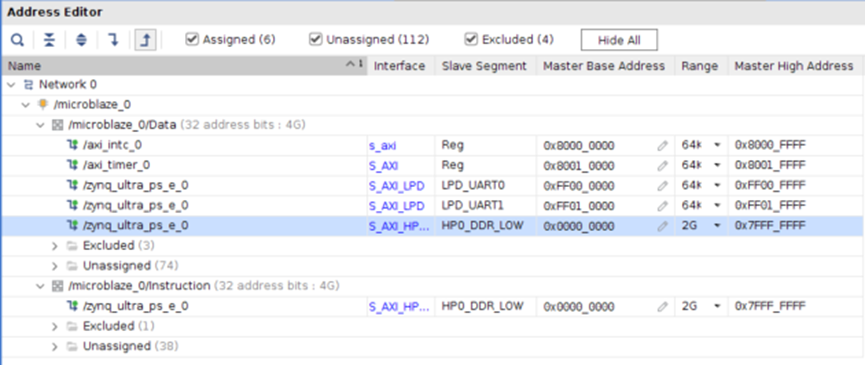

MicroBlaze 地址映射如下所示:

用户可以右键单击地址段,在地址映射中添加或排除地址段。

此操作适用于硬件配置。我们可以使用“Generate the Output Products”(生成输出文件)、“Create the HDL wrapper”(创建 HDL 封装文件)和“Generate the Bitstream”(生成比特流),然后导出硬件。

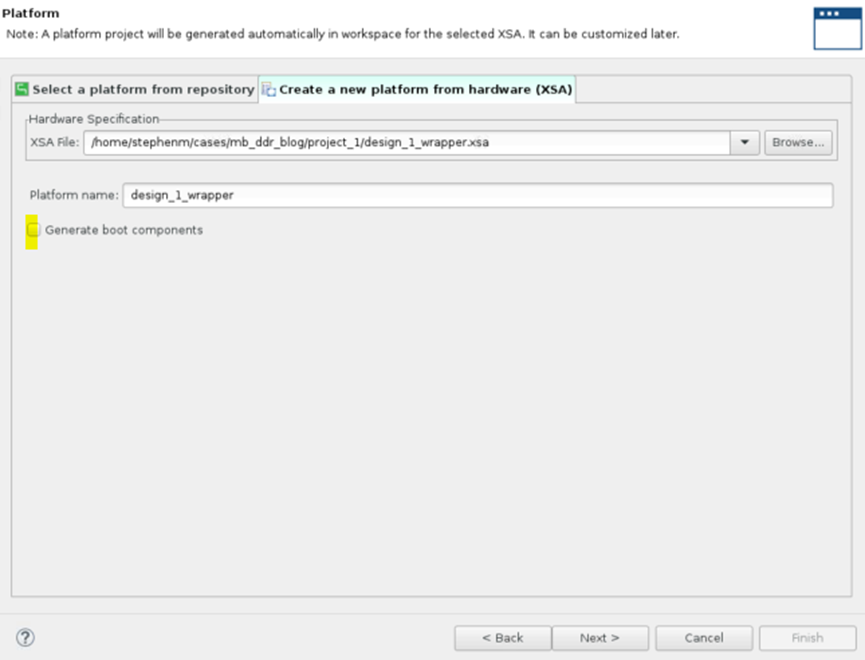

这将生成 XSA 以供在 Vitis 中用于生成我们的软件。

创建软件:

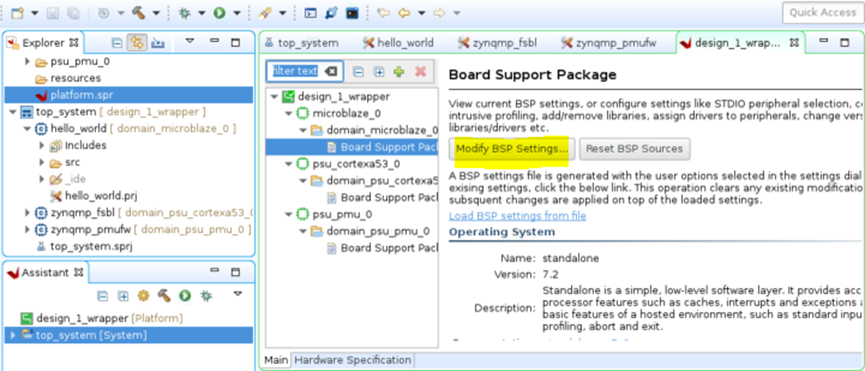

Vitis IDE 可用于生成 MicroBlaze 应用。Vitis 还将自动创建启动镜像,包括 FSBL 和 PMUFW。

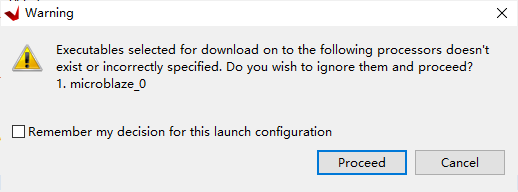

但由于我们想要从 FSBL 控制 GPIO EMIO,因此我们选择不使用工具来生成启动镜像。

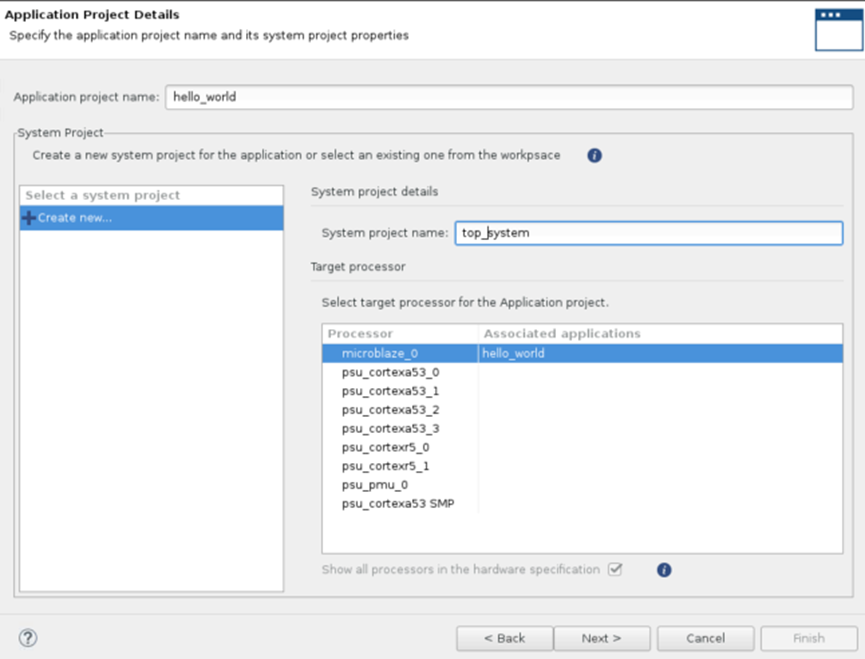

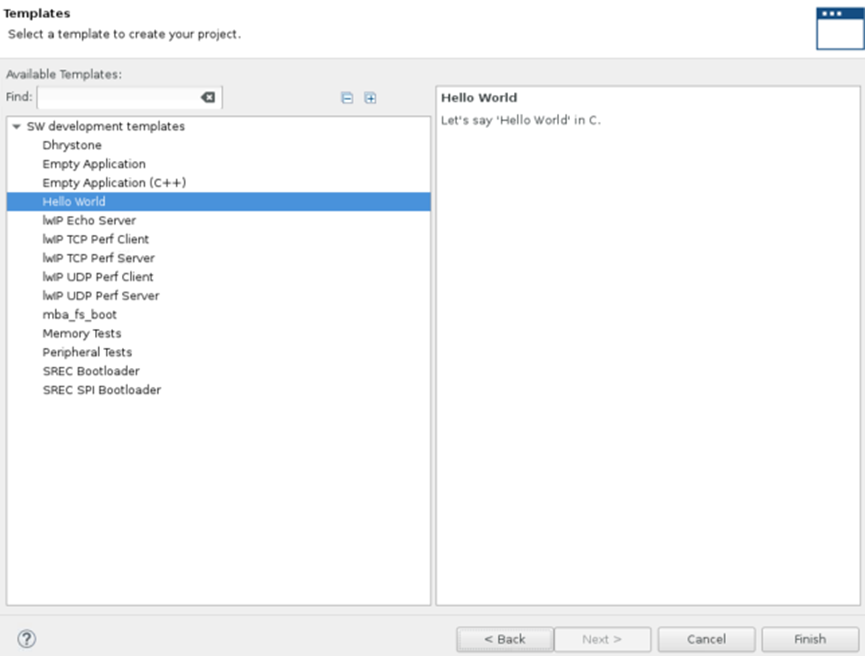

生成 MicroBlaze Hello World 应用:

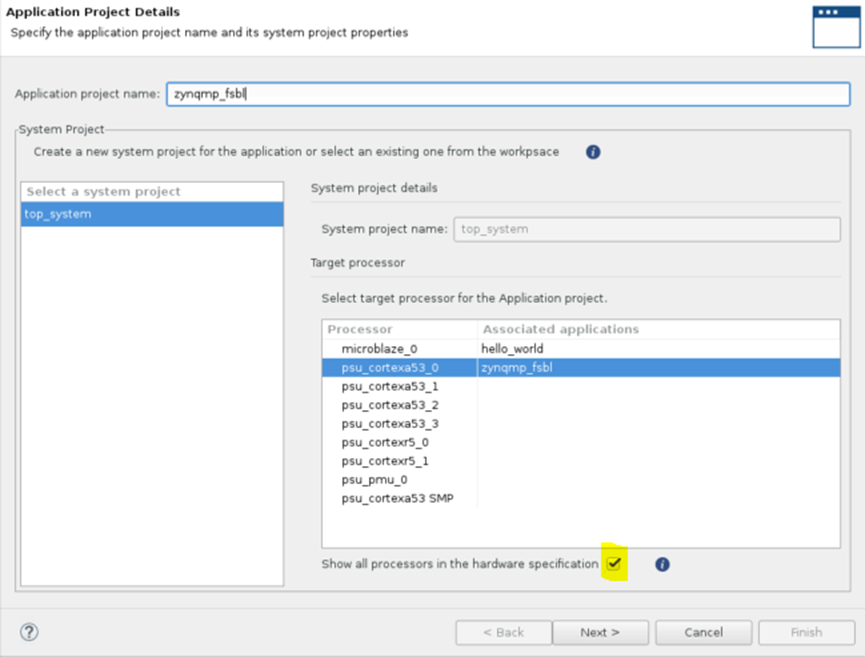

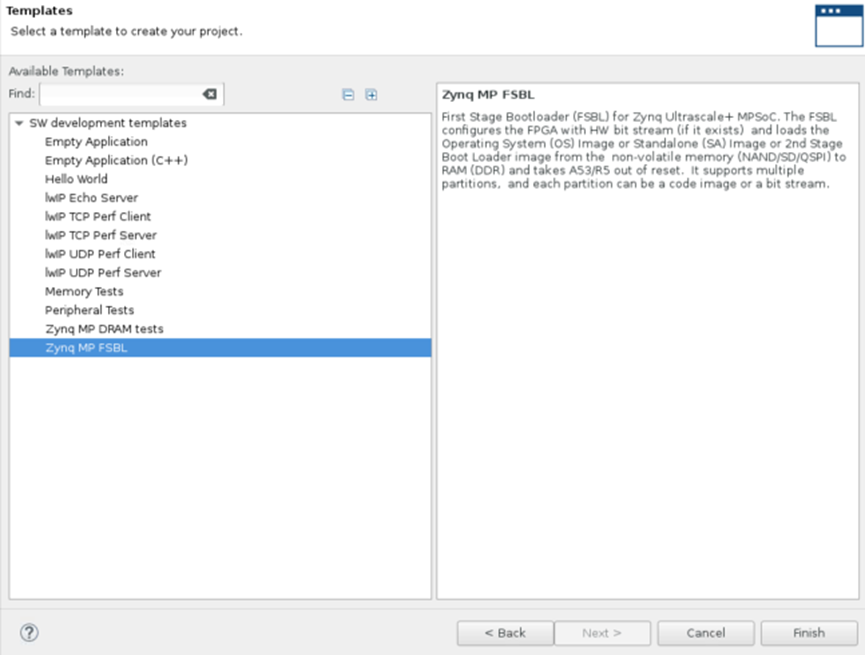

我们可以添加新工程应用,如下所示。例如,对于 Zynq FSBL:

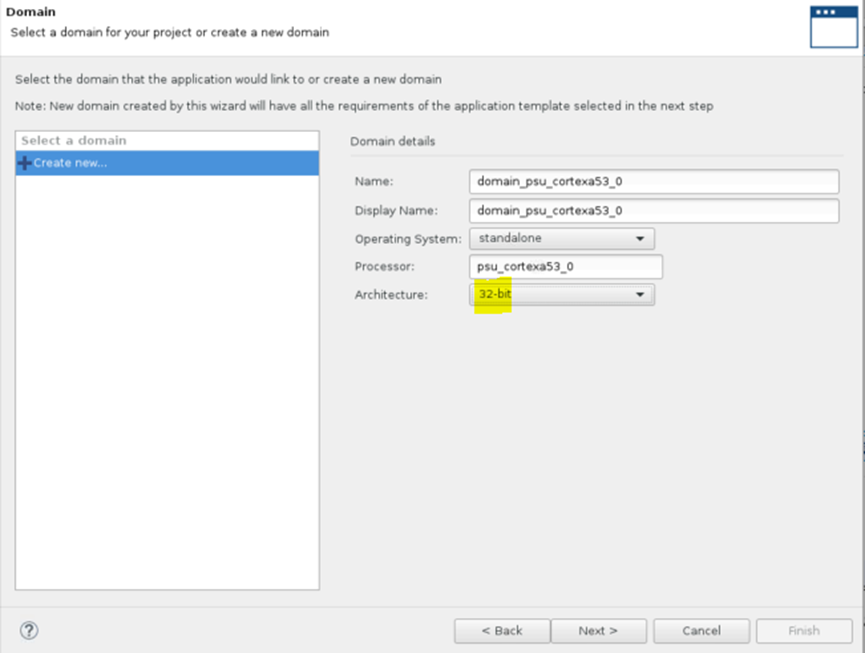

注释:FSBL 不支持 64 位到 32 位交接。因此,由于 MicroBlaze 为 32 位,我们也应将 FSBL 设置为 32 位。

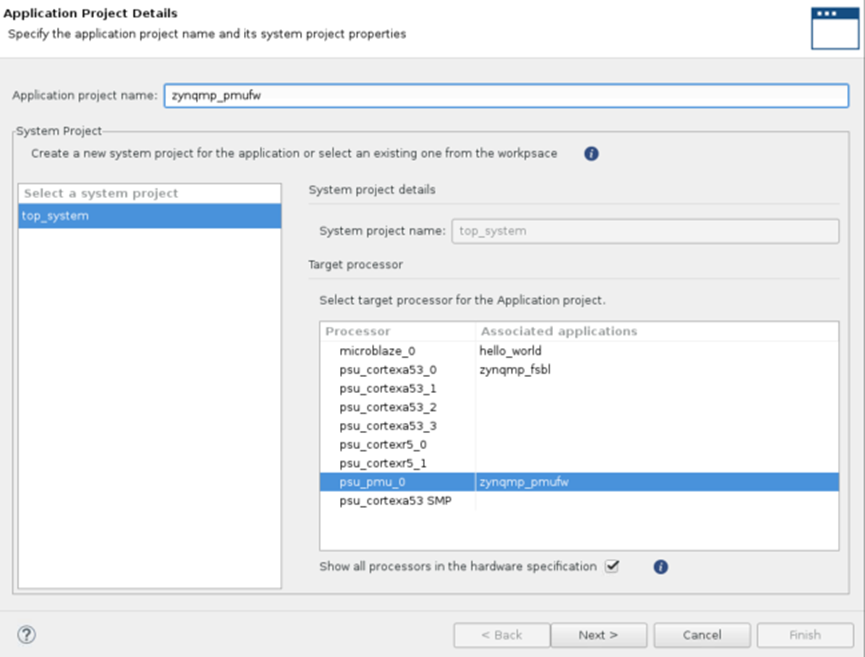

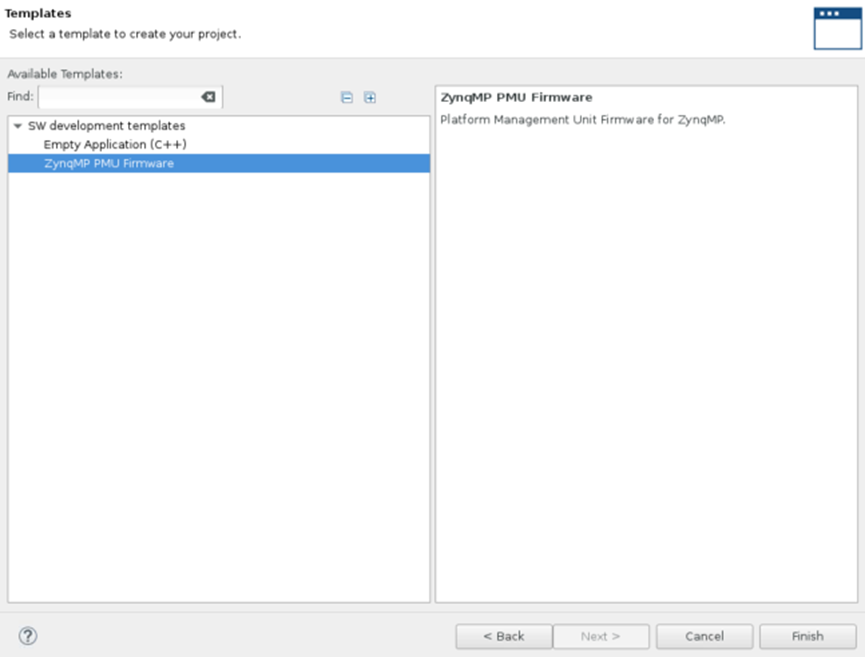

针对 PMUFW 重复上述操作:

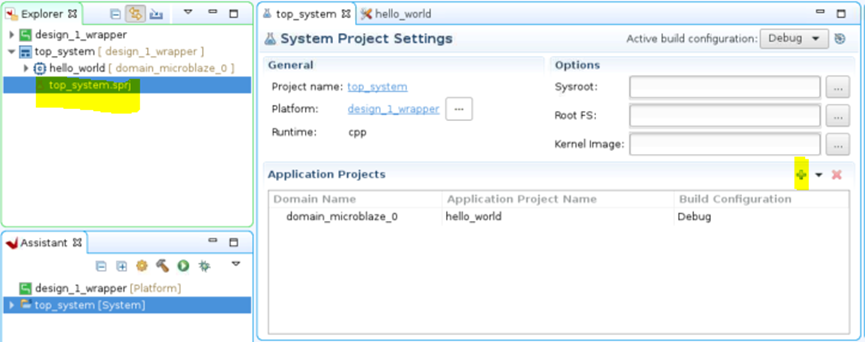

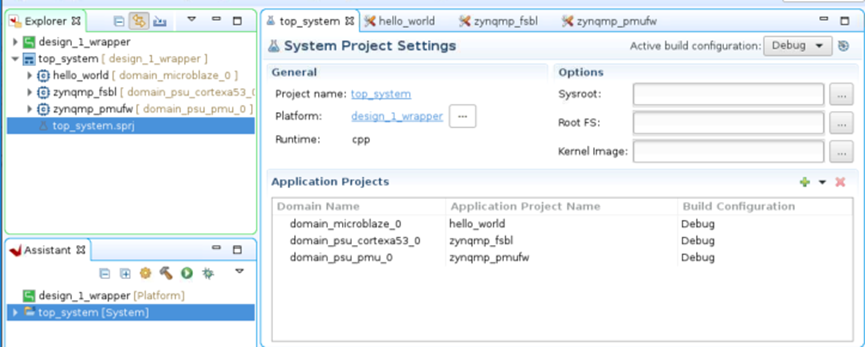

可看到所有应用工程如下所示:

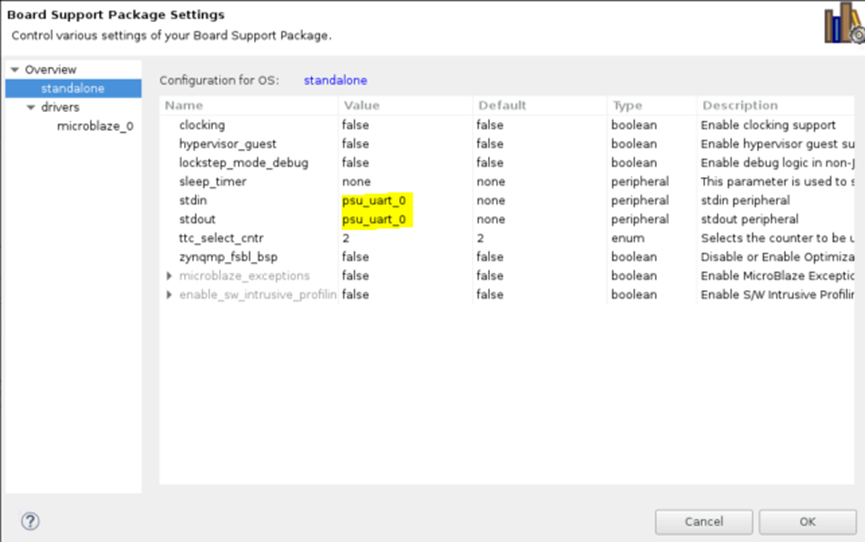

由于我们已将 PS UART 添加到 MicroBlaze 地址映射中,因此可在 BSP 中将其用于 STDIN/OUT。

此处可以看到 MicroBlaze Hello World 连接器:

其布局位置为 DDR 基址 (0x00000000) 处。用户创建启动镜像时,需牢记此地址,以免应用程序发生重叠。

首先,更新 FSBL。

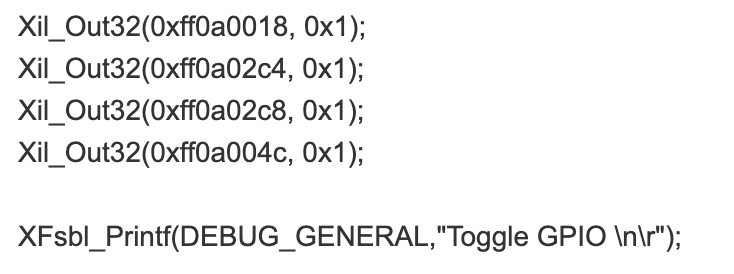

我们可以使用 Xil_Out32 API 来切换 GPIO。

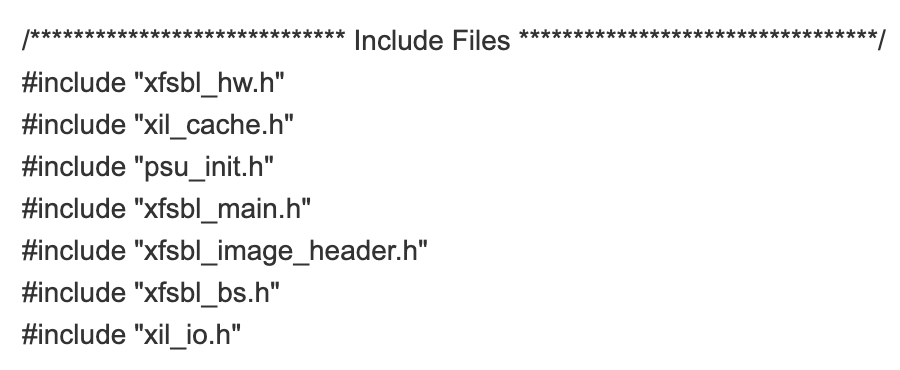

将 xil_io 头文件添加到 xfsbl_handoff.c 文件:

将此添加到 XFsbl_HandoffExit 函数

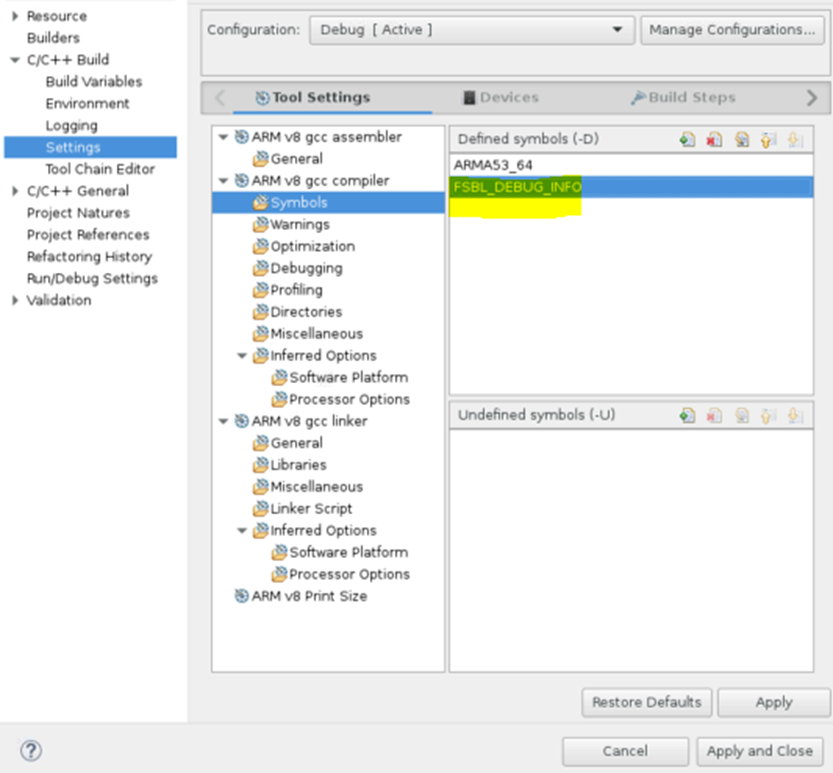

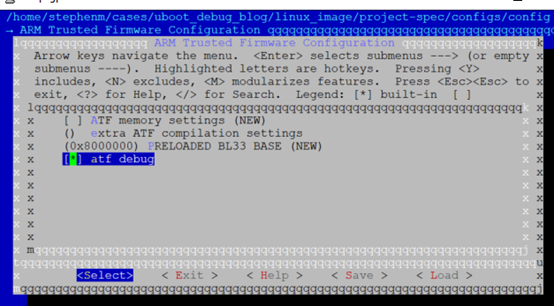

同时启用 FSBL 调试信息:

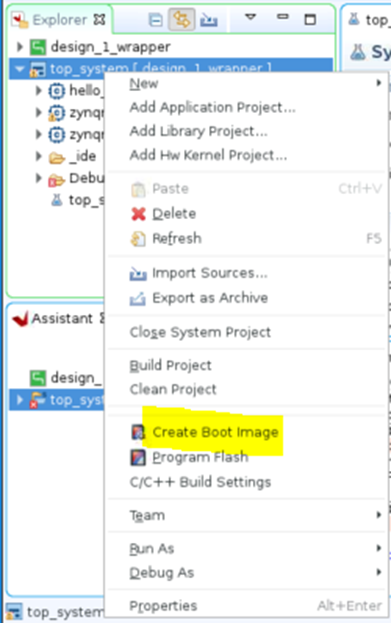

创建启动镜像:

移除 FSBL 和 PMUFW,并使用正确的镜像类型重新添加。

请确保分区镜像顺序正确(使用上下控件来调整其顺序)。

注释:由于此处共享相同 UART,用户可以在 Hello World 应用中布局延迟。

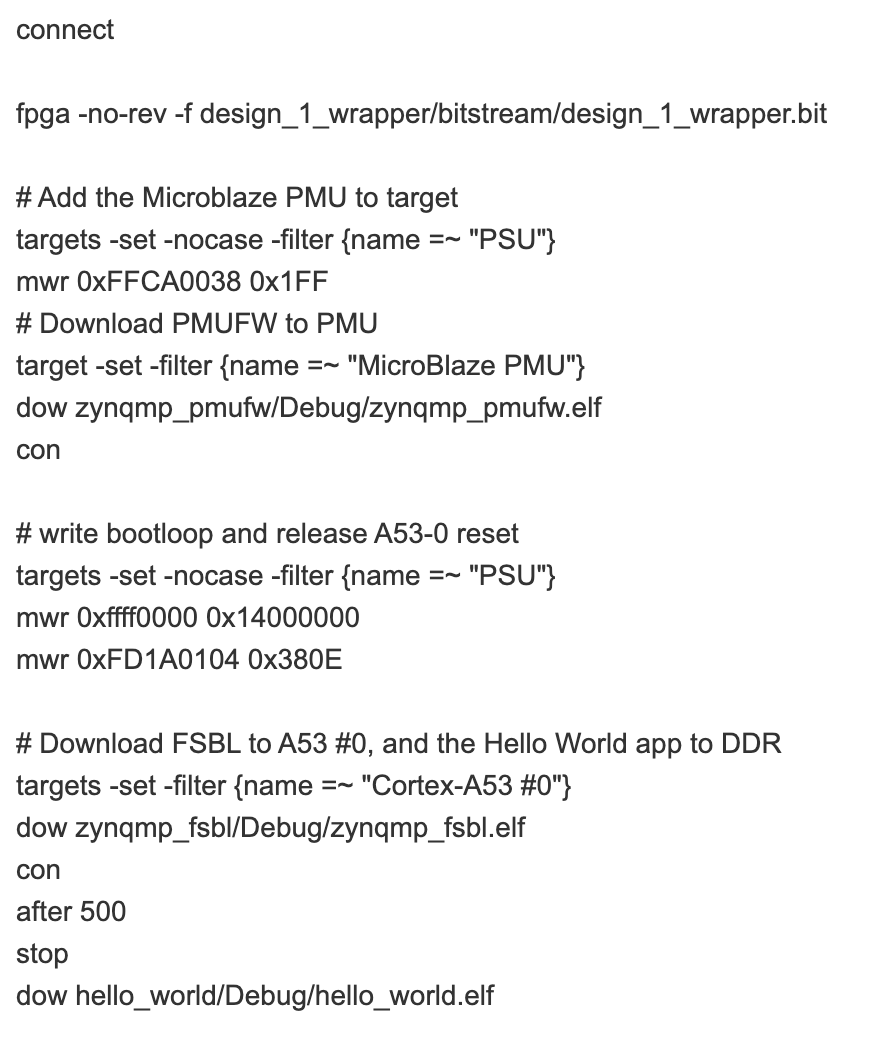

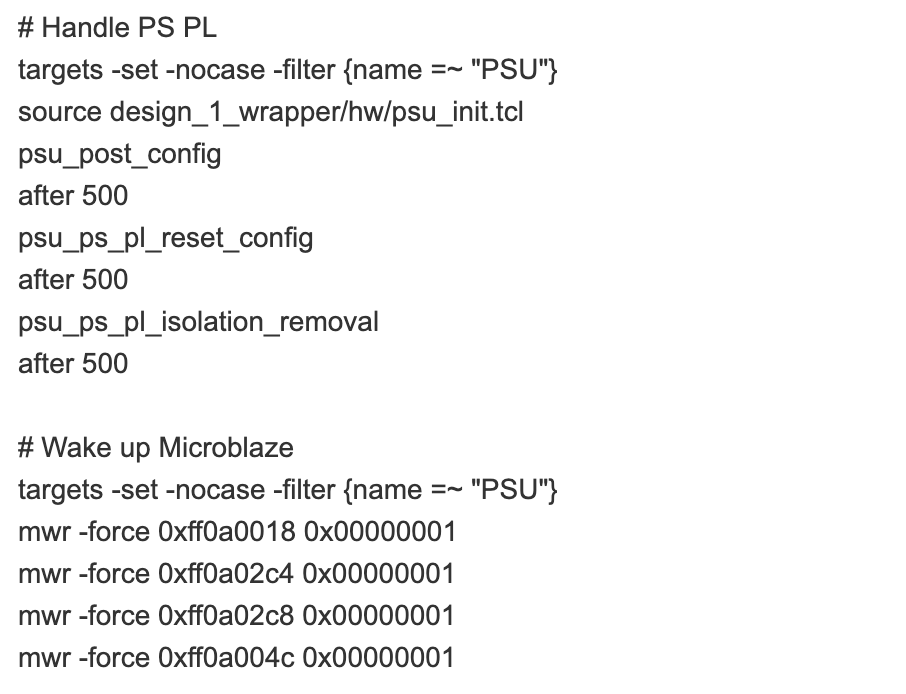

通过 JTAG 进行编程:

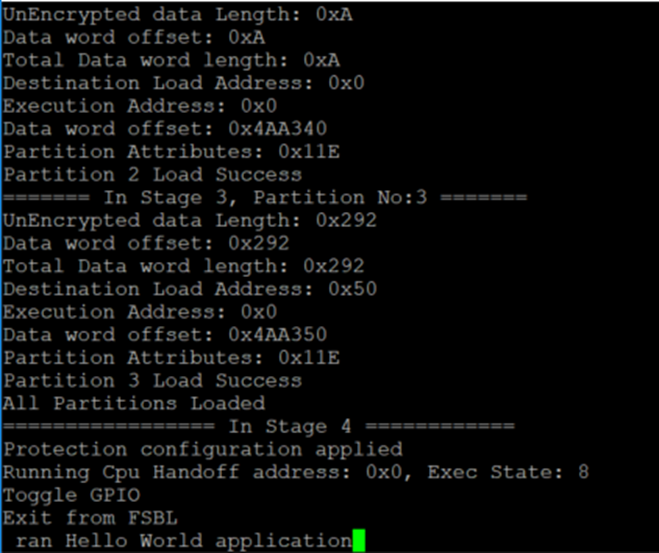

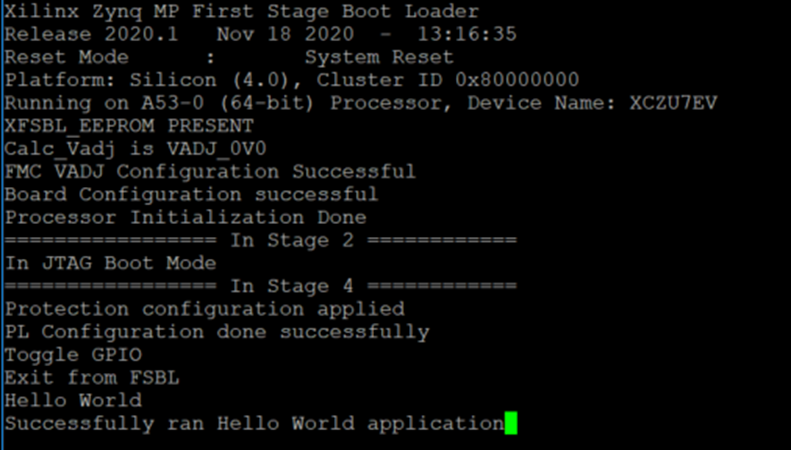

这样可看到如下输出:

审核编辑:刘清

-

存储器

+关注

关注

38文章

7528浏览量

164300 -

DDR

+关注

关注

11文章

715浏览量

65496 -

微处理器

+关注

关注

11文章

2274浏览量

82743 -

PSU

+关注

关注

0文章

43浏览量

11916

原文标题:【Vivado那些事儿】在Vitis中通过 PSU DDR 执行 MicroBlaze 应用

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MicroBlaze串口设计

Vitis2023.2使用之—— updata to Vitis Unified IDE

DDR3 SDRAM的简单代码如何编写

使用Vitis 在EBAZ4205(ZYNQ)矿机上实现"Hello World!"

请问如何通过MicroBlaze访问BRAM?

【正点原子FPGA连载】第一章MicroBlaze简介--摘自【正点原子】达芬奇之Microblaze 开发指南

使用Vitis HLS创建属于自己的IP相关资料分享

PYNQ中MicroBlaze程序文件的加载过程

怎么在Vitis中设定Kernel的频率?

Xilinx Vitis 2020.1里面MicroBlaze软核的sleep函数卡死的问题

在Vitis中调试ARM可信固件和U-boot

在Vitis中通过PSU DDR执行MicroBlaze应用

在Vitis中通过PSU DDR执行MicroBlaze应用

评论