数据路径和时钟路径

reg2reg路径约束的对象是源寄存器(时序路径的起点)和目的寄存器(时序路径的终点)都在FPGA内部的路径。如图1所示,FPGA内部圈起来的部分是从一个寄存器到另一个寄存器的数据路径,他们共用一个时钟(当然也有不共用一个时钟的reg2reg路径,这种路径的分析会复杂一些,本节我们只探讨同时钟源的时序路径)。

对于reg2reg路径,我们只要告诉FPGA的编译工具它们的时钟频率(或时钟周期),那么时序设计工具通常就“心领神会”的将时钟周期、建立时间和保持时间等相关参数代入特定的公式后,计算出这条reg2reg的路径允许的延时范围,并以此为目标进行布局布线。

图1 reg2reg路径模型

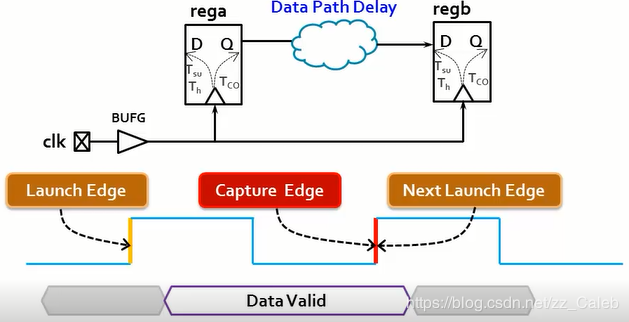

如图2所示,reg2reg模型中的数据路径(datapath)和时钟路径(clock path)清晰明了。所谓数据路径,就是数据在整个传输起点到传输终点所经过的路径;所谓时钟路径,则是指时钟从源端到达源寄存器和目的寄存器的路径。相比于数据路径的“华山一条路”,时钟路径通常由时钟源到源寄存器和时钟源到目的寄存器两条路径组成。

图2 reg2reg的数据路径和时钟路径

数据到达路径和数据需求路径

如图3所示,为了便于后续的时序余量分析和计算,我们提出了数据到达路径(data arrival path)和数据需求路径(data required path)的概念。数据到达路径,是指数据在两个寄存器间传输的实际路径,由此路径可以算出数据在两个寄存器间传输的实际时间;数据需求路径,则是指为了确保稳定、可靠且有效的传输(即满足相应的建立时间和保持时间要求),数据在两个寄存器间传输的理论所需时间的计算路径。

从图2.11的示意可以看到,两条路径的传输起点都是时钟源,传输终点都是目标寄存器。数据到达路径包括了数据路径和一条时钟路径(时钟源到源寄存器),这两条路径的总延时就是数据到达时间。而数据需求路径则只有一条从时钟源到目的寄存器的时钟路径,在进行数据需求时间计算时,应结合寄存器的建立时间和保持时间进行计算。

图3 reg2reg的数据到达路径和数据需求路径

-

FPGA

+关注

关注

1664文章

22509浏览量

639555 -

寄存器

+关注

关注

31文章

5620浏览量

130455 -

时序

+关注

关注

5文章

411浏览量

39020 -

时钟源

+关注

关注

0文章

113浏览量

16826

发布评论请先 登录

FPGA的约束、时序分析的概念详解

如何寻找时序路径的起点与终点

FPGA时序约束理论篇之时序路径与时序模型

详解时序路径的相关概念

详解时序路径的相关概念

评论