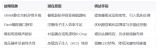

集成电路(Integrated Circuit,简称IC)芯片的三大测试环节包括前端测试、中间测试和后端测试。

前端测试主要是指芯片制造过程中的测试,包括晶圆切割、分选、探针测量等检验。其中,晶圆切割是将已经加工好的晶圆切割成单个芯片,以便进行下一步的测试;分选是将芯片按照质量等级分类,筛选出不合格品;探针测量则是通过在芯片表面上使用探针测量器来验证芯片是否符合规格。

中间测试主要是指在集成电路生产过程的中间阶段对芯片进行的测试,包括逻辑功能测试、时序测试和参数测试等。其中,逻辑功能测试是测试芯片内部的逻辑门电路是否按照设计规范正常工作;时序测试是测试芯片内各个信号线路的延迟时间是否符合规定;参数测试则是测试芯片的性能指标,例如功耗、噪声等。

后端测试则是在芯片封装之后对芯片进行的测试,包括封装测试、可靠性测试和成品测试等。其中,封装测试是测试芯片封装的质量和可靠性;可靠性测试是测试芯片在特定环境下的可靠性,例如高温、低温、湿度等;成品测试则是测试芯片是否符合规格,并对其进行功能验证。

审核编辑黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

本文介绍了集成电路开发中的器件调试环节,包括其核心目标、关键技术与流程等内容。

![的头像]() 发表于

发表于 03-01 14:29

•158次阅读

集成电路IC,宛如现代科技王国中的 “魔法芯片”,虽体积微小,却蕴含着改变世界的巨大能量。捷多邦小编今天与大家聊聊集成电路IC。

![的头像]() 发表于

发表于 01-07 15:33

•170次阅读

测量对于确定IC的EMC特性是必要的。只有准确了解IC的EMC特性,才能在生产前采取有效的预防措施,提高产品的抗ESD能力和EMC性能,避免后期因ESD干扰导致的产品故障和成本增加等问题集成电路ESD

![的头像]() 发表于

发表于 12-23 09:53

•614次阅读

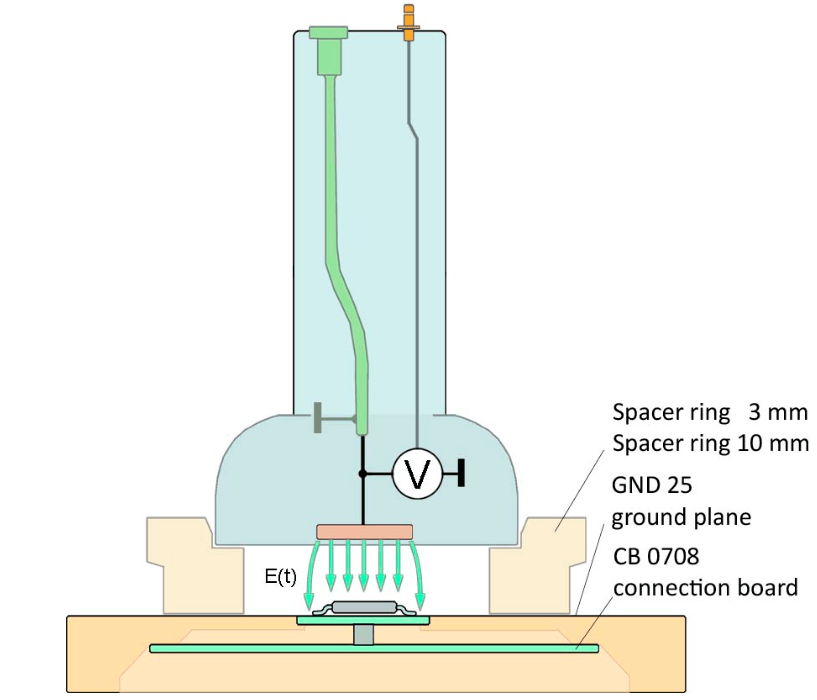

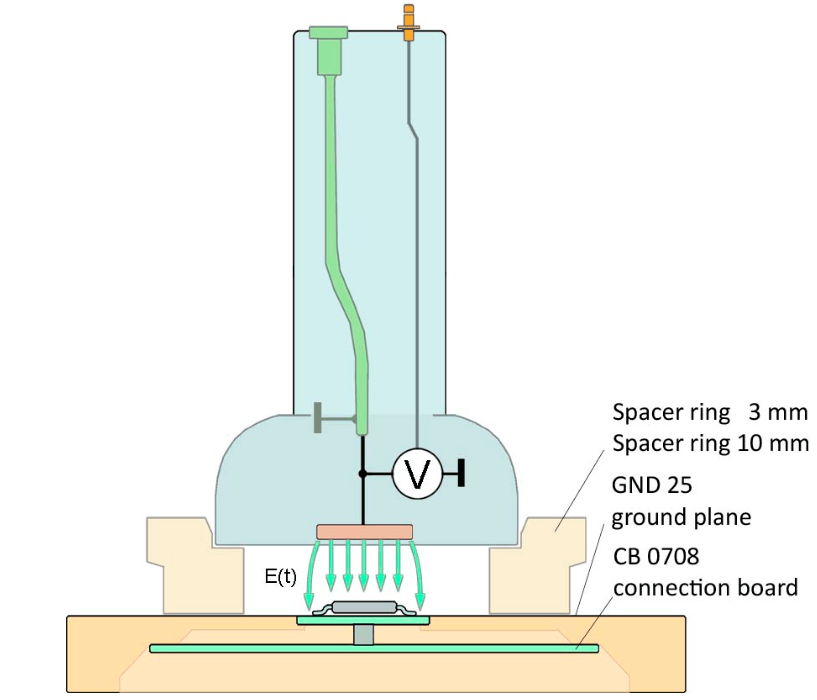

和成本增加等问题 。 三、集成电路ESD 测试与分析 1、测试环境与电场产生 图5 使用 ESD 发生器的测量设置l 测试环境,

![的头像]() 发表于

发表于 12-20 09:14

•365次阅读

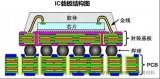

裸芯片(DIE)与印刷电路板 (PCB)之间信号的载体, 是封装测试环节中的关键,它是在 PCB 板的相关技术基础上发展而来 的,用于建立 IC

![的头像]() 发表于

发表于 12-09 10:41

•1367次阅读

ASIC集成电路与通用芯片在多个方面存在显著差异。以下是对这两者的比较: 一、定义与用途 ASIC集成电路 :ASIC(Application-Specific Integrated Circuit

![的头像]() 发表于

发表于 11-20 15:56

•1350次阅读

集成电路的测试是确保其质量和性能的重要环节。以下是关于集成电路测试方法与工具的介绍: 一、集成电路

![的头像]() 发表于

发表于 11-19 10:09

•759次阅读

集成电路,又称为IC,按其功能结构的不同,可以分为模拟集成电路、数字集成电路和数/模混合集成电路三

![的头像]() 发表于

发表于 10-18 15:08

•1675次阅读

设计、制造、应用和性能方面有着显著的差异。 单片集成电路(IC) 定义 单片集成电路是指在一个单一的半导体芯片(如硅片)上集成了多个电子元件

![的头像]() 发表于

发表于 09-20 17:20

•2347次阅读

随着半导体技术的快速发展,集成电路(IC)的复杂性和集成度不断提高,对测试技术的要求也日益增加。深度学习算法作为一种强大的数据处理和模式识别工具,在

![的头像]() 发表于

发表于 07-15 09:48

•1336次阅读

IC测试,即集成电路测试,是集成电路设计和制造过程中的一个重要环节。它主要通过对

![的头像]() 发表于

发表于 07-10 14:45

•3046次阅读

据浦口经开区官微消息,近日,位于浦口经济开发区的伟测集成电路芯片晶圆级及成品测试基地项目的道路和绿化施工进入收尾阶段,项目已正式启动竣工验收工作。 据悉,伟测集成电路

![的头像]() 发表于

发表于 05-28 15:50

•529次阅读

在电子工程的世界里,集成电路(IC)是构建现代电子设备不可或缺的基础元件。它们按照功能和设计的特定性大致分为专用集成电路(ASIC)和通用集成电路两类。

![的头像]() 发表于

发表于 04-07 15:45

•1812次阅读

芯片,又称微电路(microcircuit)、微芯片(microchip)、集成电路(英语:integrated circuit, IC)。

![的头像]() 发表于

发表于 04-02 16:13

•5497次阅读

电子发烧友网站提供《单芯片 集成电路IC 转换器PT2399数据手册.pdf》资料免费下载

发表于 03-28 15:02

•3次下载

集成电路IC芯片的三大测试环节

集成电路IC芯片的三大测试环节

评论