前言

随着数字电路高带宽、高速率发展,反射、串扰、抖动等信号完整性问题愈加严重,包含PCB传输线、过孔、连接器、线缆在内的所有传输链路器件都有着不可忽略的影响。严格控制每个部件的信号质量是确保全链路正常传输的有效手段。然而,对于大批量生产的工厂而言,要在有限的时间内把控所有产品的信号质量、分析产品问题并优化产品性能,这具有非常大的挑战。

本文阐述了利用MeasureExpert工具结合矢量网络分析仪的方法,对可大批量生产的PCB进行快速测试并分析其信号传输性能,能够帮助工程师快速判断产品是否合规,精确分析产品失效原因,进而提高优化效率。

矢量网络分析仪校准

PCB的信号传输特性能否正确表征与测试仪器精度相关。网络分析仪测试过程中的误差主要分为系统误差、随机误差和漂移误差。系统误差主要由仪表内部测试装置的不理想导致,不随时间变化,可重现;随机误差是随时间变化,不可预测的,主要由仪表内部噪声造成;而漂移误差主要是由于温度变化造成的性能漂移。这些误差会严重影响测试精度,因此需要做仪器校准。校准原理即是对已知参数的校准器件进行测量,获得误差模型,基于此误差模型进行计算进而去除误差的影响。

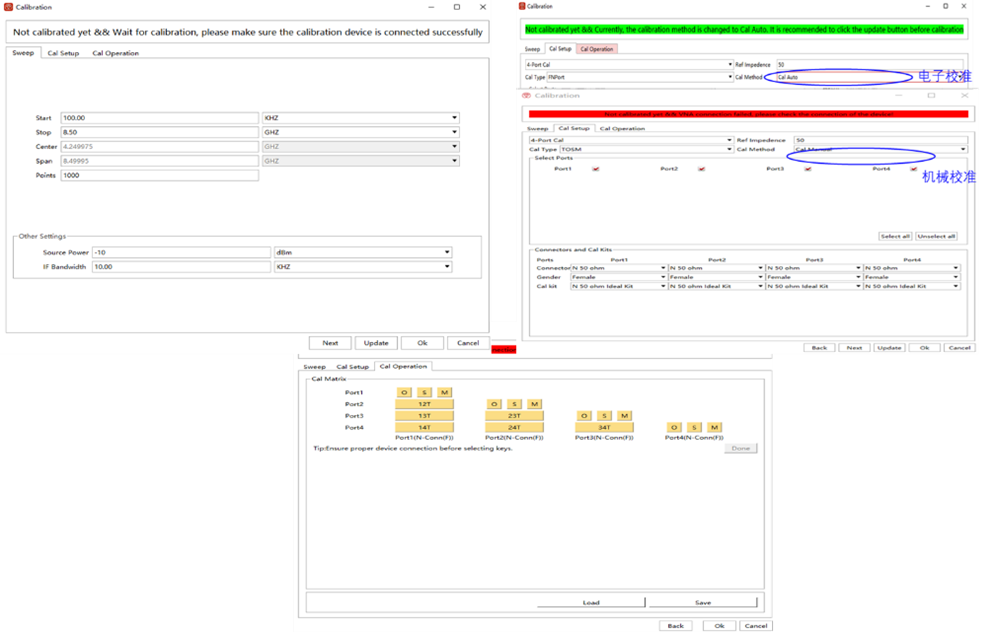

MeasureExpert校准方式包含机械校准和电子校准,校准流程化。

图 1

矢量网络分析仪校准流程

批量化的Delta L测试

1.Delta L去嵌原理

通道的损耗是影响高速I/O信号传输性能的重要因素,损耗测量会引入探针/SMA、焊盘、过孔等影响,这对于管控PCB传输线损耗,分析相关材料属性是一大难题。

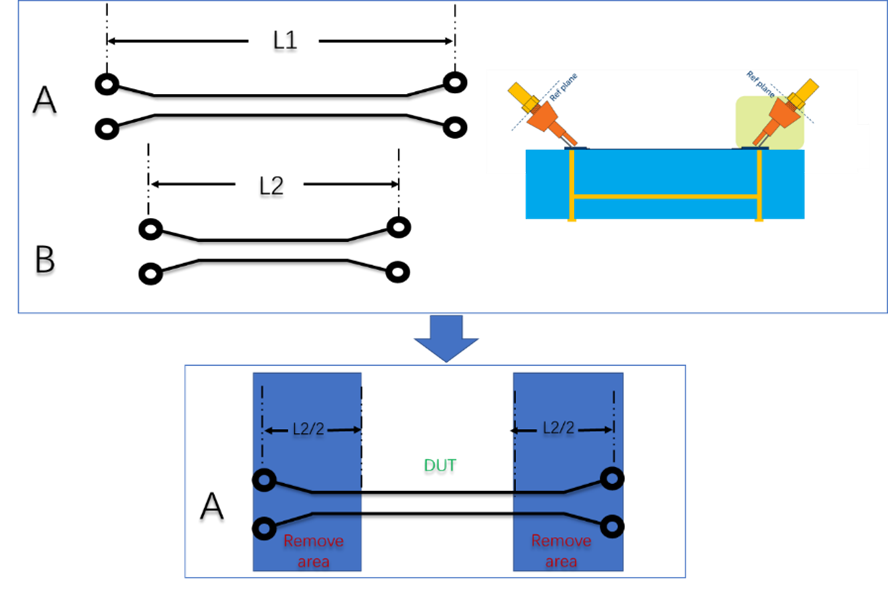

Delta L是一种操作简单、精度高的去嵌方法。首先设计两条只有长度不同的传输线,长度为L2的短线B插损值ILB = IL(fixture)+ ILL2 + IL(fixture),长度为L1的长线A插损值ILA = IL(fixture)+ ILL1 + IL(fixture),然后对长短线做相关数学运算,获得单位长度传输线的插损值:IL / unit= (ILA-ILB) / (L1-L2)。由于过孔会导致多重反射,进而影响去嵌精度问题,因此L2和L1-L2的长度不宜太短。

图2

Delta L去嵌

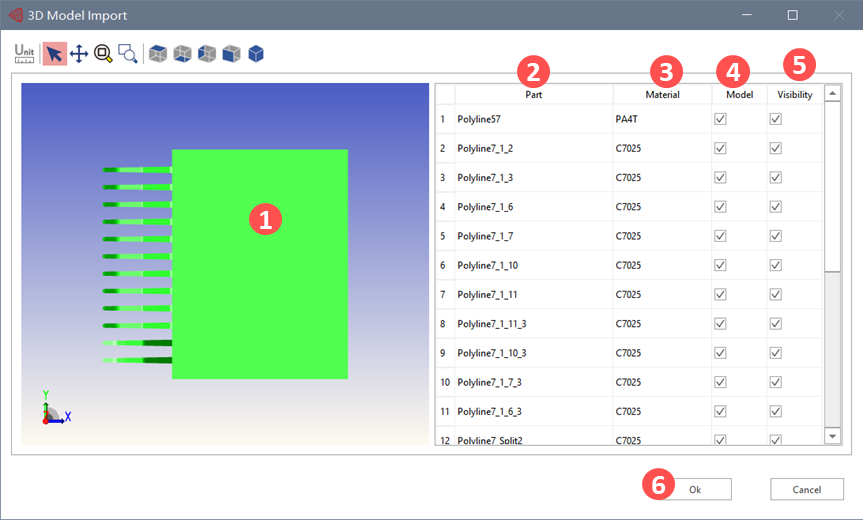

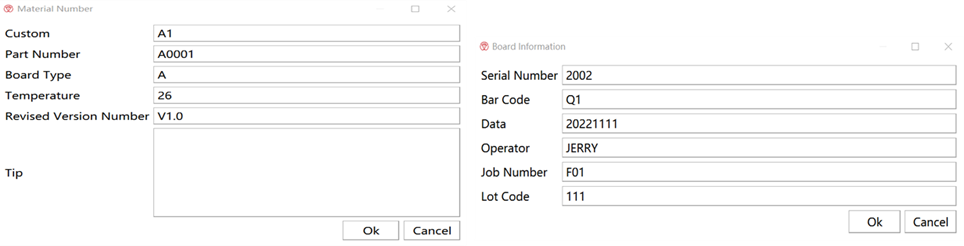

2.Delta L属性配置和产品信息编辑

MeasureExpert支持Intel Delta-L 4.0版本,测试类型可选2L和3L,判决标准可自定义设置,结果将自动判断pass/fail,如图3a。客户信息、产品型号、序列号、批次号、测试温度、操作员信息可依次键入, 如图3b。

图 3a

SAT配置界面

图3b

产品信息编辑

3.Delta L测试结果显示和报告输出

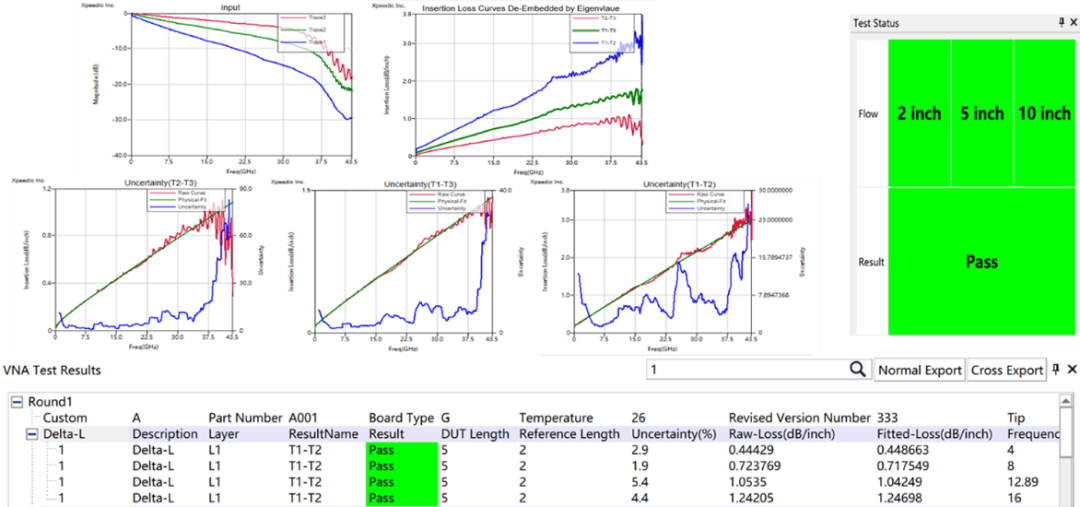

属性配置完成后,快速连接PCB,图4a是3L(2inch,5inch,10inch)的测试结果显示,主要分为3部分。测试曲线分别包含去嵌前损耗、去嵌后损耗、去嵌后每inch的损耗以及对应损耗拟合值和不确定度。测试状态框显示整体结果,若是Fail会显示是由IL还是不确定导致的,本案例结果显示PASS。图4a下方是细节部分,显示各判决频点下IL值、拟合IL值、不确定度、是否pass的结果等。结果可导出csv报告, 如图表4b显示。

图 4a

Delta L测试结果显示

图表 4b

Delta L测试输出报告

批量化的TDR测试

随着速率升高,信号边沿变得更陡,阻抗失配以及反射变得越来越严重。分析信号传输不仅需要关注频域性能,时域也是不可缺少的。

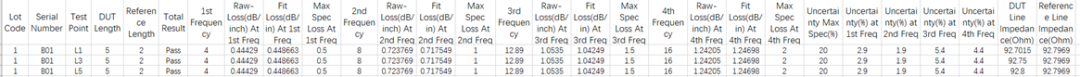

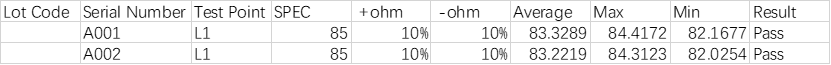

1.TDR属性配置

TDR属性配置如图5所示。首先输入测试的层数,传输线信息;然后配置阻抗判决标准(阻抗基准值、判断范围、取值区间、极值或均值判断)、夹具可选择性去除,对于只关注传输线阻抗而言,建议移除夹具,阻抗判决的取值区间将只覆盖传输线而不会误加入夹具阻抗进行判断,上升沿时间可在TDR option设置。

图 5

TDR属性配置

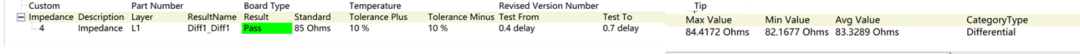

2.TDR测试结果显示和报告输出

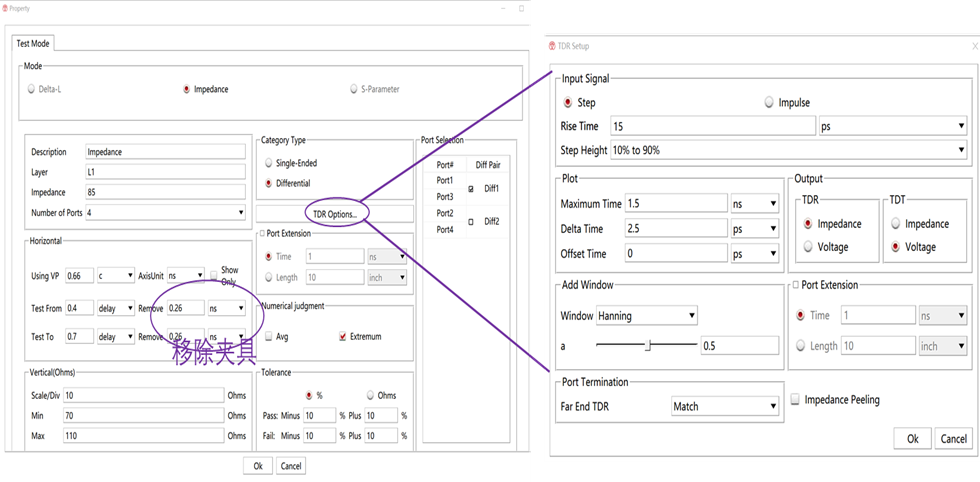

这是上升沿为15ps(10%~90%的)传输线测试结果,红点是起止点,黑点表示移除的位置,从这个结果来看,传输线40%~70%的区间阻抗最大和最小值都满足阻抗85ohm+-10%的要求,因而PASS。

图6a

TDR测试结果

图6b

TDR报告输出

总结

芯和半导体的MeasureExpert工具搭载矢量网络分析仪可实现自动化测试和批量化数据分析,内容覆盖了频域和时域。针对批量化的PCB,本文主要介绍了Delta L测试和TDR测试。Delta L测试连接快速,操作简单,去嵌精度高,结果可得到单位长度传输线损耗值。TDR测试从时域上分析传输线性能,阻抗曲线可清晰显示不同位置阻抗值。整体测试流程化,操作便捷且能节省大量的时间。

关于芯和半导体EDA

芯和半导体提供“半导体全产业链仿真EDA解决方案”,是新一代智能电子产品中设计高频/高速电子组件的重要工具,拥有领先的2.5D/3D Chiplet先进封装设计分析全流程的EDA平台。产品涵盖三大领域::

芯片设计:匹配主流晶圆厂工艺节点,支持定制化PDK构建需求,内嵌丰富的片上器件模型,帮助用户快速精准地实现建模与寄生参数提取。

封装设计:集成多类封装库,提供通孔、走线和叠层的全栈电磁场仿真工具,为2.5D/3DIC先进封装打造领先的统一仿真平台,提高产品开发和优化效率。

系统设计:基于完全自主产权的EDA仿真平台,打通整机系统建模-设计-仿真-验证-测试的全流程,助力用户一站式解决高速高频系统中的信号完整性、电源完整性、热和应力等设计问题。

关于芯和半导体

芯和半导体是一家从事电子设计自动化(EDA)软件工具研发的高新技术企业,以仿真驱动设计,提供覆盖IC、封装到系统的具备完全自主知识产权的全产业链 EDA 解决方案,支持先进工艺与先进封装,致力于赋能和加速新一代高速高频智能电子产品的设计,已在5G、智能手机、物联网、人工智能和数据中心等领域得到广泛应用。

芯和半导体自主创新的下一代集成无源器件IPD平台,以高集成、高性能、小型化为特色,为移动终端、IoT、HPC、汽车电子等客户提供系列集成无源芯片,累计出货量超20亿颗,并被 Yole 评选为全球IPD 滤波器的主要供应商之一。

芯和半导体创建于2010年,运营及研发总部位于上海张江,在苏州、武汉、西安设有研发分中心,在美国硅谷、北京、深圳、成都、西安设有销售和技术支持部门。如欲了解更多详情,敬请访问www.xpeedic.com。

审核编辑:汤梓红

-

pcb

+关注

关注

4417文章

23961浏览量

426061 -

数字电路

+关注

关注

193文章

1668浏览量

83532 -

传输线

+关注

关注

0文章

384浏览量

25568 -

串扰

+关注

关注

4文章

196浏览量

27872

原文标题:【应用案例】如何快速进行 “批量化的PCB测试分析”?

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何进行CAN通信设备的批量老化测试

CAN通信设备如何进行批量高效老化测试

失效分析方法---PCB失效分析

洲明科技表示已经能够批量化生产P0.9MiniLED产品

批量PCB生产和其他电子制造工艺

如何快速进行批量化的PCB测试分析?

如何快速进行批量化的PCB测试分析

如何快速进行批量化的PCB测试分析

评论