实现思路

在实现上,由于bmp除去文件头后也只是把图像流数据按顺序放而已,所以这里

- 先用一个fifo缓存图像数据

- 写一个状态机控制按顺序输出文件头和数据。

- 注意fifo的读写和AXIS之间的握手和控制逻辑。因为看起来fifo是暂存数据的,但可预见fifo应该是有可能周期性空的,因为在每行的结束后tlast都是让valid拉低一个周期,这一小个周期在行多了之后一点会抵消文件头的大小。

生成缓存fifo

声明:

- 命名并不规范

- 可以用原语(xpm)或其他同类型IP生成,这里不多赘述。

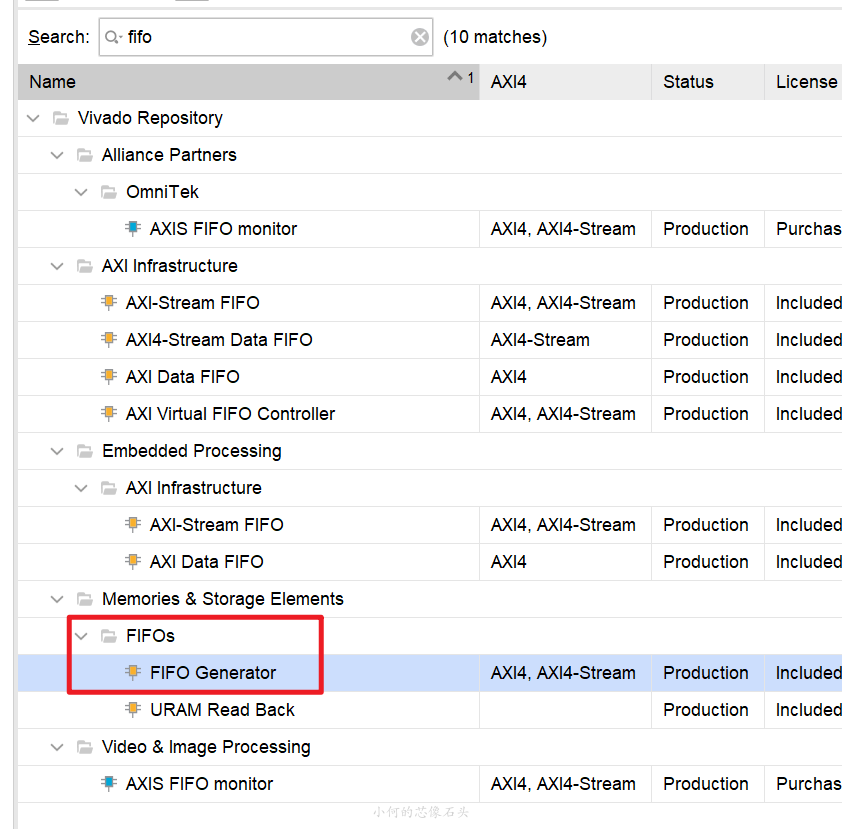

在IP catalog的搜索框中写fifo,选FIFO Generator:

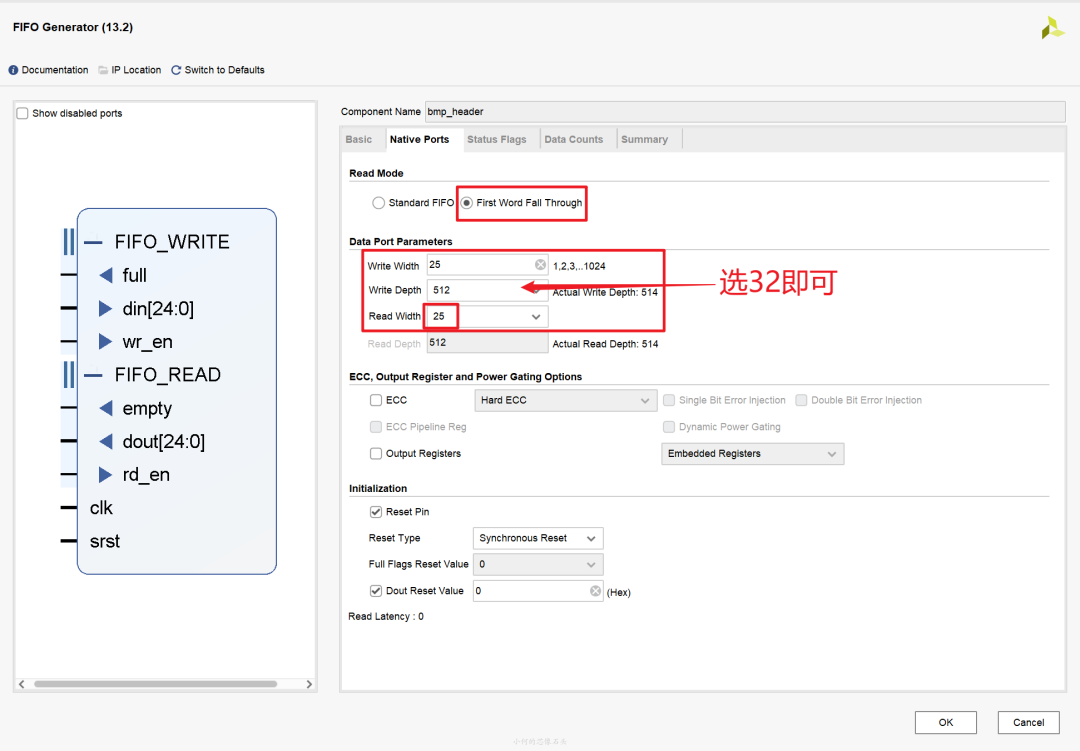

具体按下面设置:

这里注意必须选择First Word Fall Through

选25位是因为,在数据结构上是1tuser + 2*8 data,选择把帧开始标志也丢进fifo可以避免错帧。

总体端口

生成的BMP文件依然以AXIS格式输出,在tb中再以二进制格式写进文件:

module axis2bmp#(

parameter PIC_HEIGHT = 1080,

parameter PIC_WIDTH = 1920

)(

// global signal

input clk_i, // clock

input rst_n_i, // reset

// axi stream (slave) interface signal - > pixel data

input [23:0] s_axis_video_tdata, // DATA

input [0:0] s_axis_video_tvalid, // VALID

output [0:0] s_axis_video_tready, // READY

input [0:0] s_axis_video_tuser, // SOF

input [0:0] s_axis_video_tlast, // EOL

// axi stream (master) interface signal - > bmp

output reg [23:0] m_axis_video_tdata, // DATA

output [ 0:0] m_axis_video_tvalid, // VALID

input [ 0:0] m_axis_video_tready, // (meaningless)

output [ 0:0] m_axis_video_tlast // end of file stream

);

slave端为图像数据,master端为输出BMP文件流,这里需要注意master流中并不处理反压问题(即没有ready信号,懒得加fifo)

fifo接口逻辑

// image pixel fifo dw=24, BRAM cap=512

wire [24:0] bmp_header_din;

wire [0:0] bmp_header_wr;

wire [0:0] bmp_header_full;

wire [0:0] bmp_header_empty;

wire [0:0] bmp_header_rd;

wire [24:0] bmp_header_dout;

bmp_header bmp_header_inst (

.clk(clk_i), // input wire clk

.srst(~rst_n_i), // input wire srst

.din(bmp_header_din), // input wire [23 : 0] din

.wr_en(bmp_header_wr), // input wire wr_en

.rd_en(bmp_header_rd), // input wire rd_en

.dout(bmp_header_dout), // output wire [23 : 0] dout

.full(bmp_header_full), // output wire full

.empty(bmp_header_empty) // output wire empty

);

// pixel fifo assignment

assign bmp_header_din = {s_axis_video_tuser,s_axis_video_tdata};

assign s_axis_video_tready = ~bmp_header_full;

assign bmp_header_wr = s_axis_video_tready && s_axis_video_tvalid;

fifo的读使能放到后面再讲,这里先处理好数据进来就可以了

文件流处理状态机

经典三板斧,不展开

包头数据准备

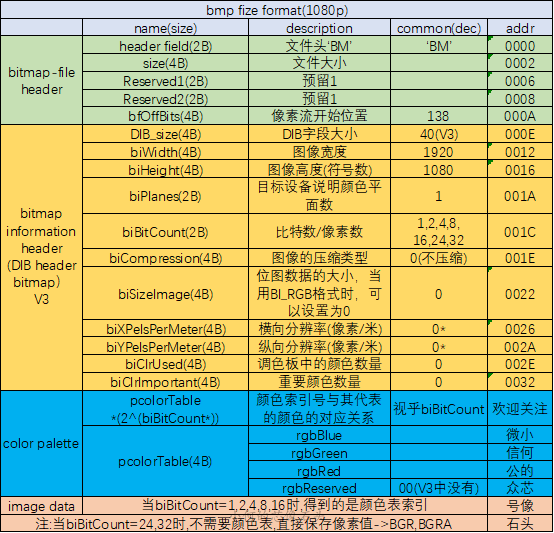

需要搬回第一篇中的BMP文件格式,由于是输出,所以我们就不考虑调色板了:

这里先用一些localparam存起来,(这里考虑大小不变)

//--------------------------写BMP状态机------------------------

// local parameter

localparam [15:0] bfType = 16'h4d42;

localparam [31:0] bfReserved = 32'h0000_0000;

localparam [31:0] biSizeImage = PIC_HEIGHT * PIC_WIDTH * 3;

localparam [31:0] biSizeImage_cnt = PIC_HEIGHT * PIC_WIDTH;

localparam [31:0] bfOffset = 32'd54;

localparam [31:0] bfSize = biSizeImage + bfOffset;

localparam [31:0] biSize = 32'h28;

localparam [31:0] biWidth = PIC_WIDTH;

localparam [31:0] biHeight = PIC_HEIGHT;

localparam [15:0] biPlanes = 16'd1;

localparam [15:0] biBitCount = 16'd24;

localparam [31:0] biCompression = 32'd0;

localparam [127:0] biUseless = 128'd0;

localparam CNT_PIXEL = $clog2(PIC_HEIGHT*PIC_WIDTH);

转移状态

//转移状态

localparam S_WAIT = 3'b001 ; // 等待SOF标记

localparam S_WRITE_HEADER = 3'b010 ; // 写BMP包头

localparam S_WRITE_DATA = 3'b100 ; // 写BMP数据

状态转移变量

//状态转移变量

reg [2:0] state, n_state; // 状态寄存器

reg [4:0] header_cnt; // 包头计数器

reg [CNT_PIXEL-1:0] pixel_cnt; // 像素计数器

wire frame_start = bmp_header_dout[24]; // SOF flag

wire write_header_done = (header_cnt == 5'd17); // 18 -1 - > 18*3

wire write_pixel_done = (pixel_cnt == biSizeImage_cnt -1'b1);

这里需要注意 : 两个状态只由计数器指定跳转

状态转移

//状态机初始化

always @ (posedge clk_i) begin

if(~rst_n_i)

state <= S_WAIT;

else

state <= n_state;

end

状态机 状态转移

always @ (*) begin

case(state)

S_WAIT :

if(frame_start)

n_state = S_WRITE_HEADER;

else

n_state = S_WAIT;

S_WRITE_HEADER:

if(write_header_done)

n_state = S_WRITE_DATA;

else

n_state = S_WRITE_HEADER;

S_WRITE_DATA:

if(write_pixel_done)

n_state = S_WAIT;

else

n_state = S_WRITE_DATA;

default:

n_state = S_WAIT;

endcase

end

写BMP包头 处理逻辑

这里直接按照文件格式,用计数器怼进去进行:

always @(posedge clk_i or negedge rst_n_i) begin

if (~rst_n_i)

header_cnt <= 5'd0;

else if(state == S_WRITE_HEADER && header_cnt < 5'd17)

header_cnt <= header_cnt + 1'd1;

else

header_cnt <= 5'd0;

end

在数据上,可参考(注意数据以小端输出):

case (header_cnt)

5'd0 :

m_axis_video_tdata = {bfSize[0+:8], bfType};

5'd1 :

m_axis_video_tdata = bfSize[8+:24];

5'd2 :

m_axis_video_tdata = bfReserved[0 +:24];

5'd3 :

m_axis_video_tdata = {bfOffset[0+:16],bfReserved[24+:8]};

5'd4 :

m_axis_video_tdata = {biSize[0+:8], bfOffset[16+:16]};

5'd5 :

m_axis_video_tdata = biSize[8+:24];

5'd6 :

m_axis_video_tdata = biWidth[0+:24];

5'd7 :

m_axis_video_tdata = {biHeight[0+:16],biWidth[24+:8]};

5'd8 :

m_axis_video_tdata = {biPlanes[0+:8],biHeight[16+:16]};

5'd9 :

m_axis_video_tdata = {biBitCount[0+:16],biPlanes[8+:8]};

5'd10 :

m_axis_video_tdata = biCompression[0+:24];

5'd11 :

m_axis_video_tdata = {biSizeImage[0+:16],biCompression[24+:8]};

5'd12 :

m_axis_video_tdata = {biUseless[0+:8], biSizeImage[16+:16]};

5'd13 :

m_axis_video_tdata = biUseless[8+:24];

5'd14 :

m_axis_video_tdata = biUseless[32+:24];

5'd15 :

m_axis_video_tdata = biUseless[56+:24];

5'd16 :

m_axis_video_tdata = biUseless[80+:24];

5'd17 :

m_axis_video_tdata = biUseless[104+:24];

default:

m_axis_video_tdata = 24'heeeeee;

endcase

图像流AXI-Stream生成BMP文件的实现思路

图像流AXI-Stream生成BMP文件的实现思路