高速数字电路模块通常以 同步 (synchronous)电路的形式实现,它们由一个或者多个时钟驱动(触发)。对于 单一时钟(域) 的同步电路而言,只要输入和时钟的关系满足 建立(setup)时间 、保持(hold)时间的时序关系,电路的输出(布尔值)就是可预测的,这是数字逻辑电路设计的基础。如果 不能满足建立保持时间 ,我们认为输入是 异步 (asynchronous) 信号 。一个时钟域的同步信号输出到另一个时钟域通常被认为是异步信号。

本文从同步电路的时序模型出发,探讨了两种时钟同步的总线电路方案:

- 共同时钟 (common clock)总线

- 源同步 (source synchronous)总线

共同时钟总线的收发端使用同一时钟,结构简单,由于物理限制和PVT效应,局限于时钟速率比较低的应用;源同步总线增加 接口时钟 ,并以 与数据相同的方式发送 ,大大提升了接口时钟速率,由于引入了 不同的时钟域 ,也增加了接口设计的复杂程度。

1. 时钟同步电路的时序模型

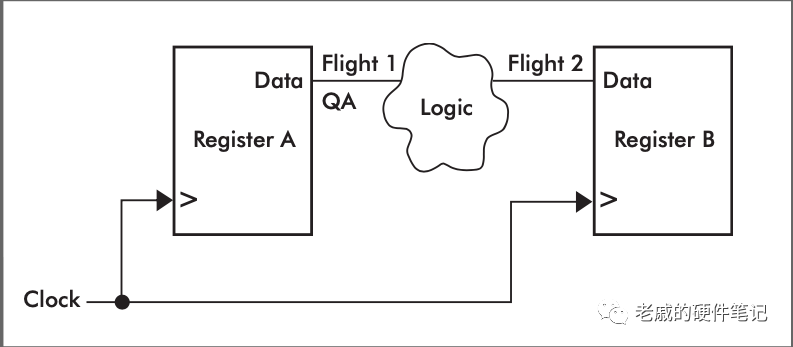

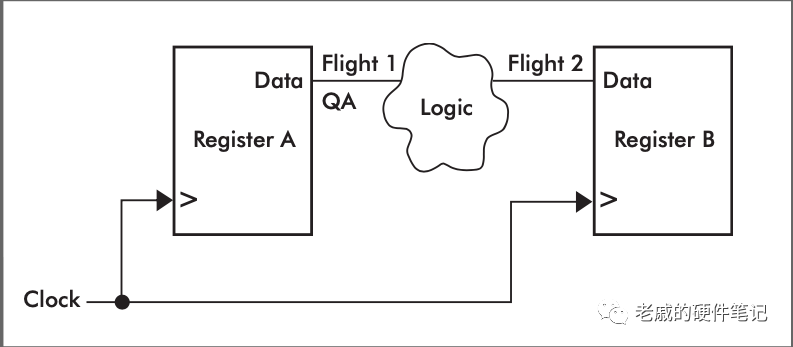

<图1>

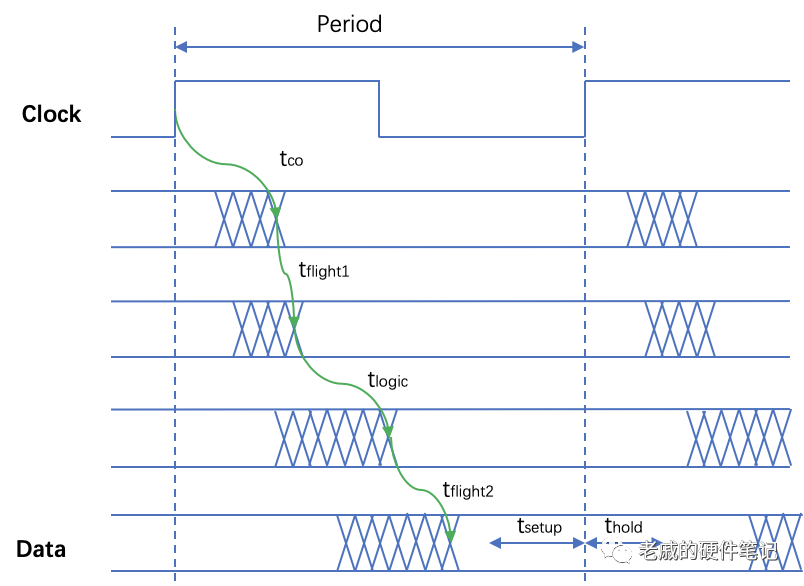

寄存器A在时钟(launch clock)的上升沿打出数据,经过两段飞行时间(传输延时)和组合逻辑电路延时之后,在下一个时钟沿(capture clock)被寄存器B抓取,这里假设A、B的时钟完全相同 - 频率相同相位相同。在两个时钟上升沿之间,按照时间顺序,发生了下列事件:

寄存器A打出输出(QA)。QA在上升沿之后一段时间才能有效(valid),这个时间是tco(clock to output);

传输延时tflight1,组合逻辑电路引起的延时tlogic,传输延时tflight2;

寄存器B抓取输入。输入在时钟上升沿之前必须提前稳定(建立时间tsetup),在时钟上升沿之后保持一段时间(保持时间thold)。假如不满足建立、保持时间的要求,那么B的输出可能会非0非1的亚稳态(Metastability)。

<图2>

把这些事件衔接在一起,形成了时序预算(timing budget)分配图。注意,‘X’表示不确定区间,通常是由PVT(制程电压温度)效应引起的偏差。

tsetup_margin = Period - tco(max)- tflight1 - tlogic(max) - tflight2 - tsetup

thold_margin = tco(min) + tflight1 + tlogic(min) + tflight2 - thold

tsetup_margin和thold_margin为 时序裕量 (margin),它**>=0代表满足建立保持时间**要求。

2. 共同时钟(common clock)系统总线

共同时钟系统其实可以借用<图1>,只需要把寄存器换成芯片(系统)。

共同时钟系统只有一个时钟(域),无论发送端还是接收端。

回到时序计算公式,要使tsetup_margin >=0,可以得到:

Period >= tco(max) + tflight1 + tlogic(max) + tflight2 + tsetup

右边这些参数代表了真实的物理局限,它们决定了时钟可以跑多快(时钟周期最小是多少)。

tflight1、tflight2来自于PCB走线,连接器,芯片封装等等。

tco、tsetup、tlogic代表芯片的 物理特性参数 。不同的芯片在不同的温度/电压下由于PVT效应表现会有变化,形成了时序图上的 不确定区间 。我们必须计算最恶劣(worst case)的情况,这会吃掉时序裕量。

而且,我们也做不到理想的单一同步时钟。出于信号质量的考量,时钟信号通常是点对点(point to point)的连接。不同模块的时钟,通常是连接同一个时钟buffer的不同扇出(fanout)。在工程实践上,理想的同步很难做到,只能把相位偏差(skew)控制在一定范围内。

所有这些,都限制了时钟速度或者数据吞吐量的提升,而优化参数常常意味着成本的抬升。老戚看到的共同时钟系统的时钟没有超过100MHz的。实现更高速总线的解决办法是源同步时钟方案。

3. 源同步(source synchronous)系统

源同步在芯片(系统)接口上 同时输出数据和(接口)时钟 ,数据和时钟采用完全相同的IO结构,从而最大程度的抵消tco,tflight等等。通常认为,同一个芯片上的PVT效应也是一致的。

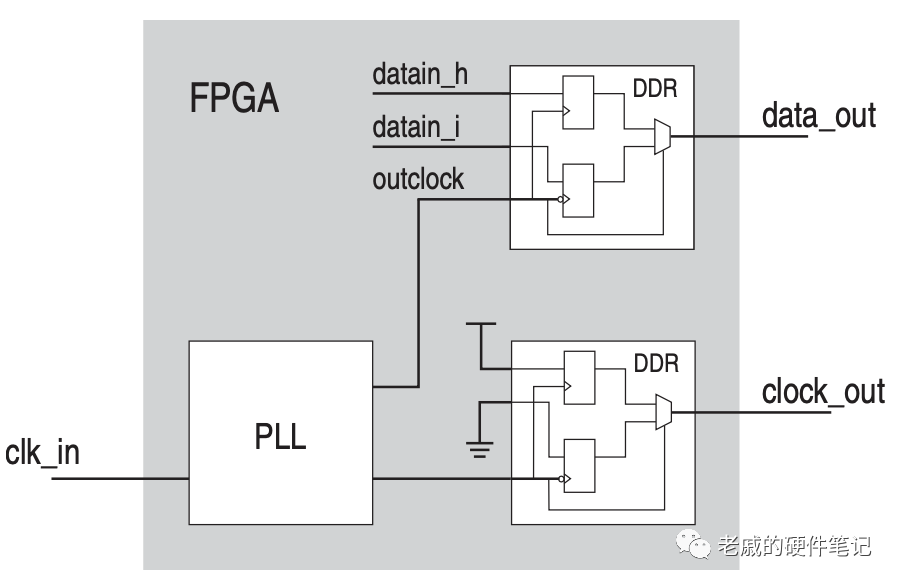

<图3>

<图3>是典型的中心对齐(center aligned)的源同步DDR输出。内部PLL的输出两路相位相差90度的时钟,经过同等的传输延时,到达接收端的时候,时钟刚好处在数据的中心(假定接收端建立保持时间的要求也是对等的)。接收端使用接口时钟clock_out抓取数据data_out,紧接着把数据同步到本地时钟。 接口时钟和本地时钟并不一致 ,属于 不同的时钟域 。

现有的高速并行接口无一例外都是源同步,最典型的当然是内存接口。以DDR4为例,地址/命令/片选信号和主时钟形成了一组源同步总线,内存数据DQ每8位就会有一个DQS信号作为接口时钟,形成源同步的数据时钟总线。在接收端,数据会先被抓取到相应DQS的时钟域,然后同步到主时钟。

源同步很好的解决了接口总线的速度问题,却也引入了不同的时钟域, 增加了收发接口设计的复杂度 。

- 跨时钟域(clock domain crossing)

实现跨时钟域的信号传递要回到时钟域C0的输出到时钟域C1的输入的建立保持时间的基本问题。

假如时钟C0/C1 同源 (不同频,例如分频/倍频关系)而且相位差固定的 可以直接用本地时钟抓取 ;同频(源)但是不知道相位关系不确定的可以以FIFO的方式解决;有频差的也可以用 FIFO解决 ,但要防止溢出(overrun,underrun)。

还是以DDR4内存接口为例,假设主时钟是1600MHz,那么DQS则是倍频 --- 3200MHz。由于时钟(包括地址/命令/片选)信号的fly-by拓扑,时钟到达不同内存颗粒存在先后顺序。对于写操作(write),控制器通过write leveling侦测到未经调整的DQS和主时钟的相位关系,相应的调整输出DQS的相位,保证内存颗粒接收的DQS和主时钟保持 特定的相位关系 ,从而在颗粒内部能够以最简单的方式(同时延时latency最小)完成跨时钟域。对于读操作,似乎有read leveling来实现相似的功能(这方面资料不详)。有趣的是,在DDR4内存接口,控制器(通常逻辑更为复杂)承担了所有时序调整的责任,内存(存储厂商的逻辑设计能力要差一些)接口则以最简化的方式工作。

在以太网领域,处理跨时钟域更常用的方法是FIFO(First In First Out)。FIFO不仅能够处理同频时钟的跨时钟域数据转换,也能处理不同频率(有限频差)的跨时钟域处理,从而获得了广泛的应用。PCIe协议和以太网协议都运用基于FIFO的 弹性缓冲 (elastic buffer)来处理系统时钟的PPM偏差问题。

-

寄存器

+关注

关注

31文章

5355浏览量

120513 -

连接器

+关注

关注

98文章

14547浏览量

136654 -

同步电路

+关注

关注

1文章

60浏览量

13313 -

FIFO存储

+关注

关注

0文章

103浏览量

5998 -

PCB走线

+关注

关注

3文章

134浏览量

13923

发布评论请先 登录

相关推荐

两种典型的电池供电电路的设计方案

SOPC设计中的两种片上总线分析

基于FPGA的时钟恢复以及系统同步方案设计

两种不同结构的永磁同步电机特点说明

两种总线数据两种传递形式:PIO、DMA介绍资料下载

探讨两种时钟同步的总线电路方案

探讨两种时钟同步的总线电路方案

评论