3DIC设计的重要性日益凸显。当今市场对AI应用的需求在不断增加,而摩尔定律的步伐却在放缓,这使得芯片开发者不得不寻求其他类型的芯片架构,以满足消费者和领先服务提供商的预期。3DIC设计并不是简单地将多个裸片相邻连接,而是通过硅晶圆或裸片的垂直堆叠来大幅提高性能和功耗表现,并让尺寸变得更小。

为此,新思科技和力晶积成电子制造股份有限公司(简称“力积电”)携手合作,共同推出新的晶圆堆栈晶圆(WoW)和晶圆堆栈芯片(CoW)解决方案。这是一种特殊的3DIC设计,它借助新思科技的3DIC Compiler平台和力积电的先进制程技术,创造出一种新的联合解决方案,让开发者能够将DRAM存储器直接堆叠和键合在芯片上,从而以更低的成本创建出先进的电路。

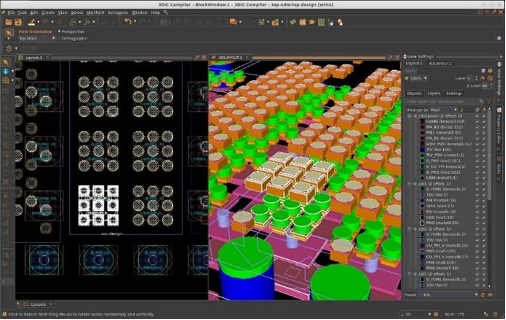

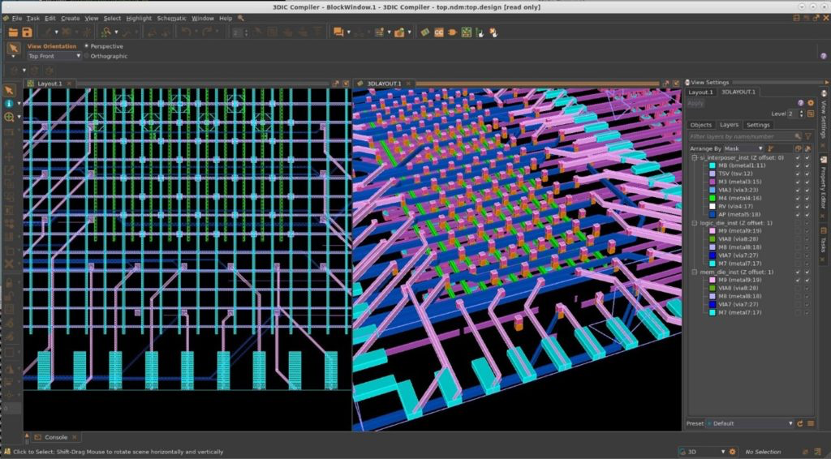

新思科技3DIC Compiler直观地显示了3D堆叠裸片中的芯片凸块、TSV和混合键合

力晶积成电子制造股份有限公司副总裁兼首席技术官S.Z. Chang表示:“3DIC设计非常复杂,尤其是在堆叠内存和逻辑裸片方面,需要依赖半导体生态系统中众多参与者的专业知识。我们很高兴能与新思科技密切合作,带来这一出色的解决方案。有了该解决方案,开发者在将多个半导体晶圆融合成一个3D设计时,所需的时间会减少1-2个月,同时堆叠两个裸片所需的迭代次数也会相应减少。”

本文将详细介绍WoW、混合键合及其主要优势,并探讨为什么DRAM逻辑堆叠有利于打造创新性的AI应用,以及新思科技与力积电联合打造的这一新解决方案如何帮助提高开发效率并带来量产时效优势。

什么是WoW混合键合和CoW混合键合?

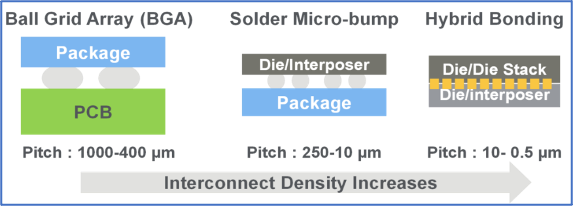

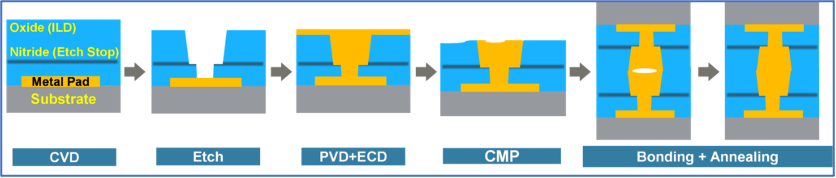

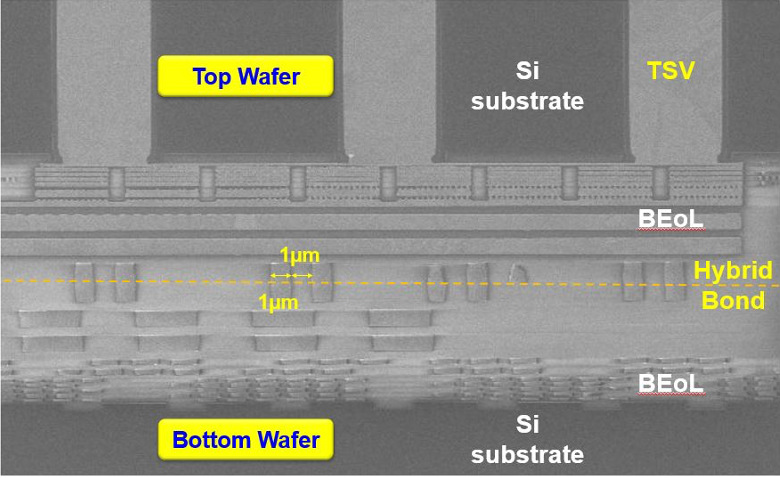

WoW混合键合堆叠是一种3D设计技术,它通过以电气方式连接不同的晶圆,打造单个集成器件。在该技术中,每个晶圆上都存在微小的铜焊盘,这些焊盘被永久地键合在一起,形成数以万计甚至百万计的电路互连。CoW混合键合与此相似,当设计中用到多种不同尺寸的芯片时,这可能是更实用的方法。通过WoW和CoW 3D堆叠,混合键合在没有增加功耗的情况下缩短了信号传输距离,并提供了比任何其他3D集成方案更高的互连和带宽密度。该技术可以微缩到亚微米级互连,有助于实现广泛的芯片分解和小芯片架构创新。

力积电专注于利用现有的芯片供应链,开发间距小于3um的WoW堆叠技术。此外,力积电还与新思科技通力合作,通过采用坚固的铜-铜混合键合技术和硅通孔(TSV)工艺,成功展现了晶圆级多堆叠结构的优势。

细间距互连微缩(图源:L.Jiang等,ECTC 2022)

不过,与其他方法相比,混合键合要复杂得多,随之而来的就是成本问题。但对于AI训练引擎等高级应用来说,这一成本还是非常值得的,因为它显著提高了内存带宽密度并降低了延迟。使用混合键合在逻辑器件上堆叠内存带来了AI所需的高性能和低延迟,并且与传统的2D甚至2.5D设计相比,还存在许多额外的改进。

混合键合工艺流程(图源:Albert Lan等,2021年第17届国际器件封装大会)

在逻辑器件上堆叠DRAM所面临的挑战

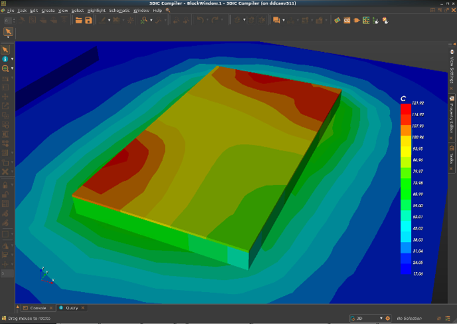

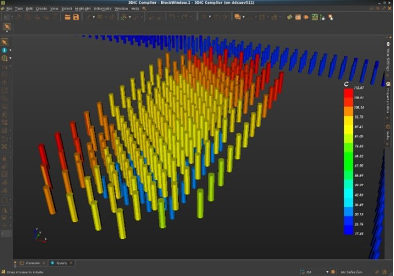

新思科技3DIC Compiler直观地显示了处理器芯片上DRAM堆叠的发热情况

长期以来,芯片开发者一直在思考如何更好地堆叠处理器和内存。其中有许多因素需要考虑:选择异构还是同构集成,如何更好地为裸片堆叠供电,热管理,栈内PVT传感器,压力引起的性能和可靠性问题等等。

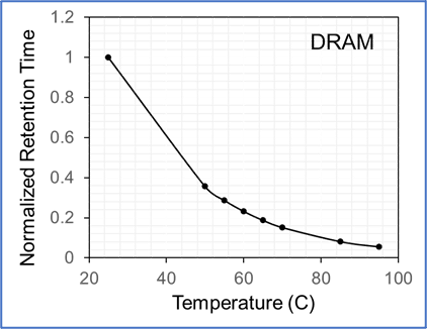

新思科技产品总监Kenneth Larsen指出:“在堆叠动态随机存取存储器(DRAM)而非静态随机存取存储器(SRAM)时,这些因素会变得更加复杂,因为DRAM的数据保留能力对温度较为敏感。在3D堆叠结构中,处理器和DRAM的工作温度可能达到110摄氏度--120摄氏度,而在2D DRAM结构中则为55摄氏度。”

较高的温度将会导致DRAM由于电荷泄漏而更快地丢失数据。因此,在给定的时间段内需要更多的自刷新,才能确保数据处于健康状态。芯片开发者需要探究温度会对整个系统的性能产生怎样的影响。

DRAM的数据保留时间对温度较为敏感

在逻辑器件上堆叠DRAM时,底部计算逻辑裸片所产生的热量会向上散发而影响内存,因而有必要通过设计来解决发热和散热问题。

再者,内存和逻辑设计由不同的供应商或设计团队负责,由于团队之间没有共同的沟通渠道来展开讨论或交换设计,因此可能会导致在堆叠这两者时出现流程脱节。此外,几何结构及采用的缩小工艺也不同;例如,一个是100% GDS,而另一个则是90% GDS。面对这些挑战,需要一种创新的EDA解决方案,帮助开发者从设计阶段顺利进入制造阶段。

高效的Multi-Die系统集成

力积电与新思科技在这一新解决方案上的合作主要依赖于新思科技的3DIC Compiler平台。该平台是一个完整的端到端解决方案,可实现高效的3D Multi-Die系统集成。3DIC Compiler基于新思科技数字设计系列的通用融合数据模型基础结构,它融合众多变革性的Multi-Die设计功能,提供了一个完整的3D平台,涵盖从架构设计到芯片签核的整个过程。该解决方案包括沉浸式2D和3D直观显示、跨层次结构探索和规划、设计和实现、DFx、系统级验证和签核分析。

DRAM处理器的中介层

系统的全连接模型可以在3DIC Compiler中建模,也可以通过标准网表和各种文本格式导入。3DIC Compiler提供了在底部和顶部裸片之间创建连接的功能,与手动方法相比,这可为芯片开发者节省多达两个月的时间。在概念、设计、实现和制造阶段,优化芯片涉及多个步骤和多项检查。

新思科技3DIC Compiler中直观地显示了TSV热图

其中一个步骤是3D系统连接检查,用于验证半导体裸片、裸片堆叠、中介层、嵌入式桥接和封装基板之间的电气、逻辑和物理连接。这项检查可以在设计中检查从裸片上的逻辑裸片焊盘到主IO(键合和凸块之间的物理连接)的电气连接,并可以明确指出网状结构不完整或短路等问题。3D设计规则检查、裸片镜像堆叠、键合协调以及功耗和DFT检查等也在此范围内。

新思科技的3DIC Compiler软件会检查信号和供电是否借由TSV从底部裸片正确到达了顶部裸片。此外,它还可以进行必要的热仿真,从而对两个裸片间的相互作用(包括功耗和随后的产生热量)进行建模。两个裸片之间的热量需要散掉,而3DIC Compiler可以帮助开发者利用多种不同的方法来实现这一点。

WoW解决方案(图源:力积电)

在使用力积电和新思科技合作打造的全新3D WoW和CoW解决方案时,经认证的新思科技数字设计系列解决方案会在从流片开始的整个流程中为客户提供协助,而3DIC Compiler正是构建在该数字设计系列的基础之上。这一新的解决方案在内存和逻辑裸片之间提供了高带宽,从而可以提高AI推理的性能和速度。

随着AI技术日渐融入人们的日常生活,我们期望它变得更加智能,因此对内存带宽、IO和算力的总体需求会随着时间的推移而不断增长。然而,摩尔定律已在放缓,因此先进的封装将会是芯片开发者今后所要寻求的答案。3DIC Compiler等产品正在协助开发者快速、有效地满足这些新的应用需求,推动人工智能及更多领域向前发展。

原文标题:新思科技携手力积电,以3DIC解决方案将AI推向新高

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

-

新思科技

+关注

关注

5文章

812浏览量

50450 -

力积电

+关注

关注

0文章

35浏览量

88

原文标题:新思科技携手力积电,以3DIC解决方案将AI推向新高

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Foundry 2.0优势已现!台积电2024营收创历史新高,看好2025年AI和HPC增长

玩美移动AI解决方案再拓展:全新AI卷发分析,将AI发质检测技术推向新高度

台积电2025年将全球建十座厂,资本支出创历史新高

软银携手台积电共筑AI芯片新篇章

新思科技7月份行业事件

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

台积电上调代工费以确保稳定供应

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

新思科技推出业界首款PCIe 7.0 IP解决方案

新思科技与台积公司深度合作,推动芯片设计创新

新思科技面向台积公司先进工艺加速下一代芯片创新

新思科技携手力积电,以3DIC解决方案将AI推向新高

新思科技携手力积电,以3DIC解决方案将AI推向新高

评论