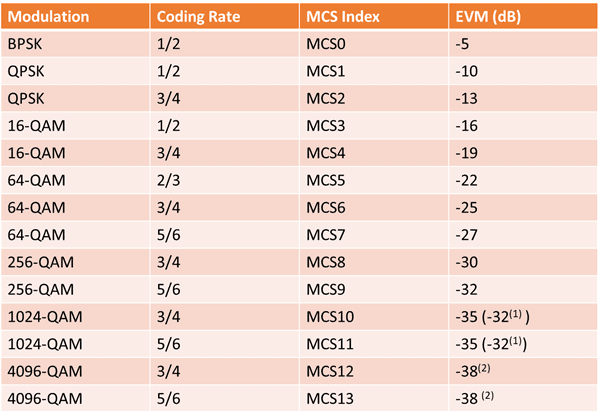

EVM与调变阶数

由上表可以知道 调变越高阶 其EVM的要求越严格

这是因为 调变越高阶的信号 在传送过程中 越容易被噪声干扰

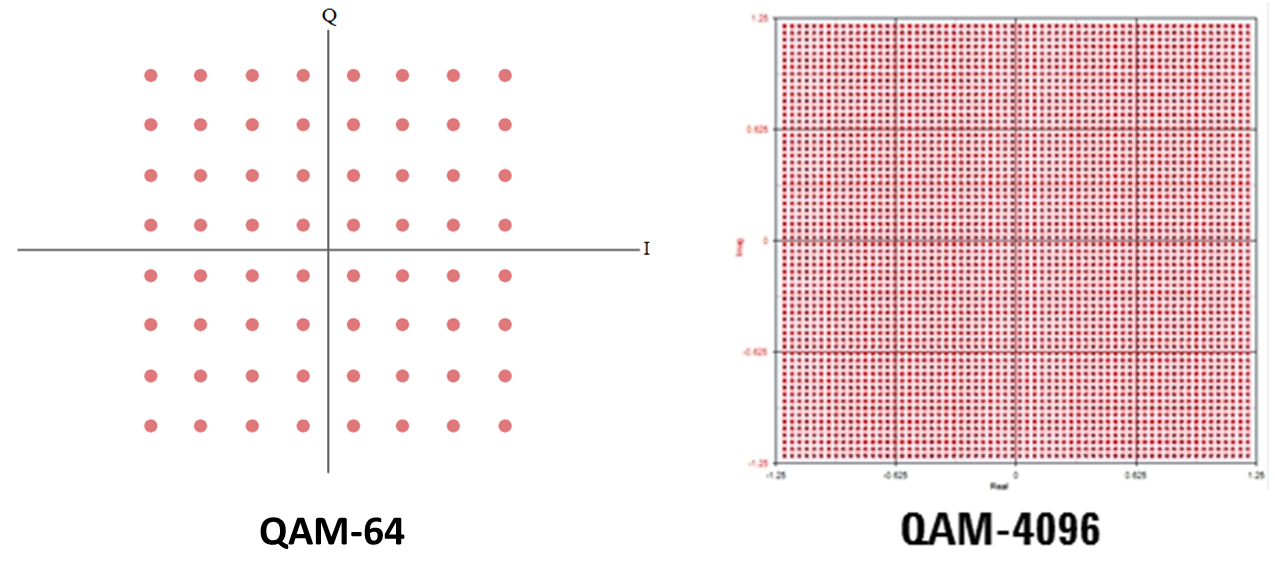

以下图为例 假设你射飞镖 请问哪张图比较容易射中?

很明显是右图 对吧?

所以 才需要更严格的EVM规格 确保信息的调变精确度

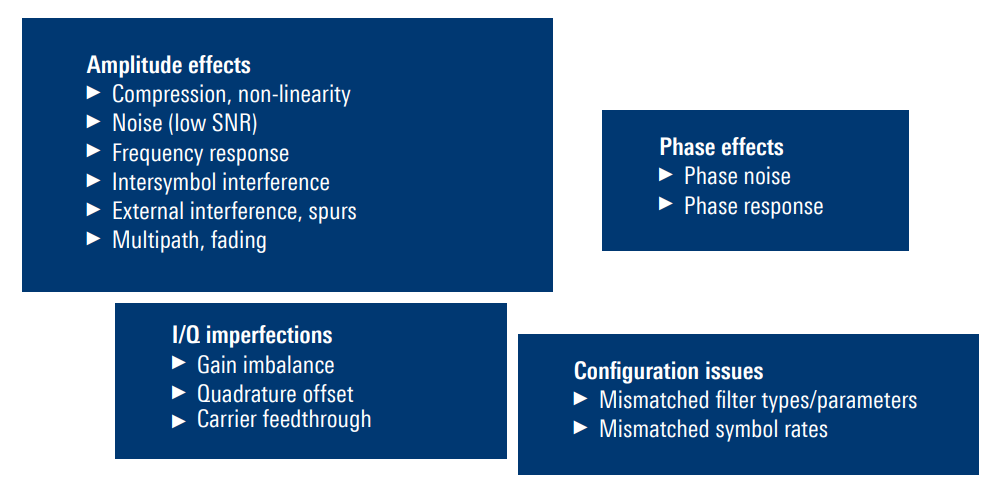

影响EVM的要素

一般而言 会让EVM变差的 有以下因素[1]:

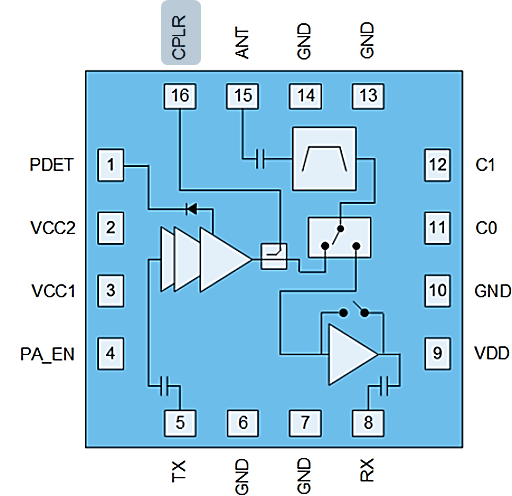

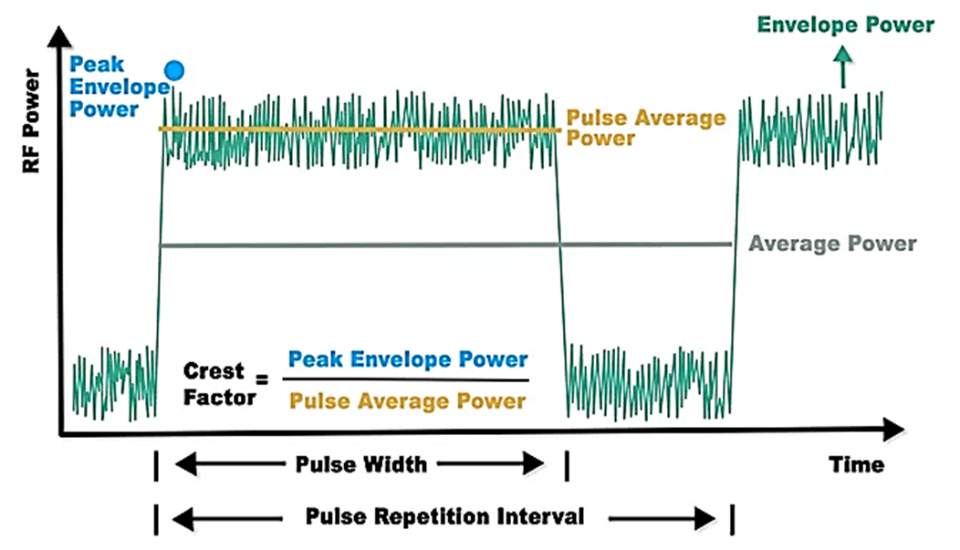

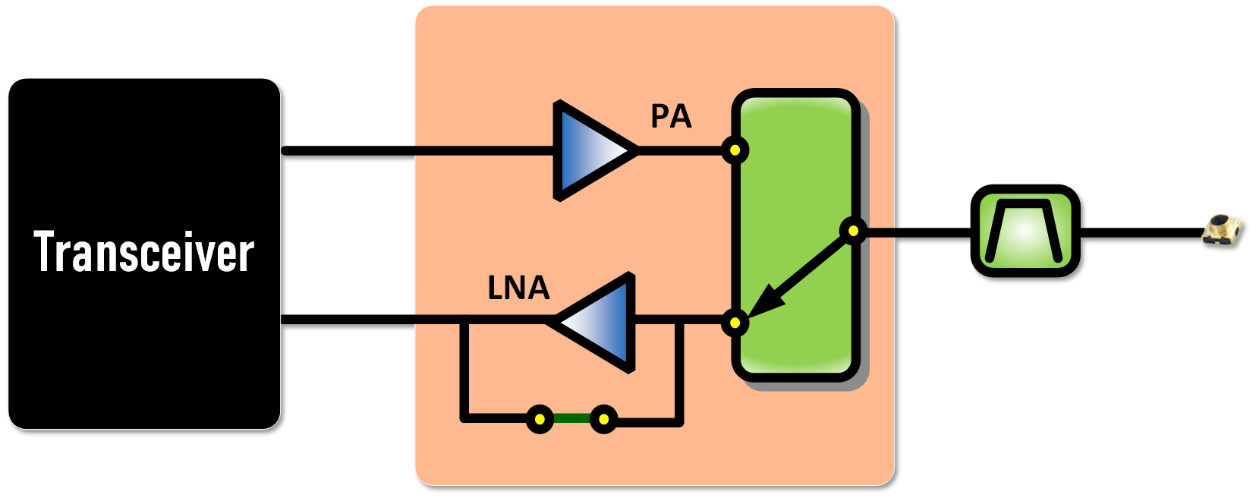

其实还有一点 那就是反馈路径 由下图可知

目前诸多前端模块 都有反馈路径

倘若反馈路径受到干扰 或是阻抗离50欧姆太远

其AM-AM会受到影响 进而影响EVM性能

EVM的两个维度

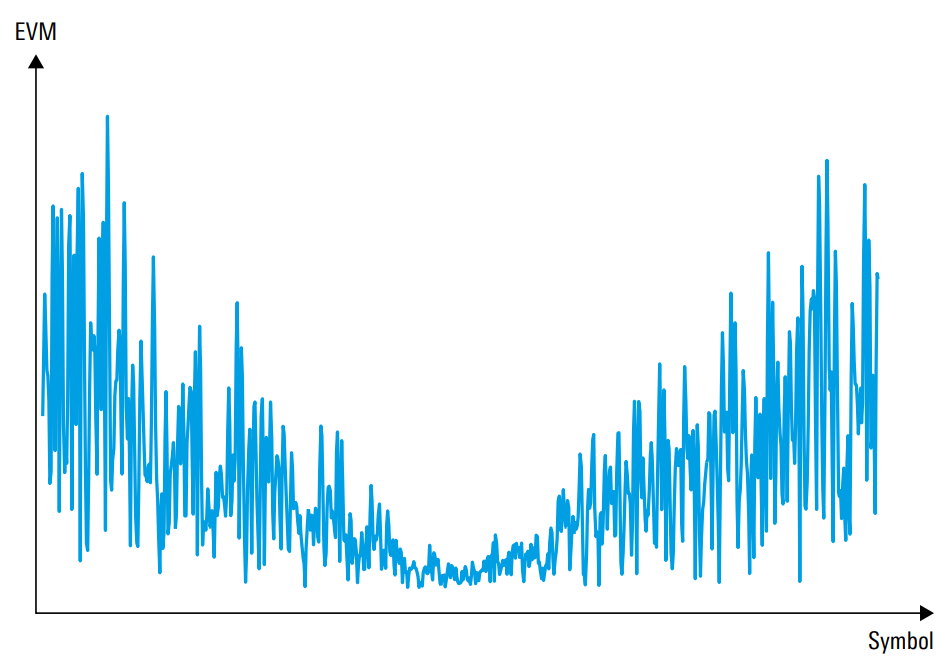

EVM VS Time

由[1]可知道 若振幅在某时间点大幅变化 则该时间点的EVM也会

比其他时间点来得高 由下图可知[4] 以WIFI为例 因为是分时多任务

其波形为Burst Mode 故在Rising/Falling时 其振幅变化最大

这也是为何EVM在头尾的时间点 会比中间段时间点来得高

呈现”U”字形

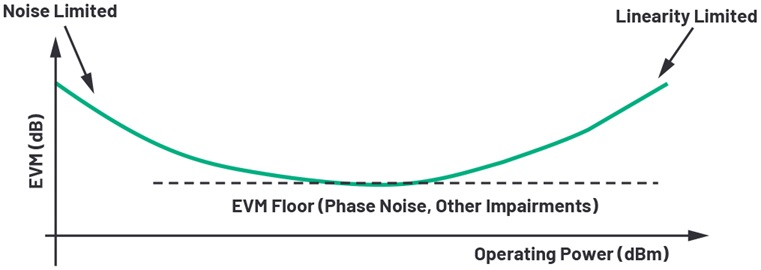

EVM VS Power

同EVM VS Time的图一样 也是”U”字形

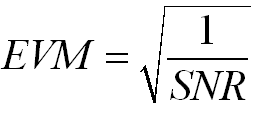

因为EVM跟SNR成反比

因此我们朝

“为何SNR在小功率与大功率时 会特别低”

就可以理解清楚了

小功率时 因为讯号较微弱 容易受到噪声影响

故SNR会偏低 则EVM偏高

大功率时 则是因为可能会因为饱和 而导致诸多非线性效应诞生

使其Noise Floor会严重上涨 故SNR下降 EVM偏高

EVM在小功率时 变差的影响因素

针对小功率时的EVM 我们举两项

前述会让EVM变差的因素来说明

一项是Carrier Feedthrough或称LO Leakage

另一项是Phase Noise

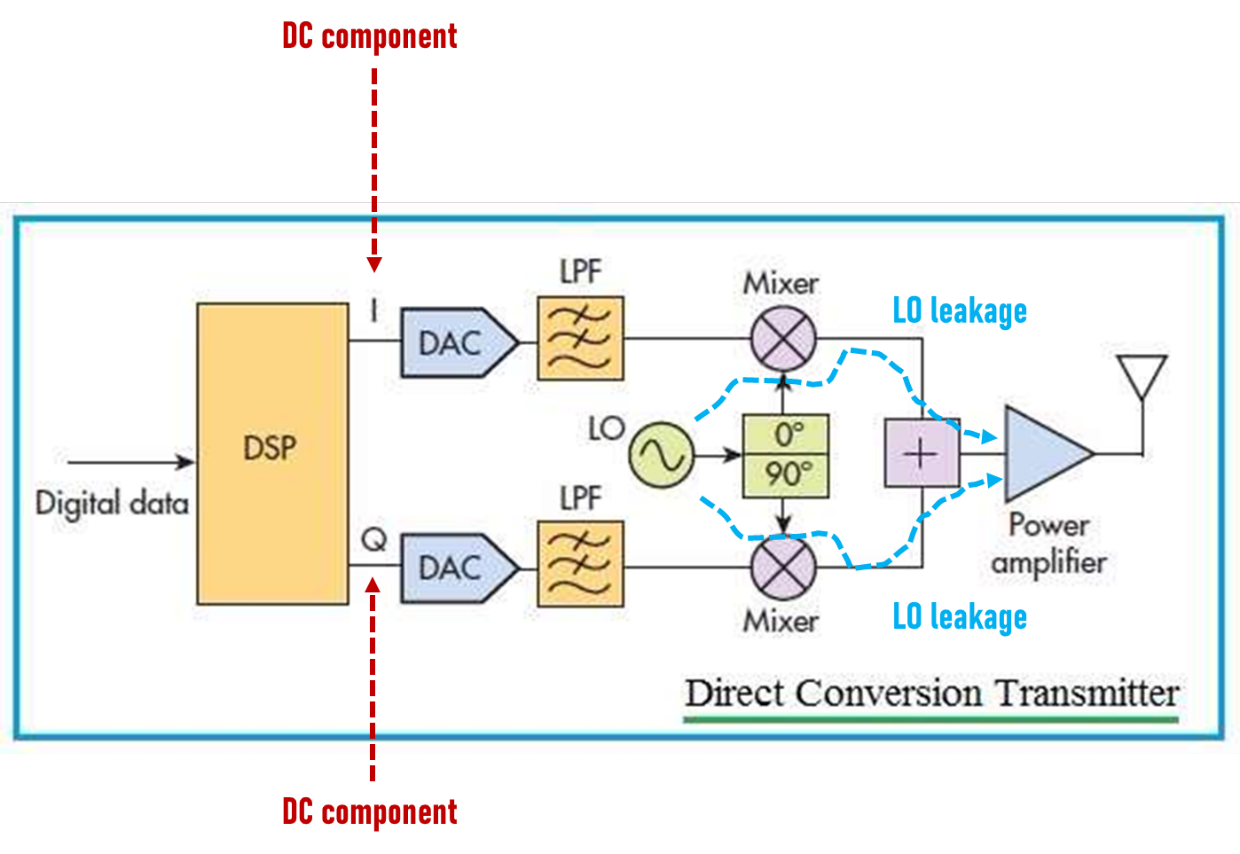

下图是零中频发射器的架构图

其RF讯号 是由基频讯号 与LO讯号 混波得来

假设

RF = LO – BB

那么我们得知 会有三项 我们不需要的噪声

LO + BB

LO

DC Component

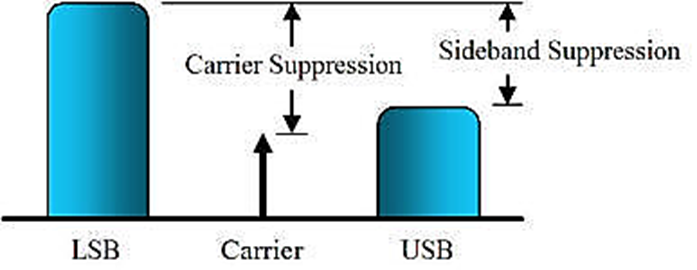

RF = LO – BB 我们称为LSB (Lower SideBand)

是我们需要的讯号

但混波过程中 也会有LO + BB的产物

称为USB (Upper Sideband) 是噪声

以及LO信号 直接泄漏到混波器输出端

该产物称为Carrier 也是噪声

另外 在IQ讯号 尚未升频时 若挟带直流讯号

该直流讯号 会跟着IQ讯号一并升频 最终出现在频谱上

该产物亦称为Carrier 也是噪声

而这三个产物 由于都离基频跟RF讯号太近

几乎无法靠硬件滤掉 只能靠软件的算法

加以抑制 称为Sideband suppression

以及Carrier Suppression

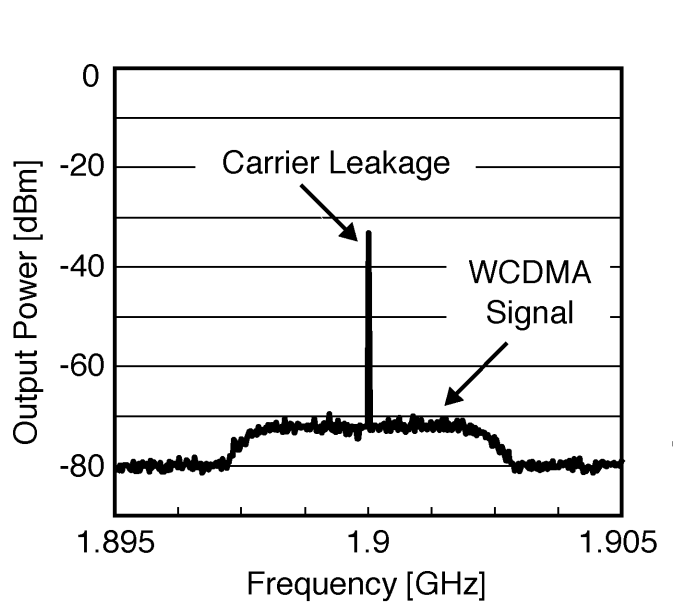

我们看下图

当小功率时 其Carrier leakage 甚至会比讯号还大

其SNR肯定不好 连带EVM就飙升

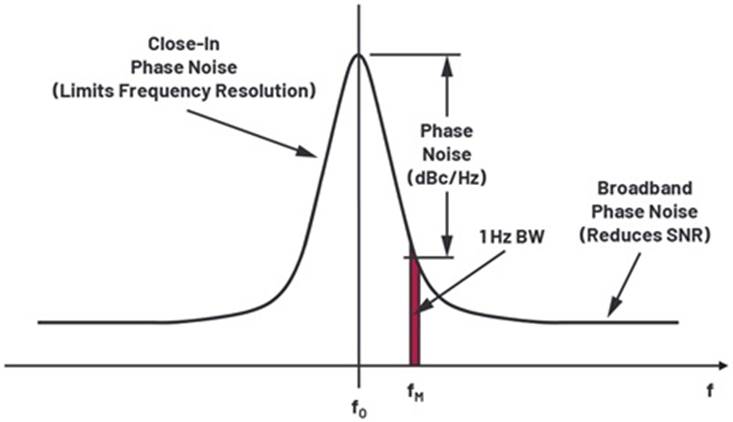

再来是Phase Noise影响

由上图可知 Phase Noise会让Noise Floor上涨

该影响在小功率时特别明显 因为SNR会显著下降

故EVM会飙升

EVM的迭加计算

由上述公式可知 最终量到的EVM 其实是由发射路径上

每个组件的EVM 最终加总得到

因此结合前面所说 收发器的输出RF讯号 因为讯号较微弱

故容易受到噪声影响 例如Phase Noise或Carrier Feedthrough

使得EVM飙高

而此时再经过PA的贡献后 最终量到的EVM 肯定不好

因此 EVM不好时 除了怀疑PA之外

更需要确认 是不是收发器输出RF讯号的EVM 就已经不好了

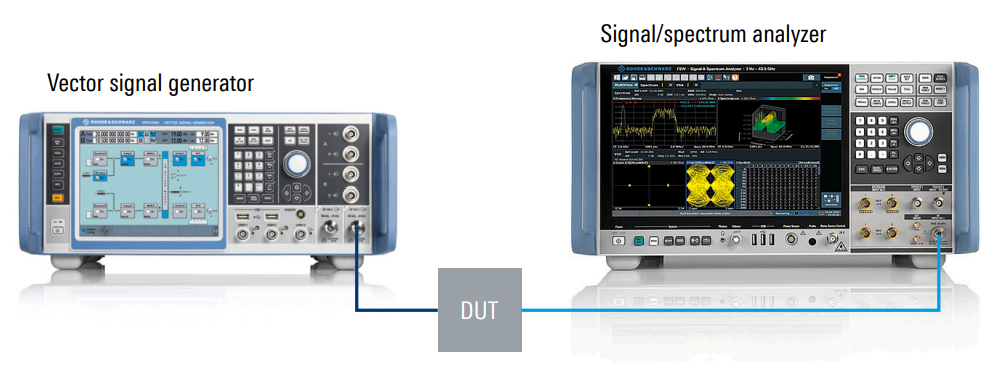

确认的方法 可以直接外灌讯号给PA

倘若单独量PA 量出来为-40dB

而板子上量到的 为-35dB

那表示收发器出来的EVM 为-36.65dB

故此时要改善的目标 其实是收发器 而非PA

当然 量测前 也要注意仪器本身的EVM

因为也会列入量测EVM值的计算

换言之 有可能单独PA量出来的EVM很高

主因是仪器的EVM高 而非PA本身EVM高

一般来讲 仪器本身的EVM 要低于待测物 5dB ~ 10dB

才不会影响到待测物 自身量出来的EVM[1]

-

信号

+关注

关注

12文章

2945浏览量

80479 -

EVM

+关注

关注

3文章

1040浏览量

43913 -

前端模块

+关注

关注

0文章

19浏览量

11314

发布评论请先 登录

如何影响FFX输出并最终影响系统性能?

哪些方法可以改善PDN对电源系统性能?

感知系统性能评估分析解决方案 精选资料分享

优化BIOS设置提高系统性能

频偏对脉冲成型多载波系统性能的影响分析

Linux系统性能优化技巧

Linux系统性能优化与调试的思路

EVM对系统性能的影响

EVM对系统性能的影响

评论