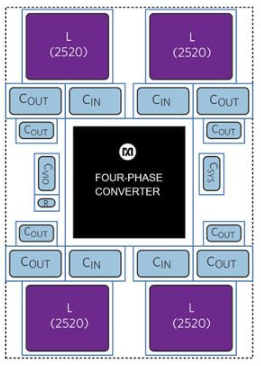

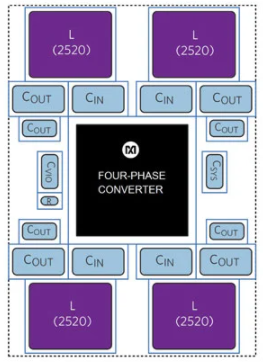

降压(降压)稳压器由于其固有的高效率,长期以来一直是首选的DC-DC转换电子主力。仅在降压模式下,电流在整个周期内被引导至输出。每个周期向输出的电流更高,使降压转换器成为最高效的架构。作为众多例子之一,现代微处理器,从用于功能强大的刀片到智能手机的微处理器,都以非常低的输入电压工作,使降压转换器成为必要的电源。随着这些应用变得越来越复杂,电源必须加强其电力输送,同时提高效率以减少热损失。因此,降压转换器已经从非同步开关发展到同步开关,从提供几百毫安电流的单相器件发展到可以成功提供数十到数百安培电流的多相器件。图1所示为现代四相交错降压转换器,为智能手机和平板电脑的CPU核心芯片供电。

图1.多相交错式PCB示意图

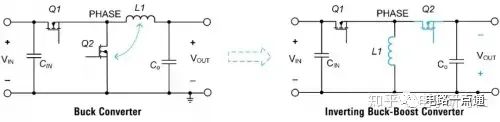

两相交错式降压转换器架构

为简单起见,我们将重点讨论两相交错式同步降压转换器架构(图 2)。

图2.两相交错式降压转换器示意图

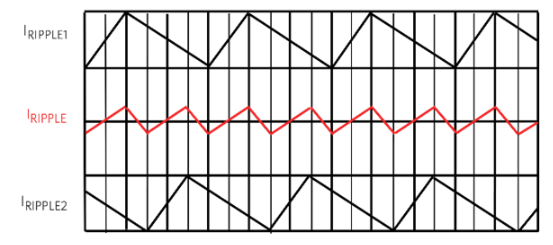

两个交错相位可确保纹波电流,从而降低纹波电压。在相对较低的每相工作频率下获得较低的总纹波电流。例如,图3显示,在180%占空比下,两个纹波电流错相33°,导致总纹波电流在两倍频率下幅度为单相幅度的一半。较低的输出电流纹波和较高频率下的电压纹波意味着输出上需要的电容器更少,从而减小了BOM。

图3.两相电流纹波降低与时间的关系图

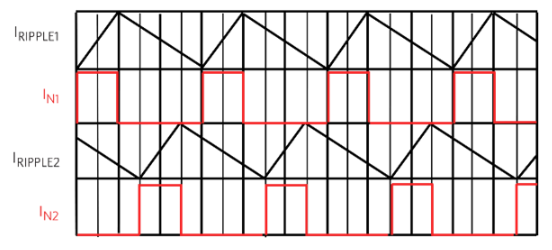

两相架构还需要较少的输入电容。总输入电流是两个异相电流(I合1和我合2在图 4 中)。在这里,与单相操作相比,随着时间的推移分散总输入电流会降低输入电流的总RMS值,从而允许使用更小的输入电流纹波滤波器。

图4.两相输出纹波电流和输入电流随时间的关系图

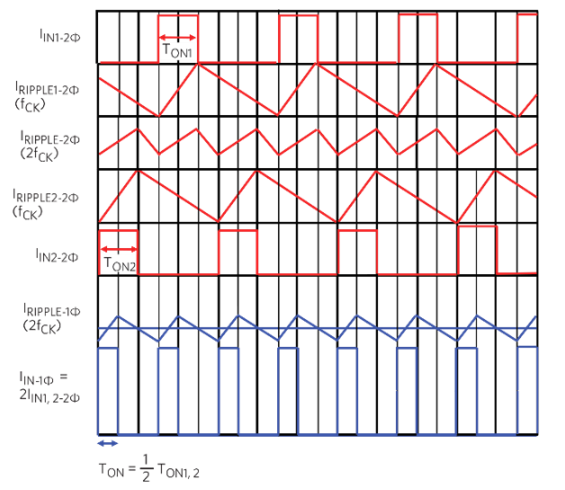

此外,如图5所示,当两种方案以相同的输出纹波频率运行时,两相(2Φ,红色所示)比单相(1Φ,蓝色所示)更有效。单相,以两倍的开关频率(f西 南部)的两相,也可以实现高频和低电流纹波,但开关损耗更高。两种方案在一个周期内的转换次数相等,但两相转换器消耗的电流是单相转换器的一半(超过持续时间的两倍),从而降低了开关损耗。

图5.两相电流与单相电流与时间的关系图

两相转换器的另一大优点是负载阶跃期间的快速瞬态响应和更低的电压过冲/下冲。由于每相电流减半,电流纹波幅度减小,纹波频率翻倍,现在可以推高相位开关频率,以进一步减小元件尺寸并增加转换器的闭环带宽,而不会遇到热限制。

最后,随着总负载电流的增加,无源元件的尺寸也会增加。对于高负载,单相降压的电感可能体积庞大且效率低下。多相操作可降低每相的电流,从而确保无源器件的最佳尺寸。

例如,MAX77812是一款20A可配置、单相至四相、单至四输出、大电流、降压转换器。系统设计人员可以使用丰富的多相交错式降压转换器产品组合。

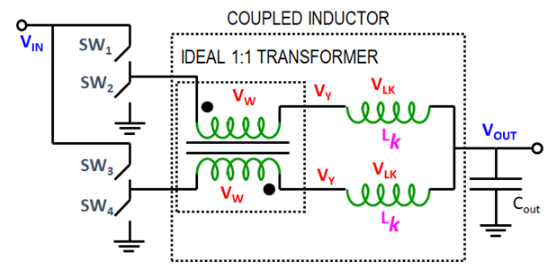

为什么耦合电感是大电流应用的理想选择

在非常高电流的应用中,必须挤出最后一个百分点的效率,还有另一张牌可以打:耦合电感,其中电感器缠绕在公共磁芯上。在两相耦合电感器(图 6)中,绕组方向使得磁通量抵消,理想情况下变压器漏感为 LK和无限磁化电感。在实践中,我们最终得到的每绕组电感非常低(Lk) 与非耦合情况相比。

图6.两相耦合电感器模型及工作原理图

让我们用软件编写网络方程1和软件4上。理想的 1:1 变压器力等于绕组电压 V在和相等的压降 VP.跨电感。对于顶级分支,我们有:

VIN = 大众 + VLK + VOUT

对于底部分支:

VW = VOUT + VLK

从中:

VIN = 2VOUT + 2VLK

其中:

VOUT + VLK = VY

因此:

VY = VIN/2

和:

VLK = VIN/2 -VOUT

即电压VP.每个电感两端的电感小于输入电压的一半!这还不到非耦合电感情况值的一半。在电感相等时,耦合电感产生的纹波电流不到两个非耦合电感的一半,从而产生更小的BOM和更高的效率。或者,以较低的电感工作可改善BOM和瞬态响应。

总结

降压稳压器是低压DC-DC转换主力,为从服务器到智能手机的应用提供核心电源。它已从非同步发展到同步,从单相发展到多相,最近又从非耦合电感器发展到耦合电感器,跟上了其复杂负载的步伐并使其能够持续发展。

审核编辑:郭婷

-

稳压器

+关注

关注

24文章

4968浏览量

100447 -

微处理器

+关注

关注

11文章

2440浏览量

86143 -

DC-DC

+关注

关注

30文章

2487浏览量

87651

发布评论请先 登录

LDO和BUCK降压稳压器对比

LDO和BUCK降压稳压器对比

怎么选择线性稳压器与开关稳压器

基于LTC1629-6EG的多相同步降压开关稳压器

使用开关稳压器!设计您自己的DCDC转换器

LTM4645演示电路-高效多相降压电源µ模块稳压器(6-15V至1V@100A)

LTM4645演示电路-高效多相降压电源µ模块稳压器(6-15V至1V@75A)

LTM4636演示电路-高效、多相160A降压电源μ模块稳压器(4.7V-15V至0.9V@160A)

LTM4636演示电路-高效、多相80A降压式电源μ模块稳压器(4.7V-15V至0.9V@80A)

LTM4676演示电路-多相模块降压稳压器,带电源系统管理功能(5.75-16V至1V@75A)

功耗:获取有关电源应用和电路设计技巧了解多相降压稳压器的优势

功耗:获取有关电源应用和电路设计技巧了解多相降压稳压器的优势

评论