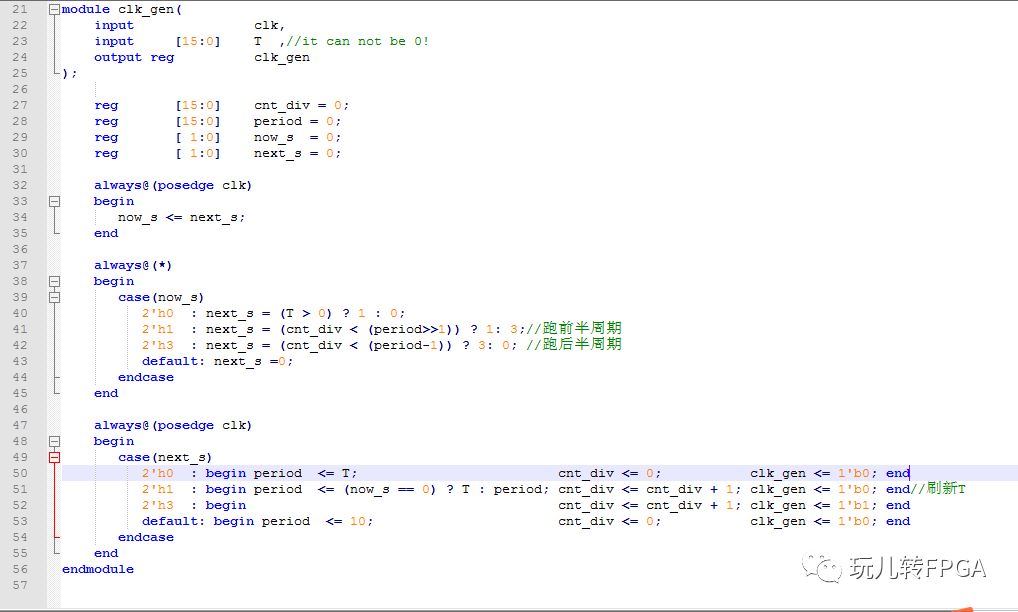

首先我们做一个模块,输入信号T,代表输出时钟周期,输出时钟周期严格等于T,对于熟悉FPGA的小伙伴应该很容易。下面是小编的代码。简单的说就是建立一个状态机,对输入周期参数在产生时钟的每个周期,第一时刻更新值,然后进入下一个状态计数,计数到和输入周期一致的时候又回到初始状态。

上面这个模块就是我们的控制对象,也就是说,我们要想办法让他的时钟频率Fo = 系统给定时钟频率Fi*N,也就是说: 输出时钟周期To = 系统时钟周期Ti/N。

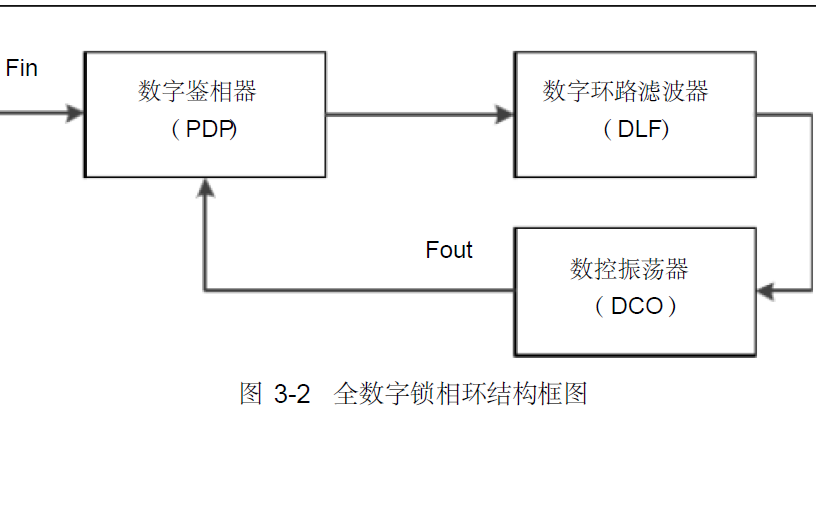

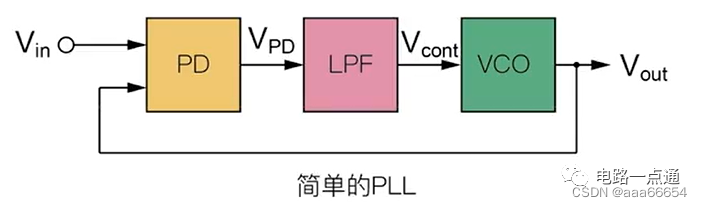

小编采用如下环路实现。从中可以看出,小编的方法反馈控制的是周期,所以一切参数都转化到周期上,输入和反馈,输出都是通过周期控制。从图中可以得出结论输出时钟周期To=N/(M*N+1)

输入时钟要求稳定,并且比系统时钟慢的越多越好,因为这样测量更准确。下面就是我们测量时钟周期的代码。反馈非常重要,因为他涉及到整个反馈环路的精度和运作效率。除以N的部分我们在另一个模块实现,因为测量时钟周期的模块是相对独立的输入和反馈都要用到,独立出来可以加强代码可重用性。这段代码就是在每个输入时钟上升沿电脑时候更新周期值。以保证周期的准确性。

控制对象和输入,反馈参数产生都已经好了,剩下的就是按照控制框图搭建反馈环路。代码如下图,代码中的Ti是在顶层产生的,输入时钟被测量后才把Ti给到环路输入。第34行是将反馈的时钟周期乘以反馈增益1/N,35行是将反馈误差乘以开环增益1/M。至此整个环路已经搭建完成!

这里附上小编顶层代码,这里从30行开始的模块就是产生上文说的Ti用的,输入时钟直接测量后,变成是种病周期T输入到feedback模块。

那么实际效果咋样呢,能工作吗?工作起来是啥样子?小编接下来就测试给大家看。测试代码如下,输出时钟周期在反馈的代码里面找,输入时钟周期是给定的,这两个找出来对比看看与理论差多远就知道了,这里M = 10,N=10。

仿真结果如下,看图1可知输出时钟周期稳定后为To = 102ns,输入时钟为Ti=1002ns,所以To/Ti = 0.1。而理论值为N/(MN+1)=10/(1010+1)=0.099。

误差err = |0.1-0.099|/0.1=1% !

我们看看下图的波形,输出时钟周期的震荡是不是很像连续系统的二阶震荡环节的阶跃响应?只不过超调不大,震荡周期比较少。这是因为我们的开环其实是一阶,加了反馈之后成了二阶系统。和控制原理书上很近似(看看离散控制部分会更觉得近似)。

-

锁相环

+关注

关注

35文章

589浏览量

87836 -

FPGA设计

+关注

关注

9文章

428浏览量

26562 -

负反馈电路

+关注

关注

1文章

35浏览量

9286 -

二阶系统

+关注

关注

1文章

16浏览量

9599

发布评论请先 登录

相关推荐

如何实现基于VHDL语言的全数字锁相环?

数字锁相环(DPLL),数字锁相环(DPLL)是什么?

基于数字锁相环消除反馈滞后的方法

教你怎么用负反馈控制实现纯数字锁相环

教你怎么用负反馈控制实现纯数字锁相环

评论