很多小伙伴开始学习时序约束的时候第一个疑惑就是标题,有的人可能会疑惑很久。不明白时序约束是什么作用,更不明白怎么用。

FPGA内部结构=LUT+触发器+走线+嵌入式模块(RAM,乘法器等)。下图大致描述了它的抽象结构。

以上公式告诉我们:信号是通过走线和各个模块产生连接。然后信号通过走线必然有延迟,有人认为电信是光速走线延时应该很短,可以忽略(全局时钟线的延时在时序紧张的情况下是不可忽略的),然而走线延迟可能超过你的想像。

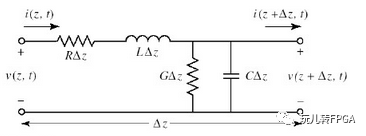

1.电信号在走线槽里面传播并不是光速,走线上有分布电感和地平面有分布电容,二者值越大,对电容充电时间越长,走线延迟越长,这写参数自然由工艺和封装来决定,和我们设计无关,但是却对我们的设计方法产生重大影响,传输模型如下:

2.除了传输线模型的延时以外,走线本身会经过很多类似路由器的结构去改变走线方向,在资源紧张的情况下可能会走过多个路由,这也就是为什么FPGA内部走线会很绕的原因,经过多级路由的走线延时会大大增加,在时序报告里面也可以看到的走线延迟=传输线延迟+路由延迟。

3.如果设计里面组合逻辑很多那么信号就会经过多个LUT,这也会产生延迟,在时序报告里面可以看见组合逻辑延迟和逻辑级数这2个选项。

综合以上3点,FPGA内部延时不可忽略!并且常常达到ns级!。

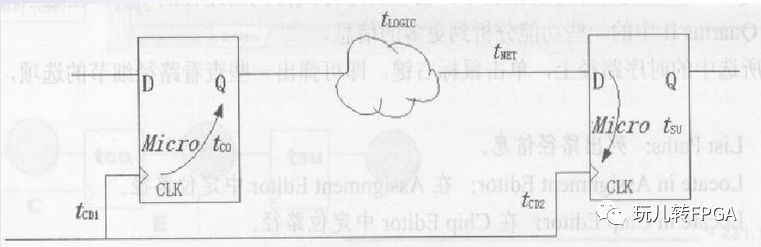

上图为实际生成的数字电路模型,从中看出

根据上图公式,tnet和tlogic一旦增加,最小时钟周期就会增加,也就意味着系统可以跑的最高频率会下降。

那么编译器怎么知道哪个是你的时钟,你的主时钟需要跑多少MHZ呢?如果编译器设计高了,会编译时间增长甚至报错,低了会导致实际上板产生竞争冒险,从而导致错误。所以为了避免以上问题,我们需要高速编译器这个时钟到底要多快,还有,相位关系,占空比。这样编译器才能根据我们的需求去对比延时所算出来会不会竞争冒险。所有的时序约束都是要告诉编译器,我的时钟和数据要满足怎样的关系,然后交给编译器去计算最糟糕的情况下能不能满足条件,还差多少ns就会不满足条件。

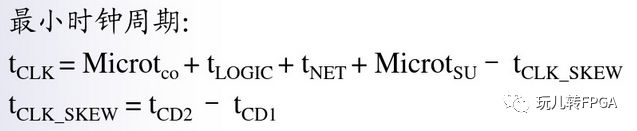

所以,为了告诉编译器时钟参数就有了

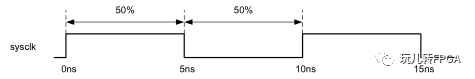

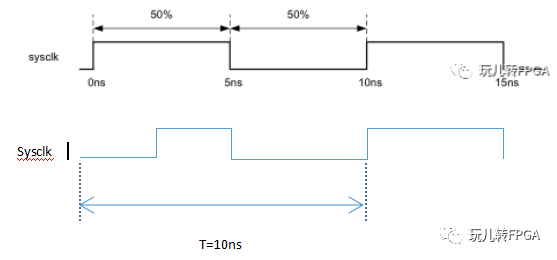

create_clock -name clk -period 10 [get_ports sysclk],这句xdc命令告诉编译器,时钟clk,从sysclk(get ports 后面摄取的是顶层要分配引脚的物理引脚,get pins后面摄取的是生成的某个寄存器或者器件的引脚,get nets摄取的是里面生成的某根线)这个引脚输入,时钟周期是10ns,由于相位和占空比未声明,所以初相位为0,占空比为50%。如下图:

如果想调节初相位90°和占空比25%:

create_clock -name devclk -period 10 -waveform {2.5 5} [get_ports sysclk]

这里-waveform {2.5 5}代表第一个跳变沿在第2.5ns处产生,第二个跳变沿在5ns处产生从而形成下图的时钟,这样就可以把所有的相位和占空比关系都描述清除。

编译器会根据时钟sysclk的周期和相位,在整个sysclk时钟域,计算延迟后对比sysclk和对应寄存器的数据端口进行对比,看是否满会产生竞争冒险,不满足的地方会报告出来。

-

嵌入式系统

+关注

关注

41文章

3590浏览量

129459 -

乘法器

+关注

关注

8文章

205浏览量

37049 -

触发器

+关注

关注

14文章

2000浏览量

61142 -

LUT

+关注

关注

0文章

49浏览量

12505 -

FPGA系统

+关注

关注

0文章

10浏览量

7032

发布评论请先 登录

相关推荐

VIVADO时序约束及STA基础

FPGA时序约束之衍生时钟约束和时钟分组约束

FPGA中的时序约束设计

深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果

FPGA时序约束简介

时序约束怎么用?时序约束到底是要干嘛?

时序约束怎么用?时序约束到底是要干嘛?

评论