CCSN Library

PT-SI在进行噪声分析前,首先需要确认Library中具备噪声模型。CCSN噪声模型建模是基于CCB(Channel Connected Block)。数字逻辑单元可以认为由一级或多级CCB组成,其中反相器,与非门,或非门只包含一级CCB;与门则包含两级CCB;而寄存器则包含多级CCB。下面就简单区分一下三种情况下噪声建模的区别:

单级CCB逻辑单元

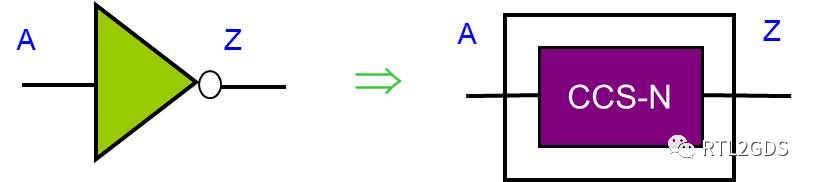

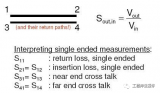

对于单级CCB逻辑单元,例如反相器,噪声建模基于时序狐(Arc Based)。噪声的传输可以基于Timing Arc,模型转换框图如下:

反相器的噪声模型在.lib中大致如下:

pin (Z) {

...

timing () {

related_pin: A;

...

ccsn_first_stage() { /*First stage CCB*/

...

}

}

...

}

两级CCB逻辑单元

对于两级CCB逻辑单元,例如与门,噪声建模也是基于时序狐(Arc Based)。分为input stage (ccsn_first_stage)和output stage (ccsn_last_stage),噪声的传输亦可以基于Timing Arc,模型转换框图如下:

与门的噪声模型在.lib中大致如下:

pin (Z) {

...

timing () {

related_pin: A;

...

ccsn_first_stage() { /*Input to Internal Node*/

...

}

ccsn_last_stage() { /*Internal Node to Output*/

...

}

}

...

}

多级CCB逻辑单元

对于多级CCB逻辑单元,例如寄存器,噪声建模是基于Pin的 (Pin Based),对于所有inputs都抽取ccsn_first_stage模型,对于outputs抽取ccsn_last_stage模型。如果这种逻辑单元中存在某些input-output的路径只有两级CCB,也可以通过Arc Based方式建模。模型转换框图如下:

寄存器的噪声模型在.lib中大致如下:

pin (CDN) {

...

}

pin (CP) {

...

ccsn_first_stage() {

...

}

}

pin (D) {

...

ccsn_first_stage() {

...

}

}

pin (Q) {

...

timing () {

related_pin: CDN;

...

ccsn_first_stage() { /*Input to Internal Node*/

...

}

ccsn_last_stage() { /*Internal Node to Output*/

...

}

}

...

}

需要注意的,对于Arc Based和Pin Based两种方式,.lib中噪声相关的属性存储的对象是不同的,Arc Based噪声属性是存在对于的Arc中,而Pin Based噪声属性则是与Pin关联的,具体的区别可以参看下面的命令:

#Arc Based Attributes

get_attribute [get_lib_timing_arc -of [get_lib_cell */INV1X]] has_ccs_noise_above_high

#Pin Based Attributes

get_attribute [get_lib_pins -of [get_lib_cell */INV1X]] has_ccs_noise_above_high

噪声分析实战

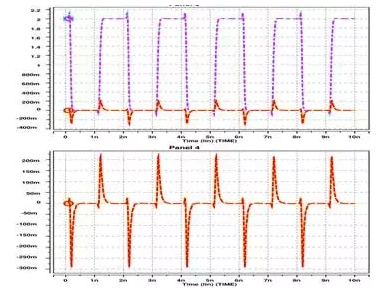

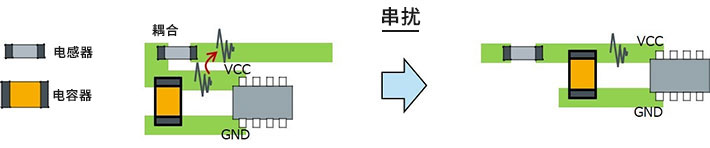

为了进行Noise或者Glitch分析,需要对一个串扰造成的Bump建模,它有宽度和高度,还有面积等属性概念(如下图所示),在分析噪声时可以分别针对height, area, area_percent进行分析,命令如下:

#默认值是height

report_noise -slack_type height

#area=1/2* height * width

report_noise -slack_type area

#area_percent = (constrainted height - actual height) / constrainted height

report_noise -slack_type area_percent

PT-SI在进行update_noise计算时,首先会采用较为悲观的方式快速计算一个类似于下图中DC noise margin的阈值,如果计算出的Bump Height远低于该值,那么就可以断定没有noise不会传播,没有危害。如果计算出的Bump Height接近这个阈值,那么工具就会启动更精细的类似SPICE的门级仿真,取得更精确的结果。通过这种方式,即节省了时间,又保证了精度。

下图中的曲线可以看做是Noise Immunity Curve(NIC),在曲线左下角的Glitch都是无害的,而右上角的Glitch都是必须修复掉的。PT-SI在进行Noise门级仿真时会实时地计算出各个点的NIC,通过PT的GUI界面也可以调出这类图片。

最后,简单聊一聊万一出现的noise违例,我们怎么去修复呢?

这个需要结合受害(victim)和攻击(aggressor) Net相关路径的时序,周围Net和Cell的密集程度等情况来具体分析,大致上有以下方法:

(1)增加受害Net的驱动单元驱动能力

(2)减少受害Net的负载单元驱动能力

(3)增加受害Net和攻击Net的间距

(4)降低攻击Net的驱动单元驱动能力

(5)通过加Buffer将受害Net打断 (工具一般是通过这种方式来修复)

(6)将受害或者攻击Net的驱动单元或者负载单元挪开一定距离,并重新ECO绕线

-

寄存器

+关注

关注

31文章

5343浏览量

120385 -

反相器

+关注

关注

6文章

311浏览量

43321 -

CCSN

+关注

关注

0文章

3浏览量

7088 -

GUI

+关注

关注

3文章

660浏览量

39685 -

SPICE仿真

+关注

关注

1文章

27浏览量

6419

发布评论请先 登录

相关推荐

怎么抑制PCB小间距QFN封装引入的串扰

什么是串扰它的形成原理是怎样的

如何解决PCB串扰问题

如何解决EMC设计中的串扰问题?

串扰是怎么引起的 降低串扰有哪些方法

理解串扰Crosstalk

使用电感降低噪声的注意点:串扰、GND线反弹噪声

讲解串扰引入的噪声(Noise)

讲解串扰引入的噪声(Noise)

评论