本文作者:

DSG Product Engineering Group 刘杰

我们知道,一块芯片的性能通常通过频率、功耗、面积(即 PPA)三个方面去评估。在芯片设计过程中,工程师经常会对频率,面积进行调整,但是很少会对芯片供电网络(即 PG)进行比较大的调整,甚至在一些情况下明知道目前的 PG 可能不是最优的,工程师也没有动力去调整,为什么呢?

因为在传统的设计方法下,想要设计一个满足各方面要求的 PG 网络,是需要花费大量时间的。

“

1

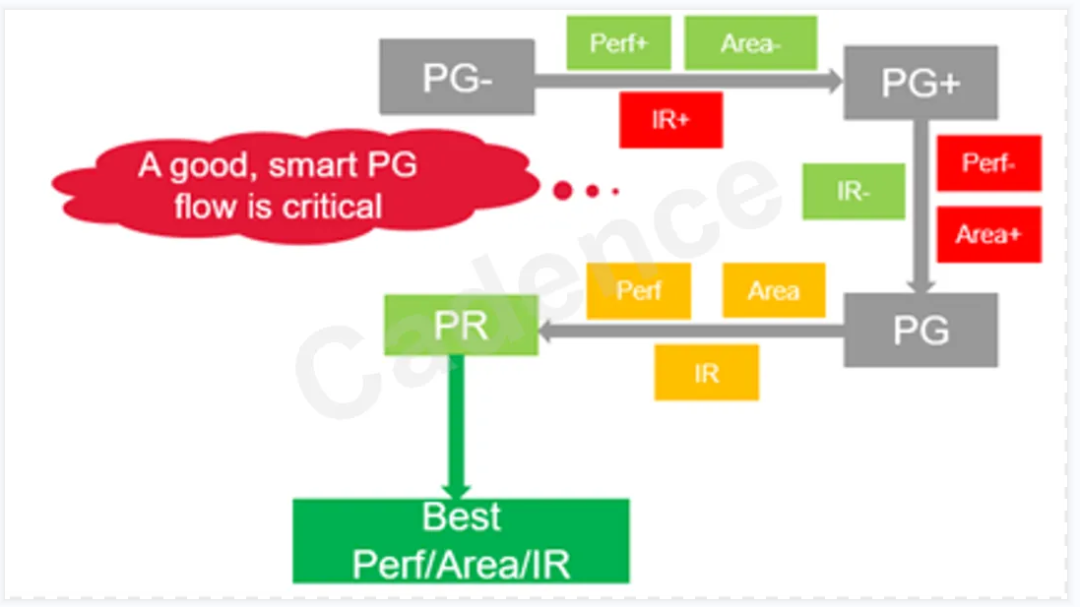

一方面是设计一个合理的 PG 网络本身需要较高的试错成本,工程师需要对其中的每个参数进行精确计算,甚至拼凑才可能得到符合要求的结果。所以一套成熟的 PG 脚本都是经过十几甚至几十个版本的不断打磨迭代最终形成的。

“

2

第二方面是 PG 脚本运行费时,动则十几甚至几十个小时的运行时间,也是设计过程中的一大痛点。

那我们有没有什么解决方案,可以帮助工程师用原来十分之一甚至更少的时间设计出一个合格的电源网络,并且可以根据不同的设计要求快速调整呢?

答案便是由 Cadence 提供的新型电源网络设计方法 —— PSDL。

什么是 PSDL?

PSDL 是 PG Structure Description Language 的简称,顾名思义,它是 Innovus 中一种全新的电源网络结构的描述语言。

PSDL 主要包含两部分的内容:

|

1 |

每层金属电源走线的样式; |

|

2 |

不同层金属电源走线的连接关系。当我们能够把上面两部分的内容都说清楚的时候,芯片的电源网络其实自然就形成了。 |

PSDL 的工作模式以及相比传统 PG 产生

流程,它有什么样的优点?

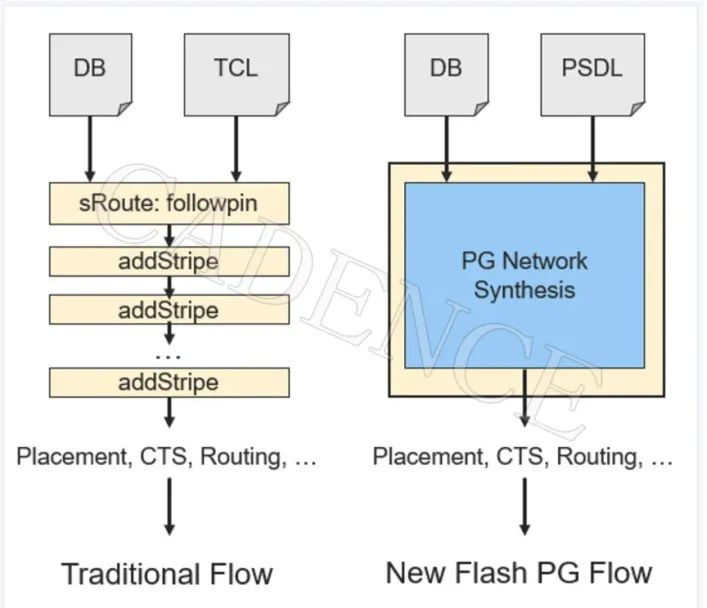

在介绍 PSDL 的优点之前,我们首先对比一下 PSDL 与传统流程的区别。如下图:

传统流程:

在 floorplan 阶段,通过一条条执行以 addStripe 为核心的命令的方式,完成 PG 创建。

PSDL流程:

在 floorplan 阶段,读入完整的 PSDL 文件,然后调用 Innovus 内部的 flash PG 引擎,一次性生成 PG 网络。

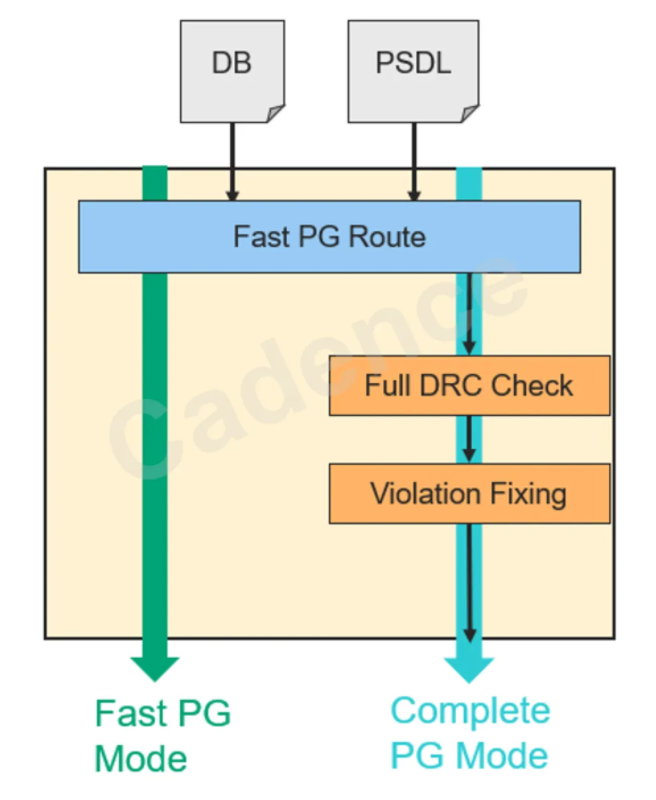

其中 flash PG 引擎工作时又分为两种模式,快速模式(fast mode)和完整模式(complete mode)。其中快速模式用于快速产生 PG,帮助工程师检查 PG pattern 是否符合设计要求并进行功耗分析;完整模式是在快速模式的基础上,工具尝试检查并处理 PG 产生的 DRC,希望可以在修理 DRC 的基础上保证 PG 连接性。工程师可以根据不同的需求场景,选择使用不同的模式,充分发挥 PSDL 的优势。

· PSDL 的优点

❖

相比 TCL 脚本,更加便于理解和书写,便于工程师快速学习应用。

❖

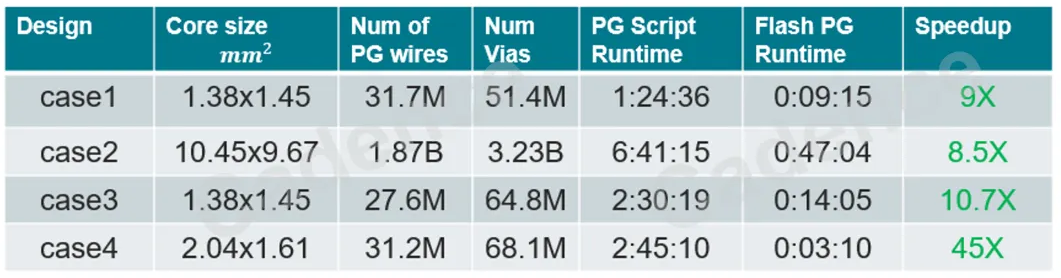

运行速度更快。PSDL 调用新的 Flash PG 引擎可以大幅提升 PG 生成速度,相比传统的 addStripe 脚本方式普遍可以提升 10 倍左右。

❖

通用性高,不依赖于芯片的大小及 floorplan 等信息。针对不同的设计需求,不同的工艺,通过一些微小的调整可以实现快速迁移复用。

❖

自动从 LEF 文件中提取不同层金属的物理信息。减少工程师重复的测量,计算等基础工作,让工程师有更多精力专注在 PG 结构设计方面。

下面是不同客户的实际案例测试结果,发现新的 Flash PG 引擎在运行速度方面普遍可以提升 10 倍左右。同时我们也发现,当芯片的 PG 结构越复杂,并且造成传统 PG 脚本越臃肿时(如 case 4),PSDL 展现出的优势也更加明显。

· PSDL 包含哪些内容?

一个完整的 PSDL 文件主要包括 VARIABLE、PATTERN、AREA、REGION。其中,PATTERN 和 REGION 是必须的部分,其他部分可以根据实际情况进行增减。

❖

PATTERN:

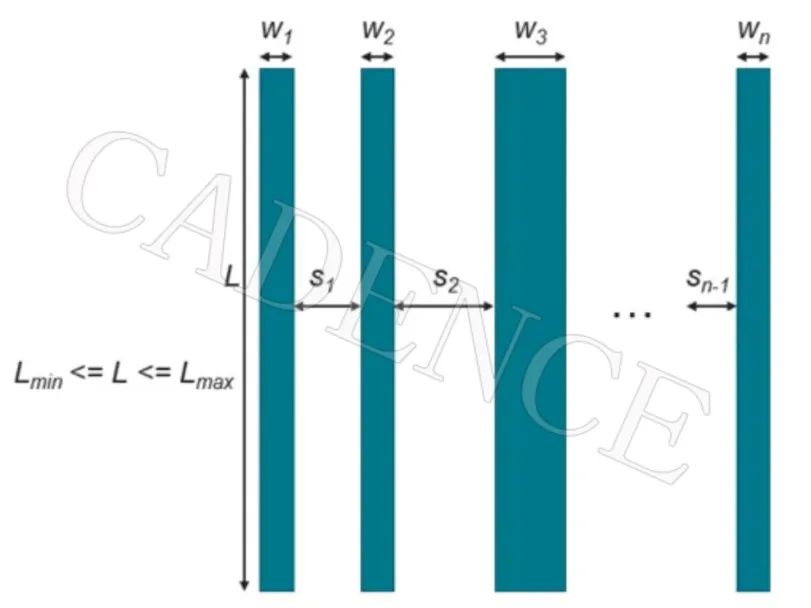

用于描述 PG 中每一层金属走线的具体结构样式;包括名称,类型,走线方向,线宽,间距,长度等基础信息。

❖

REGION:

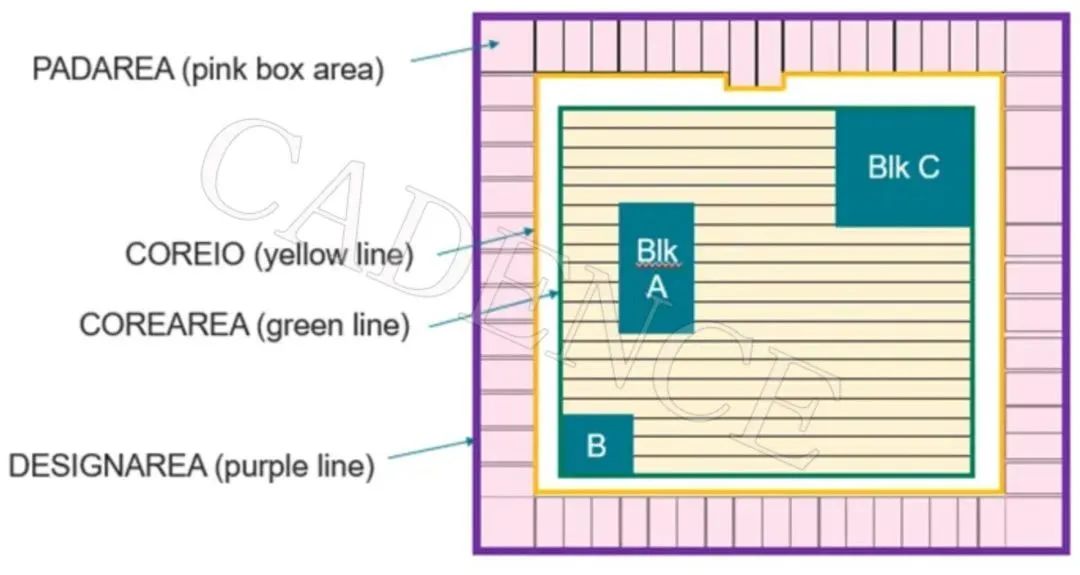

用于描述在一个具体的区域,产生某种类型的 PG 网络结构,主要包括所选区域,金属层信息等。其中区域选择可以是芯片中的任何区域,比如一个 block,instance,或者是一个 cell。这种通过单个指令便可实现在特定区域产生 PG 的方式,大大减轻了传统方式中用脚本命令进行面积计算的工作量,进一步提升工作效率,减少工具运算时间。

❖

METAL:

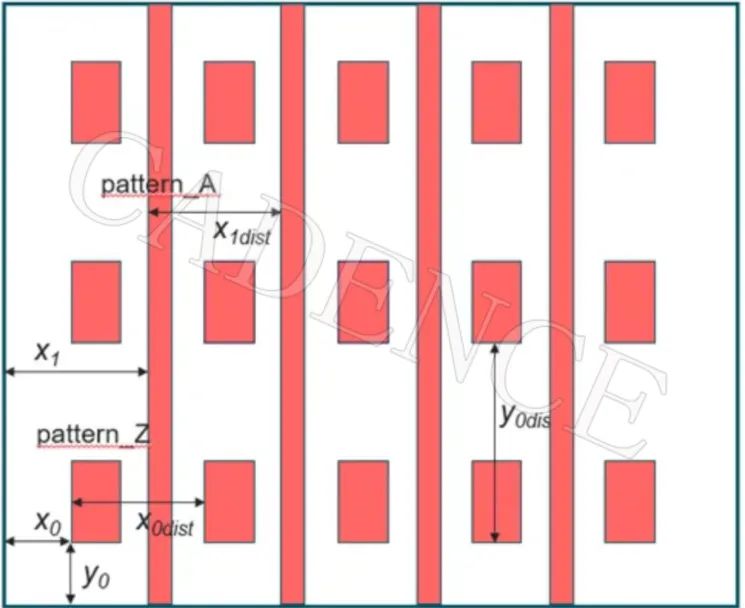

用于描述具体的一层中,所走金属线的类型及位置。如下图,表示在选定区域中,M3 上面vdd 使用前面定义的 pattern_Z(STAPLE类型)和 pattern_A(STRIPE)。其中初始偏移量、间距、数量可以由 OFFSET、STEPDISTANCE、SIZE 等进行定义。

❖

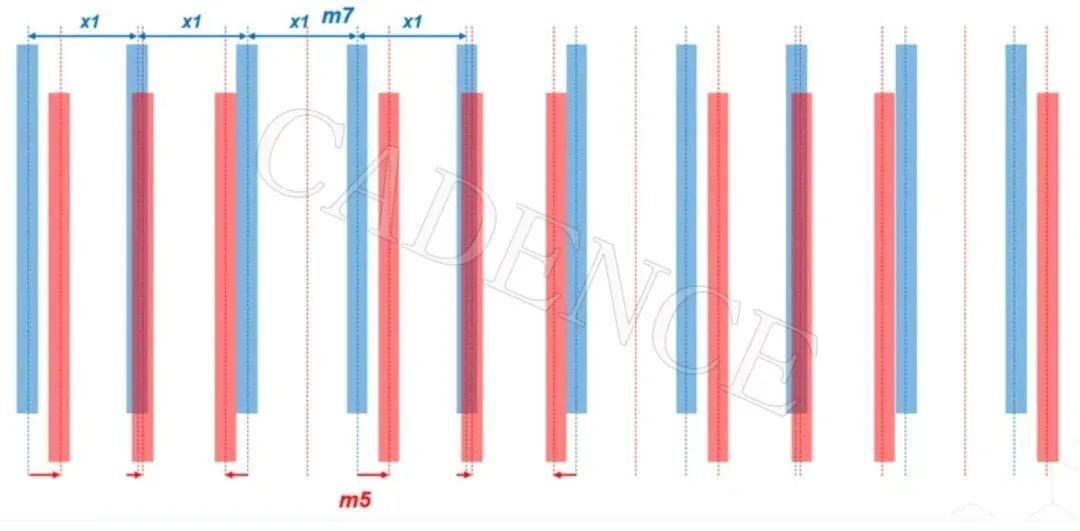

FOLLOW 和 ALIGNMENT:

作为 PSDL 中的另一大亮点,工程师可以通过 FOLLOW 和 ALIGNMENT 描述不同金属线的相对位置关系,实现更加智能化的 PG 设计。通过这种方式,不但可以减少不必要的手动计算工作,也可以保证不同层之间的连接性,同时在需要调整时也非常容易。

PSDL 相比传统方式,不但在运行速度上展现出巨大优势,而且使得电源网络设计更容易,维护和更新更方便灵活,它将对目前的后端实现流程产生影响。未来,PSDL 将和机器学习技术紧密融合,助力芯片工程师进一步提高芯片 PPA 的同时,有效解决电压降过大等电源网络问题。

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站www.cadence.com。

2023 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

-

Cadence

+关注

关注

65文章

931浏览量

142555

原文标题:更快,更强,更智能:Cadence 新型电源网络设计方法介绍

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SOLIDWORKS 2025更强劲的性能优势简介

Wolfspeed荣获世纪电源网行业大奖

一文解析LISN人工电源网络

吹田电气(深圳)有限公司亮相电源网(亚洲)工程师技术高峰论坛

更快、更小、更节能,开关电源迎来测试挑战

4G新型智能电表是什么?

网络模块的安装方法

人工智能神经网络芯片的介绍

Cadence扩充系统IP产品组合,推出NoC以优化电子系统连接性

没开玩笑!高速信号不能参考电源网络这条规则,其实很难做到

没开玩笑!高速信号不能参考电源网络这条规则,其实很难做到

海洋仪器参加电源网2024年高新电源技术研讨会-北京站圆满结束

更快,更强,更智能:Cadence 新型电源网络设计方法介绍

更快,更强,更智能:Cadence 新型电源网络设计方法介绍

评论