我们常用的debug UVM的方法是通过打印log实现。有没有办法像 debug RTL代码一样将 UVM 中变量拉到波形上看呢?答案是有的,下面让我们看看是怎么做到的。

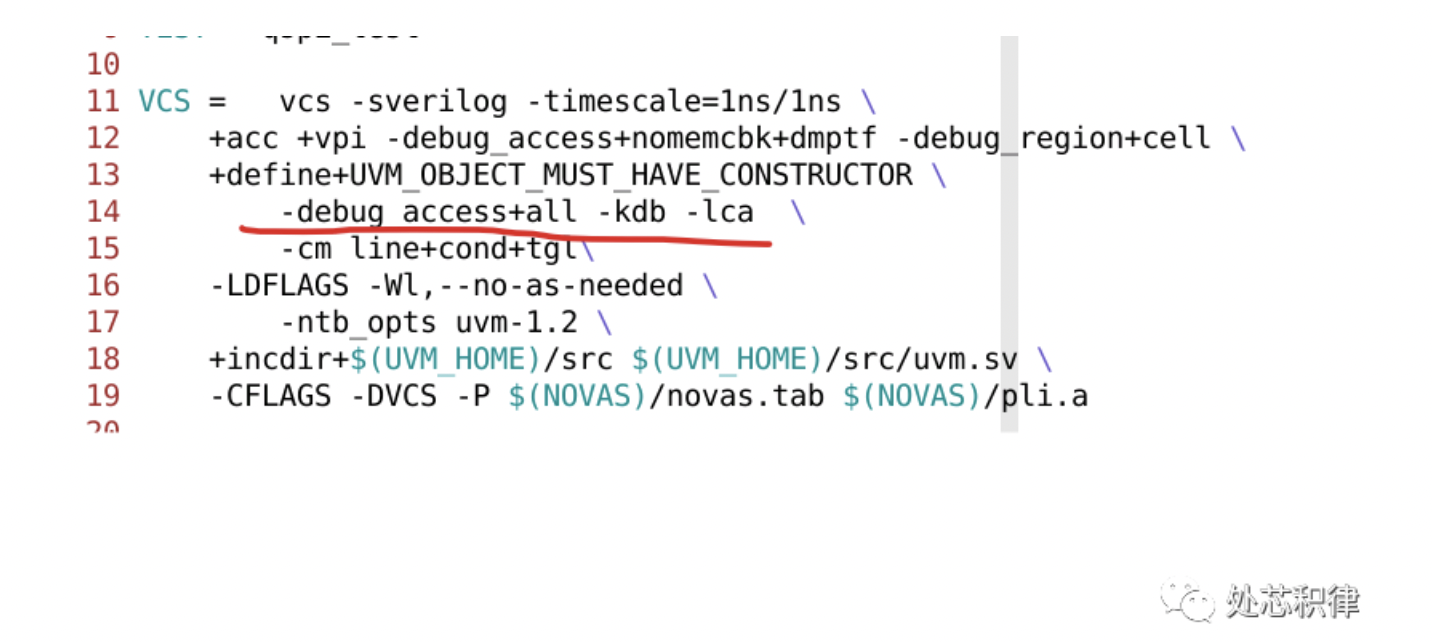

第一步在UVM compile 的选项里面加入 -debug_access+all

第二步在 simulation 选项中加入下面三个选项

-gui=verdi

** +UVM_VERDI_TRACE="UVM_AWARE+RAL+HIER+COMPWAVE"**

+UVM_TR_RECORD

这里 -gui=verdi是启动verdi 和vcs联合仿真。+UVM_VERDI_TRACE 这里是记录 UVM中 register,component 的波形。+UVM_TR_RECORD记录 transaction的信息。

我们 编译完之后,然后开始跑仿真。跑仿真的时候会跳出下面verdi的界面。

接下来点击绿色的箭头就可以跑仿真

跑完仿真之后,我们点击Verdi 里面 UVM这个地方,会出现UVM的环境。

下面我们看下 uvm component里面的信息,通过指定一个 component 然后右击 add to waveform 就可以看 component的信息。

Sequence里面的信息怎么看呢?下面点击sequence view 就可以看 sequnce的信息。

我们要看sequence里面的一个变量变化,可以这么做。

先将一个object或者一个sequence 添加到watch中。

从这个watch中的object或者sequence里面选择一个变量到 waveform上。重跑simulation,就可以看到对应添加变量的值值。

下面是我们在波形上看到sequence里面变量的信息

看register model里面的值也是类似的做法,找到 register view,然后找到 register model 添加 register 到 waveform里面。

重跑simulation,就可以看到register值。

用verdi debug UVM总体感觉比较麻烦,个人还是喜欢打印log的方式debug。

-

仿真器

+关注

关注

14文章

1018浏览量

83736 -

RTL

+关注

关注

1文章

385浏览量

59771 -

UVM

+关注

关注

0文章

182浏览量

19169

发布评论请先 登录

相关推荐

有没有办法像debug RTL代码一样将UVM中变量拉到波形上看呢?

有没有办法像debug RTL代码一样将UVM中变量拉到波形上看呢?

评论