开始之前,我们首先来看一下什么是时钟门控(clock gating)技术,顾名思义就是利用逻辑门技术控制时钟的通断。

那么为什么需要控制时钟的通断呢?主要基于以下几个原因。首先,随着工艺的发展和设计规模的增大,时钟树上产生的功耗占整个SoC功耗的比例越来越高,有时几乎能占到50%左右。关于时钟树,可能前端的同学不熟悉,简单说几句,SoC的时钟一般是参考时钟经过PLL和数字分频器输出的,后面可能要连接驱动成千上万的寄存器clock端。

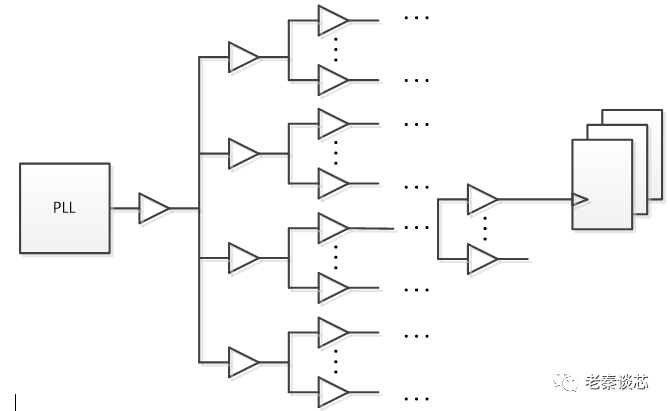

这时候任何一个单一的cell都不可能有这么大的驱动能力,因此要插入大量的buffer,而且为了保证到每个寄存器的延时一样,clock tree还要做balance。整个的时钟树大概长成下图这样,第一级buffer叫root,中间的buffer叫branch,最后一级的buffer叫leaf:

图1 时钟树示意图

如果我们的芯片在不工作时,PLL依然有clock输出的话,那整个时钟树依然产生很大的功耗。

接下来我们再看一下边沿触发器的结构图。从图上我们能看出即使D端保持不动,clock端变化也会消耗一些能量。想深入研究的同学可自行推导(可以忽略两个复位信号)。

图2 边沿D触发器

那么当D端长时间不变时,是不是可以把CP端的变化隔离掉以降低功耗呢?答案是肯定的。

最简单的办法就是把clock信号和一个EN信号做“与”操作,如下图:

图3 简单的时钟门控逻辑

这个方法虽然简单,但是如果我们不能保证EN信号相对clock的到来时间和保持时间,那么就很可能不能产生门控时钟或者产生毛刺(glitch)。为了解决这个问题,人们提出了基于锁存器的时钟门控逻辑。由于锁存器能捕捉到EN信号并使它保持到产生完整的时钟脉冲,因此EN信号只需要在时钟活跃沿附近保持稳定即可。使用这种技术,每次只需要改变门的一个输入端来打开或关闭时钟就能保证电路的输出不含有任何毛刺或者尖峰脉冲了。

图4 基于锁存器的时钟门控

现在的芯片生产商会提供时钟门控的标准单元,为了DFT测试的需要,标准门控单元还会带着test_en这种输入信号,今天为了不跑题就不介绍相关内容了。

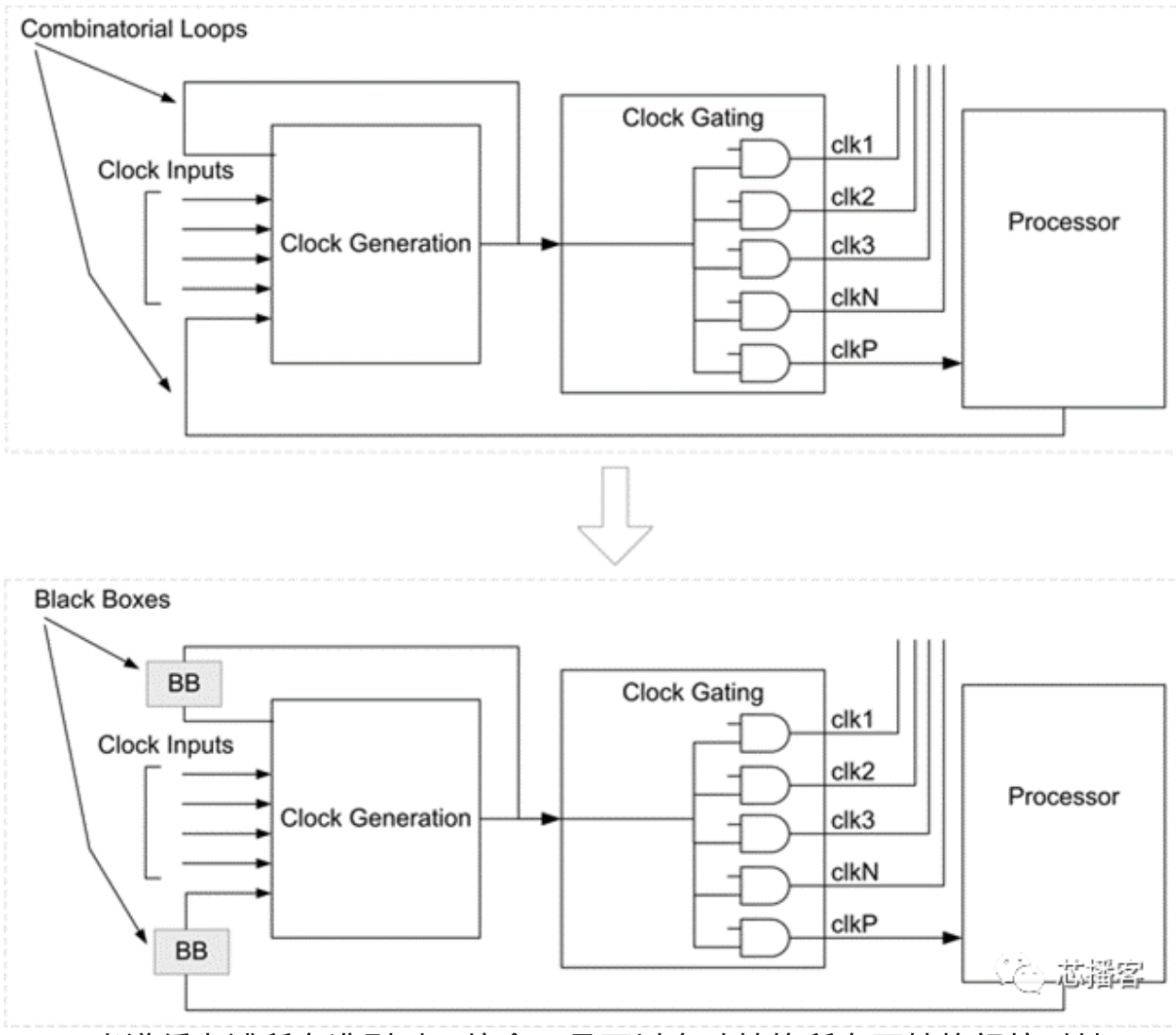

接下来就是架构师和逻辑设计工程师关心的问题了,怎么设计门控逻辑。在SoC设计中,可以实现三种粒度的时钟门控设计,首先是粗粒度的设计,架构师要决定如何在时钟产生单元增加门控逻辑,根据SoC工作情况来判决是否关断某个时钟输出。这里提供一个思路,先根据功能划分出clock domain,然后再根据每个模块/IP之间的关系制定一张表,用于决定每个时钟域的开启和关闭状态。

有了这张表就相当于有了一个状态机,根据状态机的当前状态决定时钟是否关闭。至于状态跳转的判决,可以是硬判决也可以是软判决。硬判决的好处是相对速度快;缺点是灵活性较差,而且设计相对复杂,往往需要模块/IP有接口信号可用。软判决刚好相反,优点是灵活性高;缺点是延迟比较大,不适于频繁开关,对于某些设计来说,实现软判决还要增加处理器,毕竟不是所有SoC都有CPU/MCU/DSP的。

其次是中等粒度的设计,模块设计师来决定是否关断内部子模块的时钟输入。这里没啥好说的,完全取决于模块的功能和实现方案了。

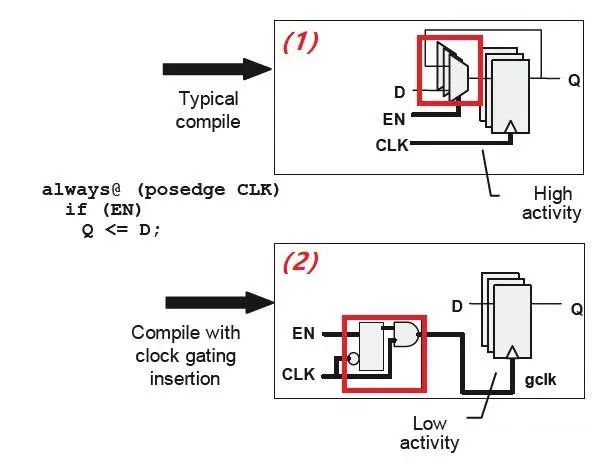

最后,可以在逻辑综合阶段,由综合工具自动插入门控单元。前面两条依赖具体设计,最后一条不完全依赖设计,再多说几句。如果RTL代码写成下图左边的样子,在逻辑综合时不打开插CG的选项,综合出的电路如中图所示;而打开插入CG的选项,就会综合出下图右边的电路。由于CG单元本身也会产生功耗,一般一个CG单元后面要接多个寄存器才能达到节省功耗的效果。一般在综合时会通过选项选择3或4个。

图5 综合插入CG的示意图

对于综合工具,其插入CG的判定很简单,就是看有没有上图代码中的enbale逻辑。如果没有就不插。所以如果逻辑设计师想要写出满足低功耗需求的RTL代码,就要尽量在代码中使用类似上图的enable逻辑。可能有喜欢刨根问底的同学要提问了“如果我的某段逻辑就没有enable怎么办?”这种情况下,可以试着向前或者向后找一找,有没有哪些逻辑可以借用过来。比如下图例子,绿色虚线代表可以增加的逻辑。RTL低功耗设计方法有很多,大家可以百度一下,或者等我以后写(此处有坑)。

图6 前向借用逻辑产生时钟门控信号

最后,要说明一个关于clock gating的误区。时钟门控固然可以节省功耗,但并不是越多越好。当CG cell达到一定数量时,再增加CG cell对功耗节省的效果就不明显了。而且如前面所说,CG cell本身也是要产生功耗的,数量太多的话肯定要消耗不少,而且还会占用大量的面积,过犹不及。(再一次体现出做SoC的balance艺术,还是那句话,没有完美的SoC,只有完美的tradeoff)

图7 CG数量与节省功耗的关系

结束前总结一下,clock gating技术对整体SoC设计的影响。

表1 低功耗技术总结

-

寄存器

+关注

关注

31文章

5620浏览量

130443 -

分频器

+关注

关注

43文章

537浏览量

53769 -

SoC设计

+关注

关注

1文章

151浏览量

19609 -

时钟门控

+关注

关注

0文章

8浏览量

7081 -

PLL电路

+关注

关注

0文章

94浏览量

7140

发布评论请先 登录

什么是时钟门控?如何去实线时钟门控的设计呢

门控时钟与时钟偏移研究

什么是时钟门控技术?为什么需要控制时钟的通断呢?

什么是时钟门控技术?为什么需要控制时钟的通断呢?

评论