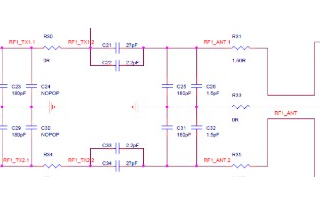

PA 调试block

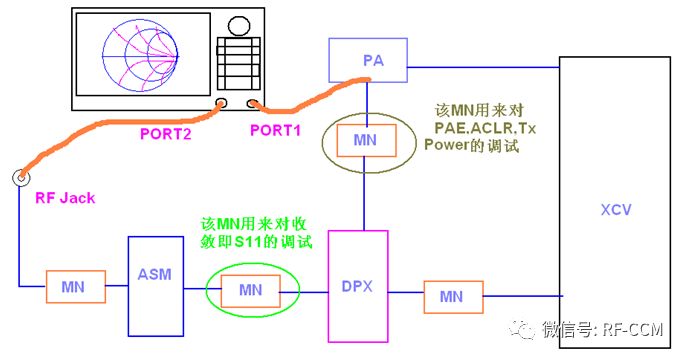

图1 RF Block

PA RF cable焊接

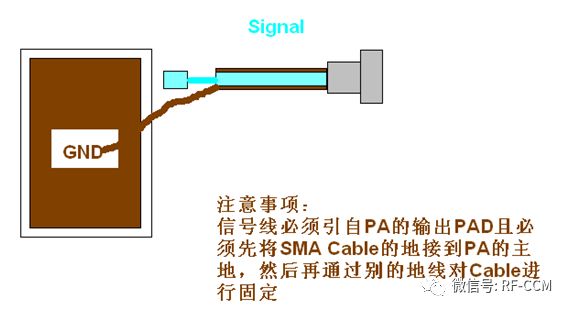

图2 PA接线方式

PA匹配****调试具体步骤如下:

- 校准VNA并做测试Cable的延迟校准。即将Cable连接到VNA后通过校准程序,将其校准到Smith Chart右端开路点,完成延迟补偿

- 焊接Cable,如上图2注意事项,先将PA用热风枪拿掉,然后将Cable的信号线接到PA的输出引脚PAD上,将Cable的地接到PA封装的主地上。然后再连到易于连接到的地上固定Cable。

- 以上图1示例如何调试PA,上图1的VNA两个端口接线分别为Port1→PA output PAD,Port2→RF Jack,所以S11即从PA output到RFJack的收敛性。而S21为Port1到Port2的IL(好的IL通常为3.2左右的样子),S21可用来判断测试路径是否是通的。

若收敛差的话则需要调节DPX ANT端口的MN,调试完DPX ANT端口的MN后还需确定是否对Rx Path产生影响。因为Port1在PA输出端,Port2在RFJack端,所以通过匹配,可以调试整条Tx链路的收敛,Tx Path的收敛决定了功率的平坦度。

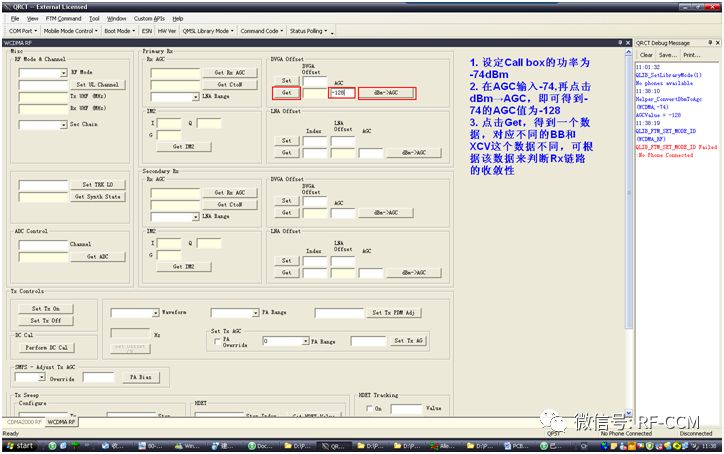

如下图示可用来确认Rx Path的影响。因为这样调试的时候S11经过了DPX,所以在调试收敛的时候不能以常规的并/串元件在Smith Chart上移动的方向来确认S11,经过DPX后很难预测S11走向,调试后需要用VNA进行验证。

- 经常会遇到ACLR的问题,首先可以盲调PA的MN,若是PA的MN与PA放置较远的话可以考虑并联电感,若是紧挨PA放置的话并联电感的效果较差。再就是找多家PA看看,最后查看PA供电是否稳定,电源是否受到干扰。

- 对比厂商提供的Load Pull的数据调试对应的MN来 优化ACLR,PAE,Tx Power要做好三者的均衡 ,通常按中信道Load Pull数据来调试PA输出的MN,在实际信令情况下测试时候需看三个信道的具体情况。

由于要考虑高低温,所以对ACLR应留有足够的余量,温度会对ACLR影响较大。

考虑到温度上升带来的Noise影响,估计能恶化2dB的ACLR性能,但是HSDPA由于其高的PAPR,所以对于HSDPA高温时候ACLR的恶化不便于估计,尽量调试ACLR<-39。实际中遇到过在用RFMD的7225调试时候,不管怎么改变匹配电路,其ACLR的变化很少。考虑两个方面:

1 PA电源问题

但是W2100&W1900均用同一组电源,这两个Band的ACLR均<-40,所以考虑电源问题似乎不太合适。

2.器件本身问题

经调试MN无效后更换该PA为ANADIGICS的AWU6605后其ACLR表现极佳,±5M为-47~-48,所以该问题是器件本身性能不太理想,再加之PCB Layout的寄生影响导致ACLR结果不如意。

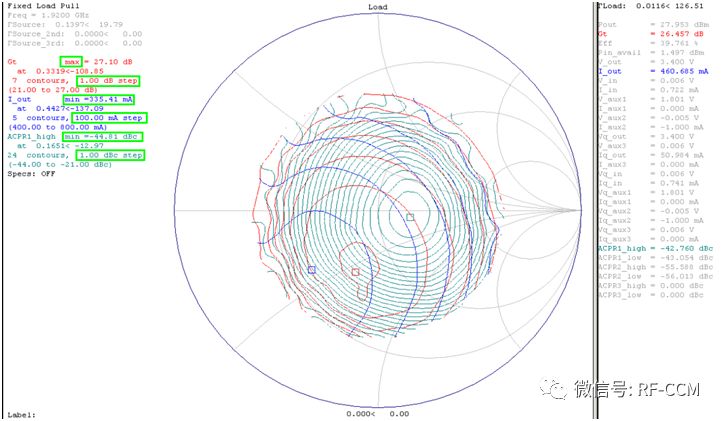

PA Loadull示例

蓝框:如上图左所示为电流最小的点,蓝色的等高线代表了等电流点,100.0mA每Step

红框 :如上图左所示为功率最大的点,红色线等高线代表了等功率点,各等高线间的间隔为1dB

绿框 :如上图左所述为ACLR最小的点,水绿色等高线代表了等ACLR点,各等高线间隔为1.00dBc

三个框会围成一个三角形,将PA的load往三角形内调是均衡三者的性能表现。

具体情况,具体参考loapull分析调试。

盲调小修是必要的。

-

RFMD

+关注

关注

1文章

71浏览量

21843 -

HSDPA技术

+关注

关注

0文章

3浏览量

5384 -

VNA

+关注

关注

0文章

34浏览量

16566 -

DPX

+关注

关注

0文章

4浏览量

8933 -

ACLR

+关注

关注

0文章

12浏览量

8142

发布评论请先 登录

相关推荐

聊聊Rust与C语言交互的具体步骤

请问UCGUI中移植触摸的具体步骤是什么?

阻抗匹配调试方法能改善吗?

学电机的具体步骤

西门子V20变频器PID控制恒压供水的具体步骤

PA匹配调试具体步骤

PA匹配调试具体步骤

评论