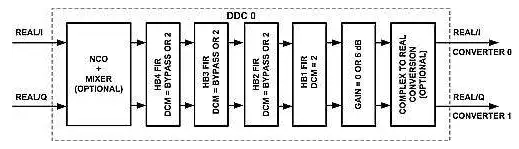

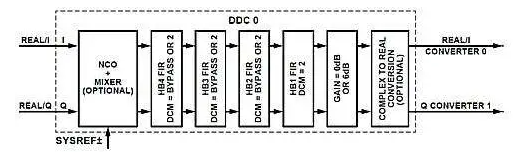

回想一下示例中,AD9680-500的工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680设置为使用数字下变频器(DDC),具有实输入、复数输出、155 MHzNCO调谐频率、半带滤波器1(HB1)和半带滤波器2(HB2)(总抽取率等于6)和<>dB增益。由于输出很复杂,因此禁用了复杂到实际的转换块。再一次,让我们看一下 DDC 的基本图表,下面包含该图表以作为复习。回想一下,信号首先通过NCO,NCO在频率上移动输入音,然后通过抽取滤波器,然后通过增益模块,在我们的例子中,绕过复数到实际转换。

AD9680中的DDC信号处理模块

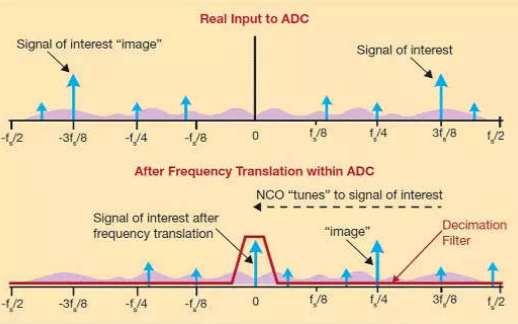

让我们重新审视一下如何使用频率折叠工具来了解ADC的混叠效应。这将有助于评估模拟输入频率及其谐波在频域中的位置。在本例中,我们有一个真实信号,采样率为491.52 MSPS,抽取率设置为<>,输出很复杂。在ADC的输出端,在进入DDC之前,信号如下图所示,使用频率折叠工具。

ADC输出端的信号,由频率折叠工具示出

输入采样时钟为491.52 MHz,模拟输入频率为150.1 MHz,基波输入音位于第一奈奎斯特区。输入频率在300.2 MHz处的二次谐波将在191.32 MHz处混叠进入第一奈奎斯特区。450.3 MHz的第三次谐波混叠为41.22 MHz,也位于第一奈奎斯特区。这是ADC输出端的信号在通过AD9680DDC中的任何数字处理模块之前的状态。

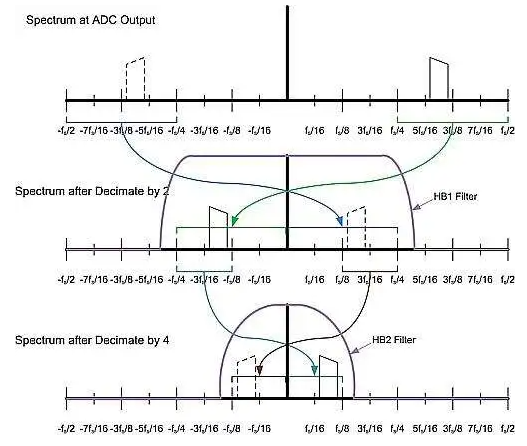

让我们看看信号如何通过DDC内部的数字处理模块。该图是根据输入采样速率、491.52 MSPS 和 fS条款将与此采样率有关。让我们观察一下一般过程。在这种情况下,不显示NCO频移,因为重点是抽取滤波。一旦复数(负频)域中的信号移位超过–fS/2它将折回第一个奈奎斯特区。接下来,信号通过第一个抽取滤波器HB2,该滤波器抽取<>倍。与我之前关于此主题的博客文章相比,我在此图中展示了抽取过程,包括滤波器响应。

在第一次抽取两倍后,频谱从fS/4 至 fS/2转换为 – f 之间的频率S/4和 DC。同样,从 – f 的频谱S/2 至 – fS/4转换为直流和f之间的频率S/4.信号现在通过第二个抽取滤波器HB1,该滤波器也抽取<>(总抽取现在等于<>)。f之间的光谱S/8和 fS/4现在将转换为 – f 之间的频率S/8和 DC。同样,– f 之间的频谱S/4和 – fS/8将转换为 DC 和 f 之间的频率S/8.

请注意,在这个通用示例中,频率规划可能会好一点,因为HB2抽取滤波器会稍微衰减频带中较高频率的含量。这是由图中“抽取 4 后的频谱”部分给出的。另外,请注意,滤波器响应是实际响应的近似值,但可能与AD9680数据手册中显示的曲线不完全匹配。我在这里展示响应是为了给出一个表示,以帮助我们了解我们应该大致期望频率衰减的位置。请注意,HB1 的滚降比 HB2 更清晰。在AD9680数据手册中抽取滤波器响应图中也可以观察到这一点。

信号通过DDC信号处理模块时的信号 – 抽取滤波的通用示例

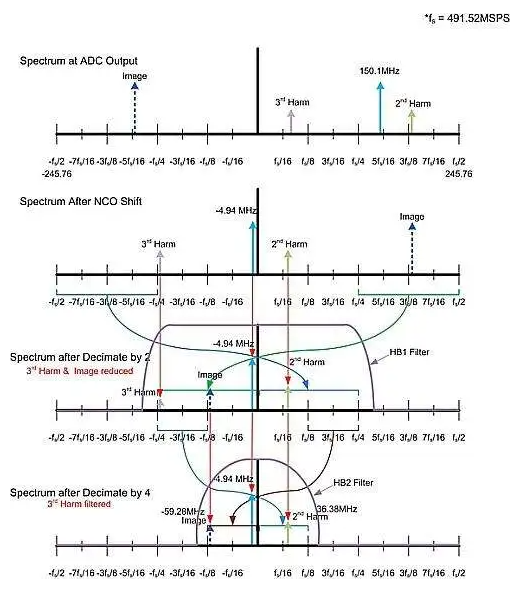

正如我们之前所做的那样,我们将从通用示例中获取信息,并使用它来查看实际频率。让我们看一下频率折叠工具中的ADC输出曲线,其中输入采样率为491.52 MSPS,输入频率为150.1 MHz。 注意:在我一月份的博客文章中,这个音调在图“信号通过DDC信号处理模块时”中被错误地显示为153.1Mhz。NCO 频率为 155 MHz,抽取率设置为 154(由于 NCO 分辨率,实际 NCO 频率为 94.122 MHz)。这导致输出采样速率为88.<> MSPS。由于我们正在进行复杂的混频,因此我们需要在分析中包括复杂的频域。请耐心等待,因为显示频率转换的图非常繁忙,但让我们尝试通过信号流。请注意,抽取滤波器响应已添加,并以深紫色显示。

信号通过DDC信号处理模块时的信号 – 显示抽取滤波

NCO 转移后的频谱:

基频从 150.1 MHz 向下移动到 -4.94 MHz。

基本面的图像从-150.1 MHz偏移到186.48 MHz。

二次谐波从191.32 MHz向下移动到36.38 MHz。

三次谐波从41.22 MHz向下移动到-113.72 MHz。

被 2 抽取后的频谱:

基频保持在-4.94 MHz。

基波镜像向下转换为-59.28 MHz,并由HB2抽取滤波器衰减。

二次谐波保持在36.38 MHz。

三次谐波由HB2抽取滤波器衰减。

被 4 抽取后的频谱:

基本频率保持在-4.94 MHz。

基波镜像保持在-59.28 MHz,并由HB1抽取滤波器衰减。

二次谐波保持在-36.38 MHz,并由HB1抽取滤波器衰减。

三次谐波被HB1抽取滤波器滤除并几乎消除。

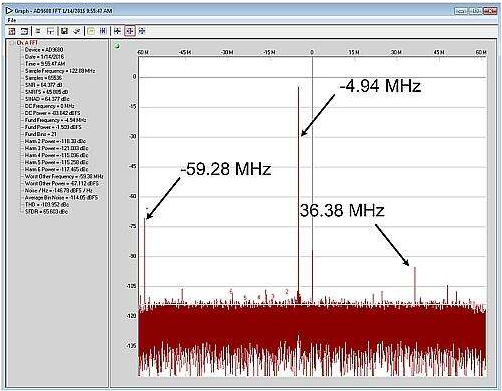

现在让我们回顾一下AD9680-500的实际测量结果。基频为-4.94 MHz。基波图像位于-59.28 MHz,振幅为-67.112 dBFS,这意味着图像已衰减约66 dB。二次谐波位于36.38 MHz,衰减了约10至15 dB。第三次谐波经过充分滤波,在测量中不会超过本底噪声。

NCO = 155 MHz 并抽取 4 时 DDC 后信号的 FFT 复数输出图

从FFT中,我们可以看到AD9680-500的输出频谱,DDC设置为实际输入和复数输出,NCO频率为155 MHz(由于NCO调谐字中的位数,实际为154.94 MHz),抽取率为9680。

审核编辑:郭婷

-

滤波器

+关注

关注

160文章

7703浏览量

177421 -

adc

+关注

关注

98文章

6391浏览量

543732 -

NCO

+关注

关注

0文章

22浏览量

24642

发布评论请先 登录

相关推荐

数字下变频器的发展和更新(第一部分)

数字下变频中抽取滤波器的设计及FPGA实现

基于FPGA的数字下变频器的设计与实现

基于FGPA实现数字下变频器的抽取滤波器设计方案详解

如何在数字下变频实现FPGA

基于FPGA的数字下变频器(DDC)的设计

数字下变频器是怎么回事

下变频器输入信号幅度对下变频的影响

ADC数字下变频器:复杂抽取示例

ADC数字下变频器:重新审视复杂的抽取示例

ADC数字下变频器:重新审视复杂的抽取示例

评论