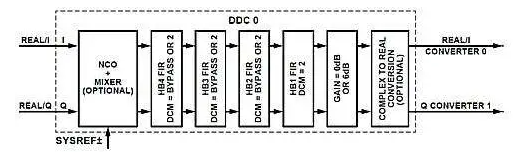

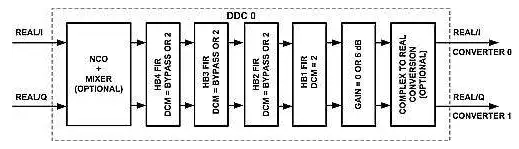

在本例中,我们将介绍AD9680-500,其工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680将设置为使用数字下变频器(DDC),具有实际输入、复数输出、155 MHz的NCO调谐频率、半带滤波器1(HB1)和半带滤波器2(HB2)(总抽取率等于6)和<>dB增益。由于输出很复杂,因此禁用了复杂到实际的转换块。回想一下我之前的博客中DDC的基本图表,下面再次包含该图表。为了理解输入音调的处理方式,重要的是要了解信号首先通过NCO,NCO在频率上移动输入音调,然后通过抽取,通过增益模块,在我们的例子中,绕过复数到实际转换。

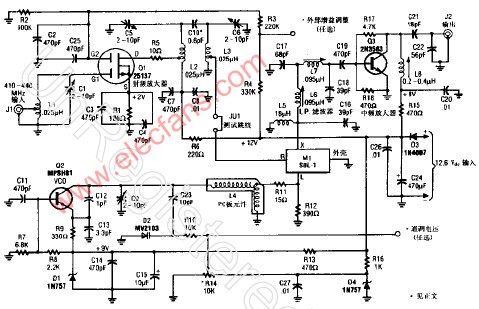

AD9680中的DDC信号处理模块

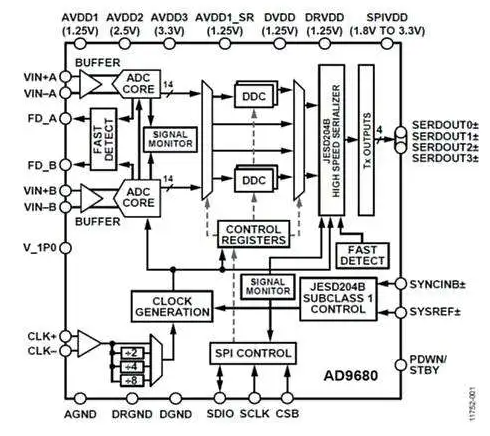

我们还回顾一经AD9680的信号流的宏观视图。如前所述,信号通过模拟输入进入,通过ADC内核进入DDC,通过JESD204B串行器,然后通过JESD204B串行输出通道输出,如下图所示。

AD9680 原理框图

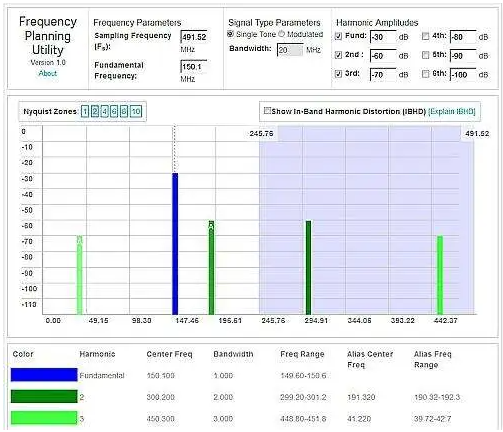

我们将再次使用频率折叠工具来帮助了解ADC的混叠效应,以评估模拟输入频率及其谐波在频域中的位置。在本例中,我们有一个真实信号,采样率为491.52 MSPS,抽取率设置为<>,输出很复杂。在ADC的输出端,信号如下图所示,使用频率折叠工具。

ADC输出端的信号,由频率折叠工具示出

输入采样时钟为491.52 MHz,模拟输入频率为150.1 MHz,输入信号将驻留在第一奈奎斯特区。输入频率的二次谐波将在191.32 MHz处混叠到第一个奈奎斯特区,而第三个谐波混叠到41.22 MHz,这也在第一个奈奎斯特区。这是ADC输出端的信号在通过DDC之前的状态。

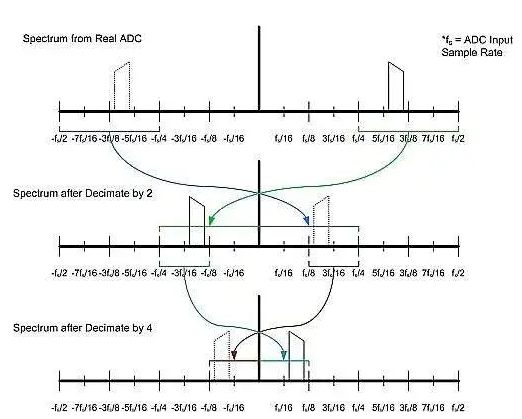

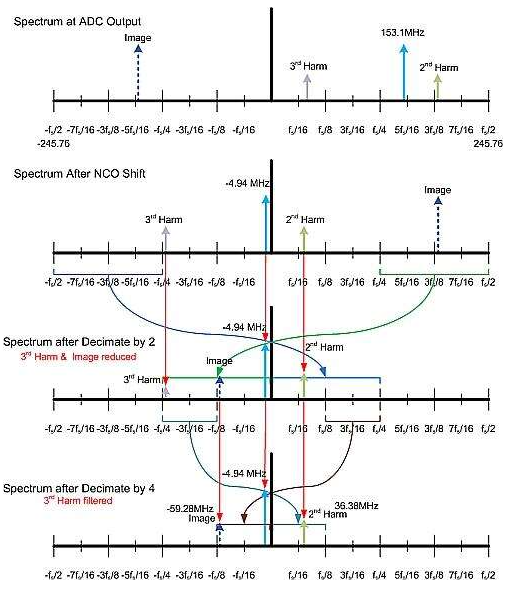

现在让我们看看信号如何通过DDC内部的数字处理模块。我们将观察信号经过每个阶段的过程,并观察NCO如何移动信号以及抽取过程随后折叠信号。我们将根据输入采样率、491.52 MSPS 和 f 来维护该图。S条款将与此采样率有关。让我们观察一下一般过程。NCO 会将输入信号向左移动。一旦复数(负频)域中的信号移出 – fS/2它将折回第一个奈奎斯特区。接下来,信号通过第一个抽取滤波器HB2,该滤波器抽取<>倍。

在图中,我显示了抽取过程,但没有显示滤波器响应,即使操作一起发生。这是为了简单起见。在第一次抽取两倍后,频谱从fS/4 至 fS/2转换为 – f 之间的频率S/4和 DC。同样,从 – f 的频谱S/2 至 – fS/4转换为直流和f之间的频率S/4.信号现在通过第二个抽取滤波器HB1,该滤波器也抽取<>(总抽取现在等于<>)。f之间的光谱S/8和 fS/4现在将转换为 – f 之间的频率S/8和 DC。同样,– f 之间的频谱S/4和 – fS/8将转换为 DC 和 f 之间的频率S/8.尽管图中显示了抽取,但未显示抽取滤波操作。

信号通过DDC信号处理模块时的信号 – 通用示例

现在让我们研究上面讨论的示例并查看实际频率。回到频率折叠工具中的ADC输出曲线,我们将查看491.52 MSPS的输入采样速率和150.1 MHz的输入频率。NCO 频率为 155 MHz,抽取率设置为 154(由于 NCO 分辨率,实际 NCO 频率为 94.122 MHz)。这导致输出采样速率为88.<> MSPS。由于我们正在进行复杂的混频,因此我们需要在分析中包括复杂的频域。请耐心等待,因为显示频率转换的图非常繁忙,但让我们尝试通过信号流。

通过DDC信号处理模块时的信号

NCO 转移后的频谱:

基频从 150.1 MHz 向下移动到 -4.94 MHz。

基本面的图像从-150.1 MHz偏移到186.48 MHz。

二次谐波从191.32 MHz向下移动到36.38 MHz。

三次谐波从41.22 MHz向下移动到-113.72 MHz。

被 2 抽取后的频谱:

基频保持在-4.94 MHz。

基波镜像向下转换为-59.28 MHz,并由HB2抽取滤波器衰减。

二次谐波保持在36.38 MHz。

三次谐波被HB2抽取滤波器显著衰减。

被 4 抽取后的频谱:

基本频率保持在-4.94 MHz。

基本面的图像保持在-59.28 MHz。

二次谐波保持在-36.38 MHz。

三次谐波被HB1抽取滤波器滤除并几乎消除。

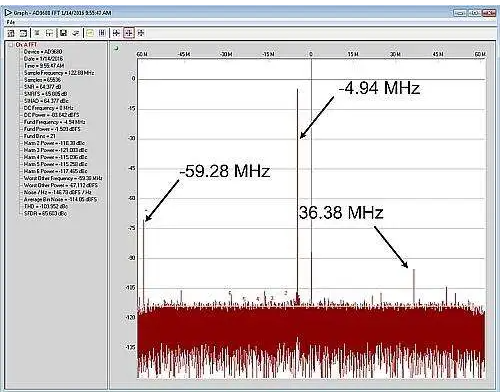

现在让我们看一下AD9680-500的实际测量结果。我们可以看到基本面位于-4.94 MHz。基波图像位于-59.28 MHz,振幅为-67.112 dBFS,这意味着图像已衰减约66 dB。二次谐波位于36.38 MHz。

NCO = 155 MHz 并抽取 4 时 DDC 后信号的 FFT 复数输出图

从FFT中,我们可以看到AD9680-500的输出频谱,DDC设置为实际输入和复数输出,NCO频率为155 MHz(实际154.94 MHz),抽取比为4。

审核编辑:郭婷

-

滤波器

+关注

关注

161文章

7824浏览量

178167 -

变频器

+关注

关注

251文章

6558浏览量

144811 -

NCO

+关注

关注

0文章

22浏览量

24674

发布评论请先 登录

相关推荐

数字下变频器的发展和更新(第一部分)

数字下变频中抽取滤波器的设计及FPGA实现

基于FPGA的数字下变频器的设计与实现

基于FGPA实现数字下变频器的抽取滤波器设计方案详解

如何在数字下变频实现FPGA

基于FPGA的数字下变频器(DDC)的设计

数字下变频器是怎么回事

下变频器输入信号幅度对下变频的影响

ADC数字下变频器:重新审视复杂的抽取示例

ADC数字下变频器:复杂抽取示例

ADC数字下变频器:复杂抽取示例

评论