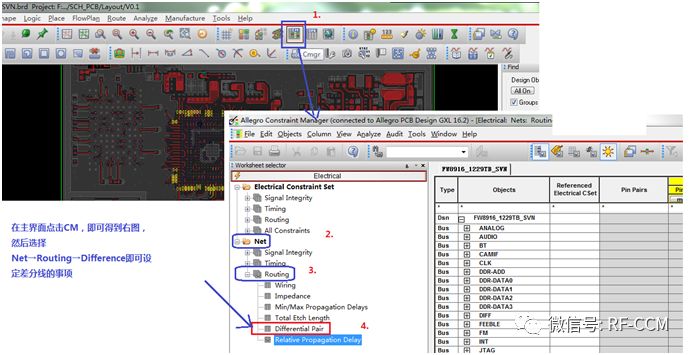

12. 如何保证差分线的长度和宽度一致?

软件自动控制,通过设定相关规则来控制走线。

13. 高速数据总线的走线需要注意什么?阻抗控制?

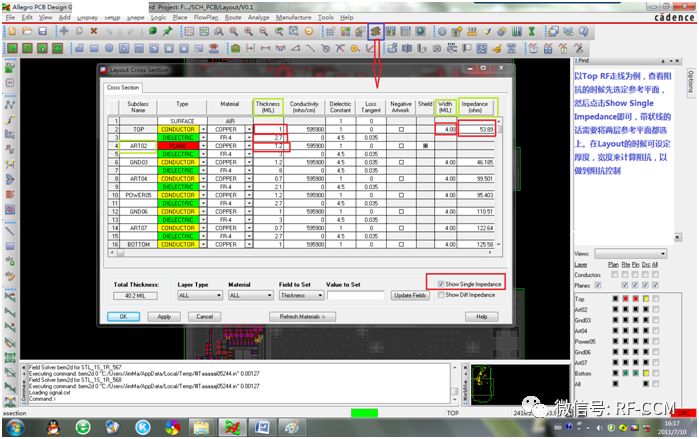

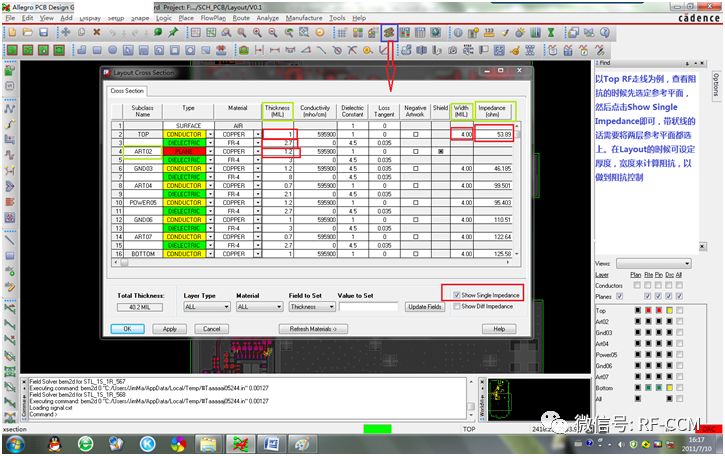

高速数据线有些需要做阻抗控制,根据层叠算出阻抗,正负10%的容差,50、90、100Ω一般都是正负10%,串扰,拉开间距,带状线的阻抗计算需要将相邻两层的pannel都计算进去,X-section计算,设定线宽和厚度

14. 电源层对上下相邻层产生什么样的影响?

若是信号走线的话,回流路径总按感抗最小的地方回流,只要是平面都可作为回流,并不是说一定要是地平面才可以,如电源平面也是回流平面。

15. 走线长度考虑

重要的 1/4 。 1/4是指PCB****的走线长度要小于这根线上信号波长的 1/4 ,因为1/4的波长的走线就是一个非常好的发射天线。

一般建议小于1/20λ 才是最佳走线长度。如 100M 频率的走线, 波长为 **3M;1/4λ=75cm ;走线长度最好不要超过 1/20*λ=15cm 。

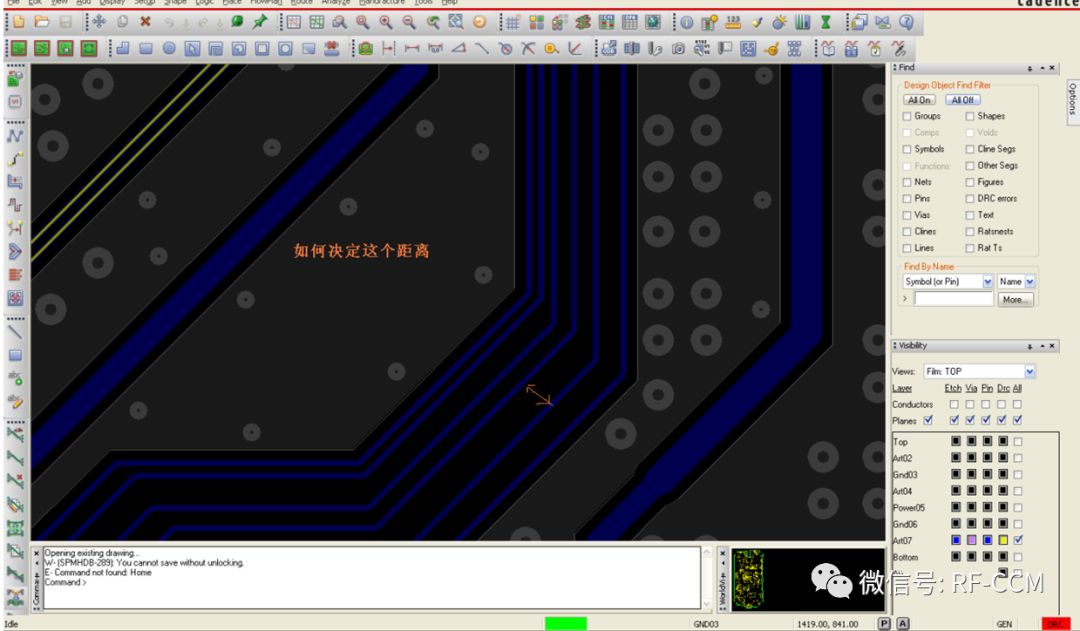

16. 如何确定下面线的间距

同类型的信号线干扰很小,可以不用考虑干扰,只需要考虑生产工艺能做到多小,如Camera的两条DataLine,只要满足生产工艺要求就可以,间距就可以离的比较近些,看具体情况处理间距。所谓要考虑串扰主要是针对不同类型信号之间的间距,同类信号只考虑生产工艺问题。而不同类信号就考虑3W原则。

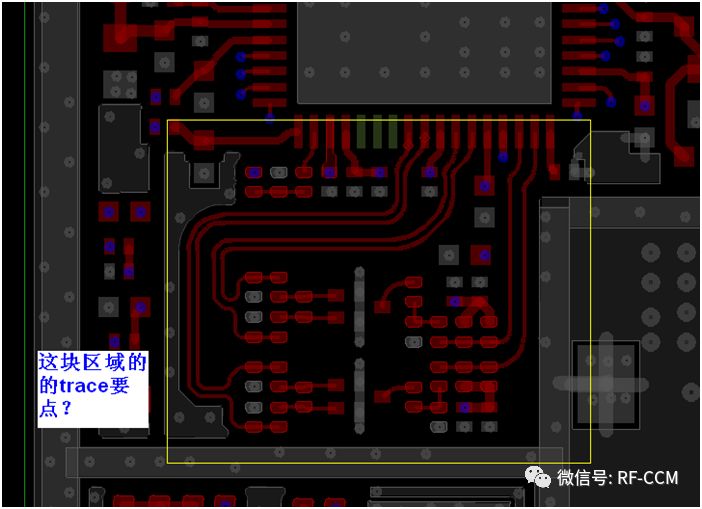

17. 下面RF区域走线主要考虑的问题是什么?

要点就是必须要控制阻抗到50Ω,这里覆铜的话因为内层有可能因为走线限制而无法打孔倒地,而导致孤立铜皮存在,孤立铜皮有可能造成天线效应,所以挖空。

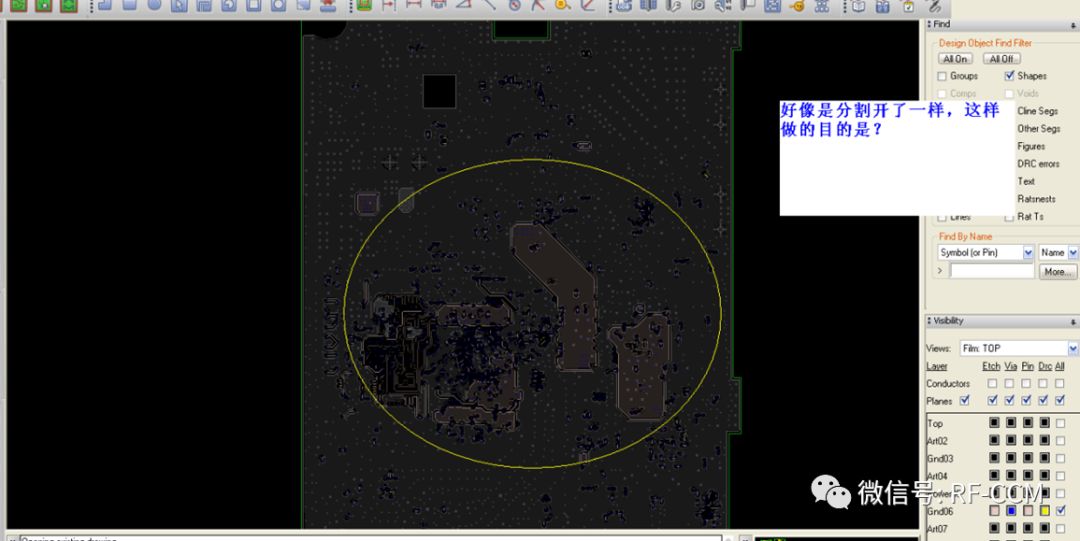

18. 下面电源部分分割的原因?

这样做肯定是不利的,但是因为这是电源走线,因其载流较大导致线宽太大而不能在别的层走线,万不得已才在地层走电源线。但是因为还有另外一层地提供完整的平面,所以此处分割没有造成大的问题。

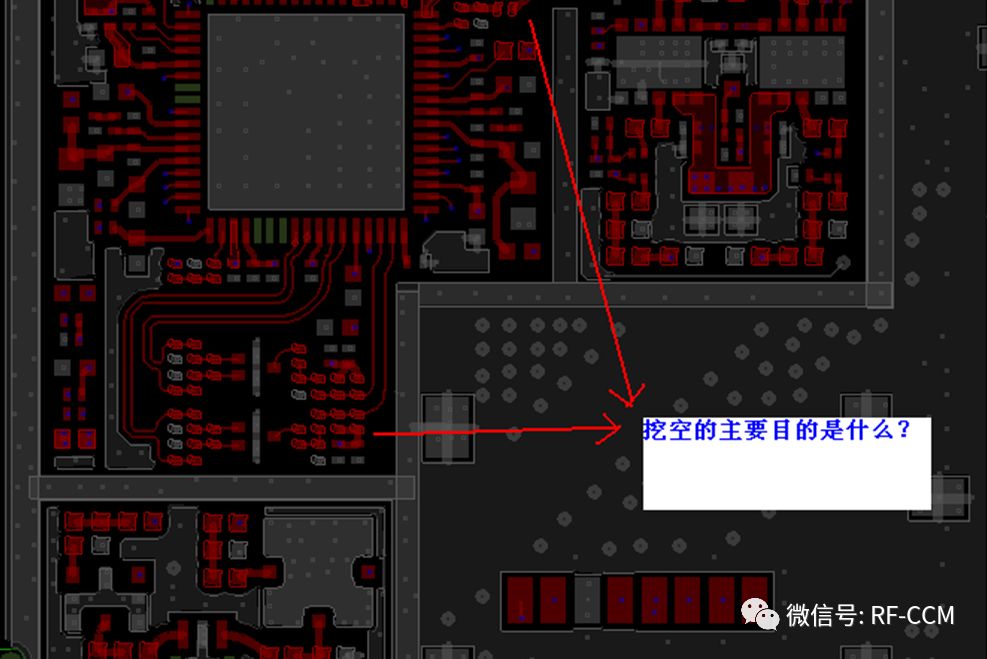

19. 如下射频部分下面挖空的主要目的是什么?

这里覆铜的话,可能因为内层有可能因为走线限制无法打孔倒地,而导致孤立铜皮存在,孤立铜皮有可能造成天线效应,所以挖空处理较好。

VTCXO在Top层挖空的主要目的是减少从PA传导过来的热量。

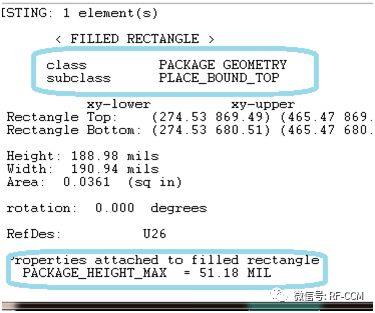

20. PCB Layout中如何查看器件的高度和坐标?

在设计之初,如何确定整个板子的厚度(PCB+器件后的,以防组装成型后太过厚重)?PCB厚度通常为多少?厚度的多少会影响什么电气性能?

高度通过下图来确认

在Find栏选择Shape

厚度主要由结构确定,我们PCB厚度通常为1mm,比方国外可以做到0.7mm,都是受限于工艺水平

21.考察一个PCB板厂的资质主要考虑它们的哪些能力?

线能走多宽,线间距,阻焊控制能力等等~

22. 如何确定走线覆铜的厚度?

根据板厂库存(备货)哪种厚度的板多,就按哪种来做,不然若板厂的库存少的话,它们需要去备料,会增加时间,交期这些。如板厂库存多的是xx盎司的板材,而我们需要xxx盎司的板材的话,就会增加备料时间,交期延迟等,所以要综合考虑,除非是板厂的材料无法满足需要,不然总按板厂库存量来设计覆铜厚度。

23.电源层电源线走线的考虑是什么?过孔多大?

考虑载流能力,根据载流能力计算过孔大小和线宽。8mil VIA,18mil的PAD通常载流能力为700mA,目前我们最大的孔为这么大,跟加工能力有关。手机通常最大的孔为8mil VIA,18mil PAD。1A走线=40mil,电流与线宽不是线性的,但还是可以以这个经验来推算一下,然后留一定余量。

24. Layout之前看器件Datasheet主要看Datasheet的哪些参数?

主要看引脚信号属于什么类型,以便于确定走线时候需要注意的事项。

25. 如何方便走线就如何放置元件的方向?

Yes

26. BGA里面打孔方式,结合SMT,那种方式比较好?

打孔的话应该打在PAD的正中间,之前的板子因为VIA稍微有点偏移,SMT反映较难贴片**。**

27. PCB表面处理技术及优劣,实际环境下对PCB的影响?

不同的情况适用于不同的场合,如有铅和pb-free等,根据产品要求来定义,我们手机板常做沉金和OSP的处理,沉金抗氧化能力好,OSP暴露在空气中的话抗氧化能力不如沉金,所以按需求用沉金和OSP处理。

28. 常说的通孔板是什么意思?手机设计成通孔板的原因是什么?

从TOP一直打穿到BOTTOM,优点就是便宜,功能性的手机可用通孔板做,但是Smartphone由于信号要求,不能做通孔板。手机通孔板主要就是因为低端机要求不高,便宜。

29. 有些接地过孔是从Top-Bottom的,这样做的目的是什么?

便宜,且可以将所有的地一次性连接起来**。**

**30. die **

(plural dies or dice) A square of silicon thatcontains an integrated circuit. Die often is used synonymously with chip. die就是ic 未封装前的晶粒 , 是从硅晶片 (wafer) 上用激光切割下 , 把****die 焊在框架上 , 再在die上面焊接上金线后形成****ic 裸芯片 , 再拿去塑封 . 将半导体大圆片 (Wafer) 分割而成的小片 (Die) 。它可有一个或多个电路 , 但作为一个单位封装而成DIE是个单词,它的原本意义有模的意思,引申为管芯,模片的意思。

31. Layout时候的封装如何和SCH结合起来?

先做好封装后再在SCH中填写****footprint

32. 检查封装的时候都是检查一些什么东西?

根据Datasheet对比****尺寸

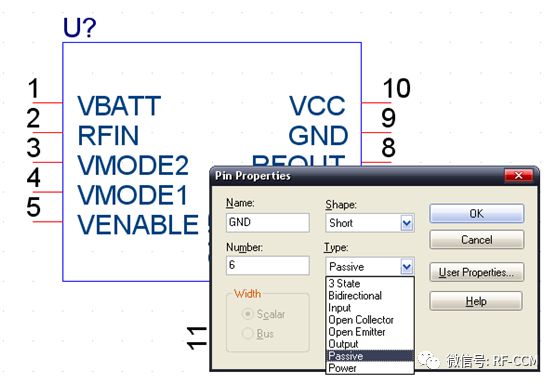

33. 在原理图库中做元件封装时定义引脚都为Passive的缺点是什么?

是否有必要将所有的引脚都规定为如下示中的几个形式?

为了省事,通常用****Passive

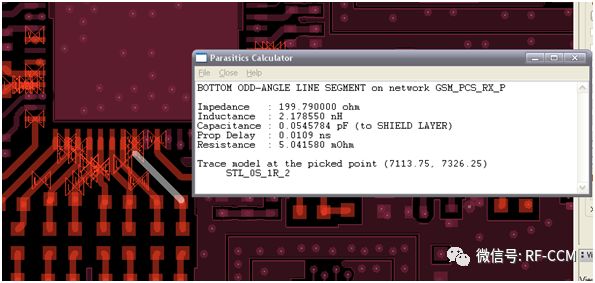

34. 如下参数如何理解?

特征阻抗,感抗,容抗,延迟,自由阻抗。

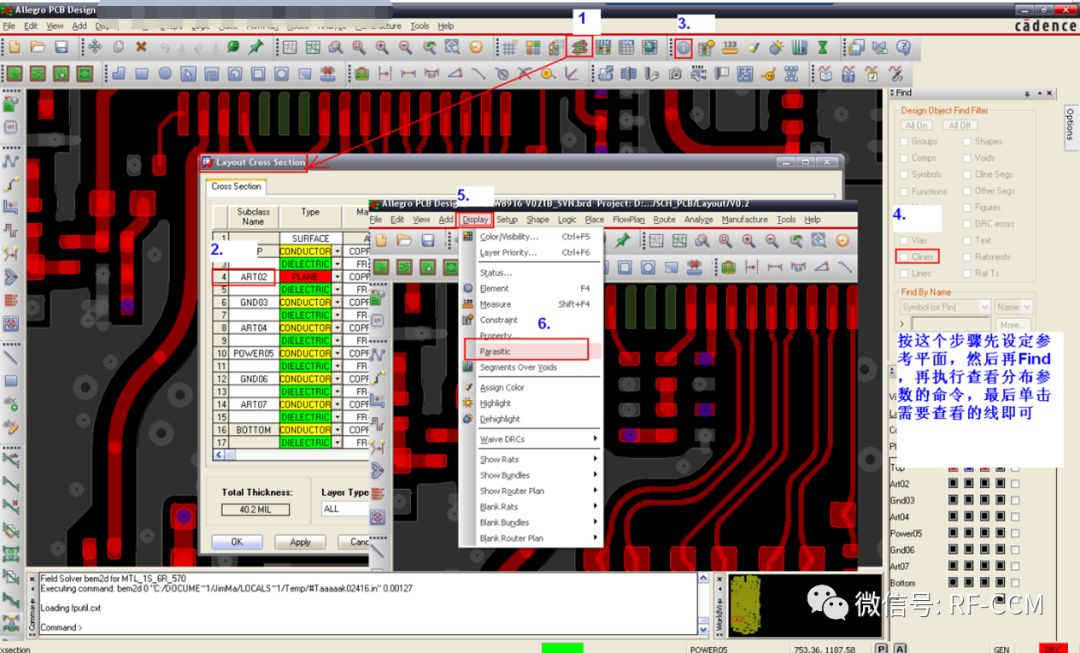

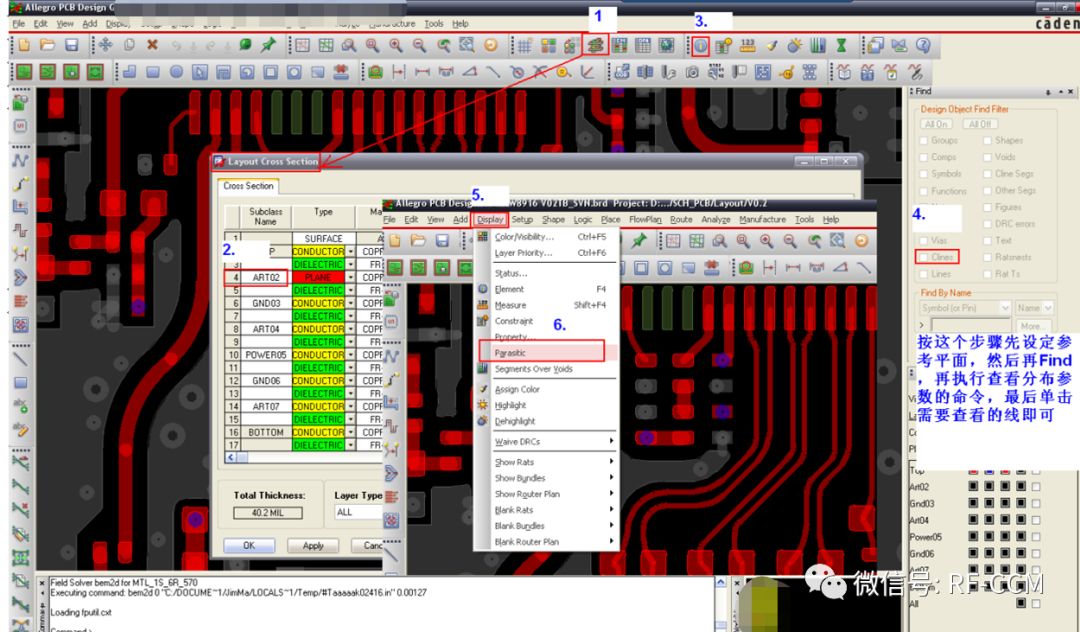

要正确查看阻抗的话,遵守下图步骤。

35. 能否查看某网络的单独的阻抗是多少?

和分布参数查看一样

36. PolarPA的过孔?

主要是考虑载流能力和余量,8mil VIA,18mil的PAD通常载流能力为700mA,目前我们最大的孔为这么大,跟加工能力有关,手机通常最大的孔为8mil VIA,18mil PAD。

37. 如下PA Power Line走线重叠的原因

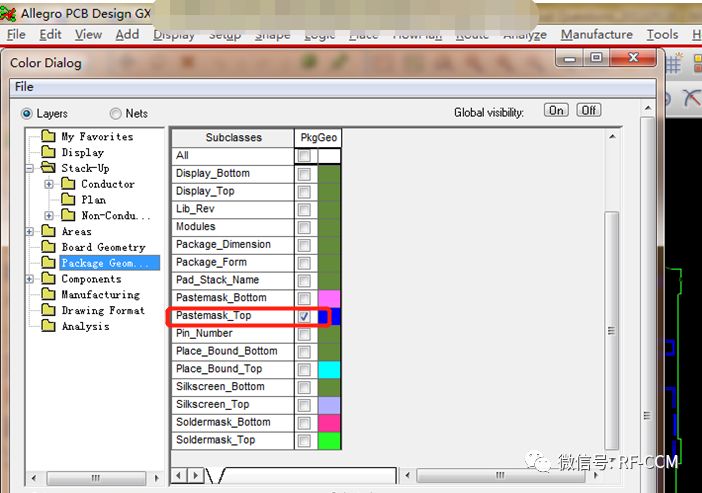

38. 如何查看屏蔽框?

通常为这层

39. 如何查看射频走线的阻抗,如何根据层叠来计算和控制阻抗?

CM图标定义差分阻抗等,在查看阻抗之前一定要先设定参考平面,不然用分布参数查看功能得出的结果会有问题。

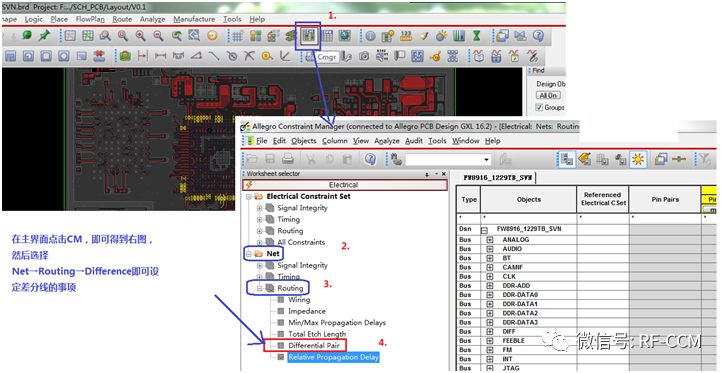

40. 差分走线规则设定(根据需要手动设定)

41.通孔板

通孔板是没有埋、盲孔的,即所有过孔都是从Top到Bottom贯通的。

42. Datasheet参考

很重要的一点是详细参阅相关Datasheet及HW Training文档和User Guide来 Layout 。 务必按这些要求来进行相关 Layout 。

-

PCB设计

+关注

关注

394文章

4702浏览量

86577 -

Layout

+关注

关注

14文章

408浏览量

62041 -

电源线

+关注

关注

1文章

374浏览量

21974 -

SCH

+关注

关注

1文章

45浏览量

26620 -

差分线

+关注

关注

0文章

37浏览量

8962

发布评论请先 登录

相关推荐

请问如何保证多片AD1278的通道之间相位一致性?

PADS PCB功能使用技巧系列 —— 如何走差分线?

请问差分线布线每对等长需要的长度差限制范围是多少?

高频差分线布线的长度匹配方式

差分线传输线长度差有关的问题

OCP互连一致方案应用

工程师头疼的差分线传输线长度差问题资料下载

如何保证差分线的长度和宽度一致?

如何保证差分线的长度和宽度一致?

评论