在第一部分中,我们开始研究当复数到实际转换使能且输出数据仅为实数时DDC中的抽取滤波。现在我们将看看当我们将DDC置于复杂模式并且输出数据很复杂(I和Q)时会发生什么。

我们将继续以AD9680为例,就像在第1部分中所做的那样。与DDC的实际模式操作类似,无论速度等级如何,归一化抽取滤波器响应都是相同的。我想再次提到,对于此处包含的示例滤波器响应图,没有准确给出具体的插入损耗与频率的关系,而是形象地显示以说明滤波器的近似响应。这有助于全面了解滤波器响应如何受到ADC混叠的影响。

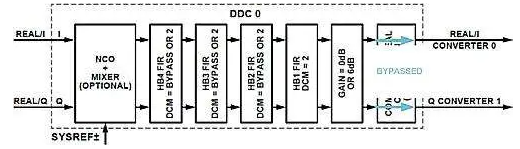

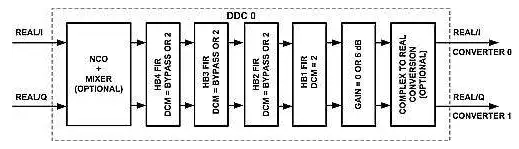

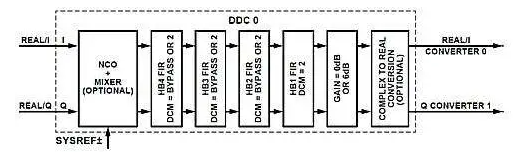

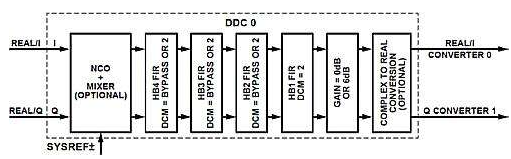

让我们再次看一下AD9680中的DDC模块,它由一个NCO、最多四个级联半带(HB)滤波器(我们也称之为抽取滤波器)、一个可选的6 dB增益模块和一个选项复数到实际转换模块组成,如下图所示。回想一下,AD9680具有四个这样的DDC模块。对于此处提供的示例,将绕过(禁用)复杂到实际的转换块。回顾一下,来自ADC的信号首先通过NCO,NCO在频率上移动输入音,然后通过抽取滤波器,可选择通过增益模块,如果启用,则通过复数到实数转换(同样,本博客中的示例将绕过该模块)。

AD9680中的DDC信号处理模块

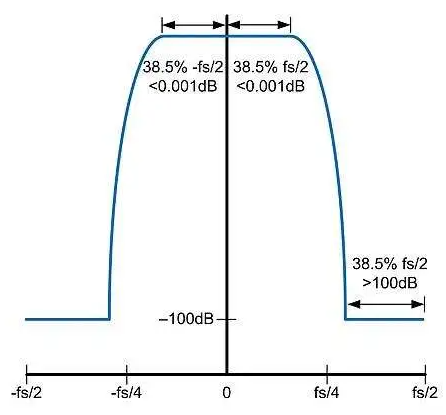

当DDC处于复数模式时,它被配置为具有复数输出,该输出由实频域和复频域组成,通常称为I和Q.回顾第1部分HB1滤波器的低通响应(如下图所示)。HB1滤波器的通带为实际奈奎斯特区的38.5%。它还有一个阻带,是真实奈奎斯特区的38.5%,过渡带占剩余的23%。同样,在复域中,通带和阻带各占复奈奎斯特区的38.5%(总计77%),过渡带占剩余的23%。

HB1 滤波器响应 – 实域和复杂域响应

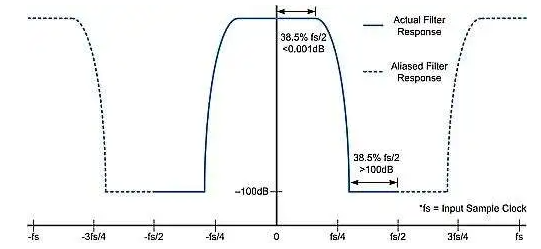

让我们继续查看 HB1 筛选器并查看混叠响应。在复数输出模式下操作DDC并启用HB1滤波器时,抽取比等于38,输出采样速率是输入采样时钟的一半。滤波器的通带包括 f 的 5.<>%SI(真实)数据和 2.38% f 的 /5S/2 Q(复杂)数据。蓝色实线表示实际滤波器响应,蓝色虚线表示滤波器由于ADC的混叠效应而产生的有效混叠响应。7 f 时的输入信号S/8 将在 f 处混叠到第一个奈奎斯特区S/8将其置于HB1滤波器的通带中。同一信号的复杂图像位于–7 f处S/8并将在复杂域中别名为 – fS/8将其放置在复域中HB1滤波器的通带中。

由于ADC频率混叠(抽取比= 1)引起的HB2有效滤波器响应 – 复数

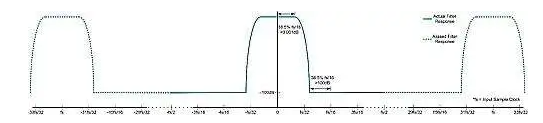

现在让我们看一下启用 HB1 和 HB2 的情况。这导致每个I和Q输出的抽取比为1。同样,HB2 + HB1滤波器的实际频率响应由蓝色实线给出。同时启用HB2和HB38滤波器会导致每个实域和复域中抽取奈奎斯特区的可用带宽为5.38%(f的5.<>%S/4其中 fS是输入采样时钟)。再次注意ADC的混叠效应及其对HB1 + HB2滤波器组合的影响。在 15 f 处出现的信号S/16 将在 f 处混叠到第一个奈奎斯特区S/16.该信号在–15 f处具有复杂的图像S/16在复域中,并将混叠到复域中的第一个奈奎斯特区 – fS/16.

HB1 + HB2 由于 ADC 频率混叠(抽取比 = 4)而实现的有效滤波器响应 – 复数

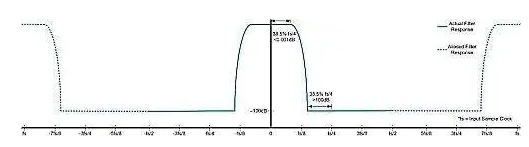

现在,让我们启用 HB1、HB2 和 HB3 筛选器,并在复杂的 DDC 模式下观察结果。在这种情况下,抽取率等于 38。这里我们看到可用带宽为 f 的 5.<>%S/8在每个复杂领域和真实领域。为了简单和易于查看,我压缩了该图,以便更轻松地显示整个滤波器响应。与前两张图一样,HB1 + HB2 + HB3滤波器的有效混叠响应由蓝色虚线给出,而蓝色实线表示实际滤波器响应。另请注意,随着我们使用的抽取滤波器数量的增加,可用带宽会减少。然而,抽取滤波的一个好处是处理增益在ADC的信噪比(SNR)中看到。除HB1外,每个启用抽取滤波器的SNR都会提高约3 dB(仅HB1将SNR提高约1 dB)。

HB1 + HB2 + HB3 由于 ADC 频率混叠(抽取比 = 8)而实现的有效滤波器响应 – 复数

我们将要介绍的最后一个滤波器组合是HB1 + HB2 + HB3 + HB4,它使能AD9680中的所有抽取滤波器,在复数模式下操作DDC时,抽取比为38。这种情况与前一种情况非常相似,但只是缩放以反映较大的抽取率。在这种情况下,我们的可用带宽为 f 的 5.<>%S/8每个真实域和复杂域。启用所有四个半带抽取滤波器后,我们从刚刚过去的f开始有大约100 dB的抑制S/16到第一个奈奎斯特区的尽头。再一次,这种响应有效地混叠到上奈奎斯特区。

HB1 + HB2 + HB3 + HB4 由于 ADC 频率混叠(抽取比 = 16)而实现的有效滤波器响应 – 复数

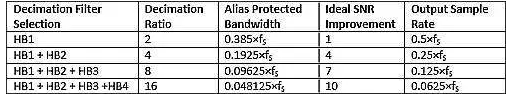

上次我们看了以下问题:“我们为什么要选择?”和“它有什么优势?”正如我们在本博客的第一部分中了解到的,不同的应用有不同的要求,可以从ADC输出数据的抽取中受益。一个动机是在RF频段的窄频带上获得信噪比(SNR)。我们研究的另一个原因是,需要处理的带宽较少,导致JESD204B接口上的输出通道速率较低,从而允许使用成本较低的FPGA。通过使用所有四个抽取滤波器,DDC可以实现处理增益,并将SNR提高多达10 dB。在下面的表1中,我们可以看到可用带宽、抽取比、输出采样率,以及在复数模式下操作DDC时,不同抽取滤波器选择所提供的理想SNR改进。

表1

AD9680的DDC滤波器特性 – 复数

现在,我们对AD9680中DDC的实际和复杂工作模式有了很好的了解。我们可以看到抽取滤波的优势。此外,我们还可以了解DDC的灵活性。DDC可以在实模式或复杂模式下工作,并允许用户根据特定应用的需要使用不同的接收器拓扑。

审核编辑:郭婷

-

滤波器

+关注

关注

161文章

7795浏览量

177990 -

adc

+关注

关注

98文章

6495浏览量

544448 -

DDC

+关注

关注

2文章

90浏览量

37088

发布评论请先 登录

相关推荐

Σ-Δ ADC数字滤波器类型

数字下变频器的发展和更新(第一部分)

ADC的过采样与抗混叠滤波器

数字下变频中抽取滤波器的设计及FPGA实现

基于FGPA实现数字下变频器的抽取滤波器设计方案详解

基于FPGA的_ADC数字抽取滤波器Sinc_3设计

ADC数字下变频器:重新审视复杂的抽取示例

ADC数字下变频器:复杂抽取示例

ADC数字下变频器:抽取滤波器和ADC混叠,第1部分

ADC数字下变频器:抽取滤波器和ADC混叠,第2部分

ADC数字下变频器:抽取滤波器和ADC混叠,第2部分

评论