基本知识

锁相环:在通信领域中,锁相环是一种利用反馈控制原理实现的频率及相位同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,输出稳定的频率信号。

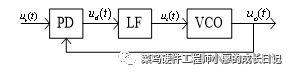

锁相环的设计原理:锁相环(PLL)是一个相位跟踪系统。最基本的锁相电路框图如下所示:

主要包括鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)。在作为频率综合器使用时,在输出信号和输入信号之间还应插入一个数字分频器,鉴相器是相位比较器,它把输出信号和参考信号的相位进行比较;环路滤波器的作用是滤除误差电压中的高频成分和噪声,以保证环路所要求的性能,提高系统的稳定性。压控振荡器受控制电压的控制,使压控振荡器的频率向参考信号的频率靠近,于是两者频率只差越来越小,直至频差消除而被锁定。

因此,锁相环的工作原理可以简述如下。鉴相器把输入信号和参考信号的相位进行比较,产生一个反映两信号的相位差大小的误差电压,经过环路滤波器的过滤得到的控制电压。调整VCO的频率向参考信号的频率靠拢,直至最后两者频率相等而相位同步,实现锁定后两信号之间的相位差表现为一个固定的稳定值。

由此可见,通过锁相环路的相位跟踪作用,最终可以实现输出信号与参考信号同步,两者之间不存在频差而只存在很小稳态相差。

为了建立锁相环路的数学模型,首先建立鉴相器、环路滤波器、压控振荡器的数学模型。

(1)、鉴相器

鉴相器(PD)又称相位比较器,它是用来比较两个输出信号之间的相位差。

鉴相器按其鉴相特性分为正弦型、三角形和锯齿波形。作为原理分析,通常使用正弦型,较为典型的正弦鉴相器可用模拟乘法器和低通滤波器的串接构成。

(2)环路滤波器

环路滤波器(LF)是一个线性低通滤波器,用来滤除误差电压中的高频分量和噪声,更重要的是它对环路参数调整起到决定性的作用。环路滤波器由线性元件电阻、电容和运算放大器组成,它是一个线性系统。常用的环路滤波器有RC积分滤波器、无源比例积分滤波器和有源积分滤波器三种。有源比例积分滤波器由运算放大器组成。

(3)压控振荡器

压控振荡器(VCO)是一个电压-频率变换器,在环路中作为被控振荡器,它的振荡频率应随输入控制电压的线性变化。VCO在锁相环中起了一次积分作用,因此也称为环路中的固有积分环节。

(4)环路相位模型和基本方程

上面分别得到了鉴相器、环路滤波器和压控振荡器的模型,将三个模型连接起来,就得到了锁相环路的模型。

在实际应用中,锁相环通常是以锁相环频率合成器的电路出现,该电路与基本锁相环电路的区别是在反馈回路中加入一个数字分频器,为了方便说明,统一称锁相环频率合成器为锁相环电路。

锁相环性能参数:(1)、频率准确度:实际输出频率与标称输出频率之差,一般由分频数N与参考源fref决定;(2)、频率稳定度:在一定时间间隔内,频率的相对变化程度(f-f0)/f0,单位一般为ppm(10-6)或ppb(10-9),该指标一般由参考源fref决定;(3)、相邻两个输出频率的最小间隔,对于整数分频,其频率精度等于fref;对于小数分频,其频率精度可为任意小;(4)、频率范围:锁相环系统输出频率的范围,该指标由VCO频率范围和锁相环芯片内的分频器共同决定;(5)、换频时间:锁相环系统输出信号从一个频率切换到另一个频率时,其输出从突变到重新进入稳定状态所用的时间,该指标由系统阻尼系数和环路带宽决定;(6)、频谱纯度:该指标由输出信号的相位噪声和杂散来衡量,带内相位噪声主要由参考源、鉴相器和电荷泵决定,带外相位噪声主要由VCO决定。

锁相环原理图设计与仿真目标

在ADS中集成了一个锁相环辅助设计工具,利用该工具,生成所要设计锁相环的整体电路,并对其进行仿真确定各电路的性能指标。

VCO输出频率:900MHz±10MHz。

VCO压控增益:12MHz/V。

VCO相位噪声:小于-100dBc/Hz@100kHz。

参考源频率:10MHz

系统频率间隔:200kHz。

环路滤波器环路带宽:Wc=10kHz。

相位裕度:45度~50度

锁定时间:小于200us

实现步骤

锁相环环路滤波器设计

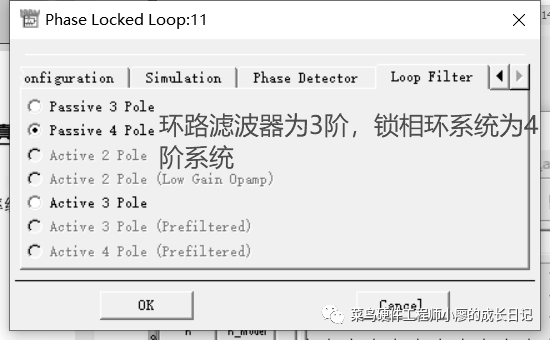

环路滤波器决定了锁相环环路电路中频谱纯度、锁定时间以及系统稳定性等指标。

设计步骤

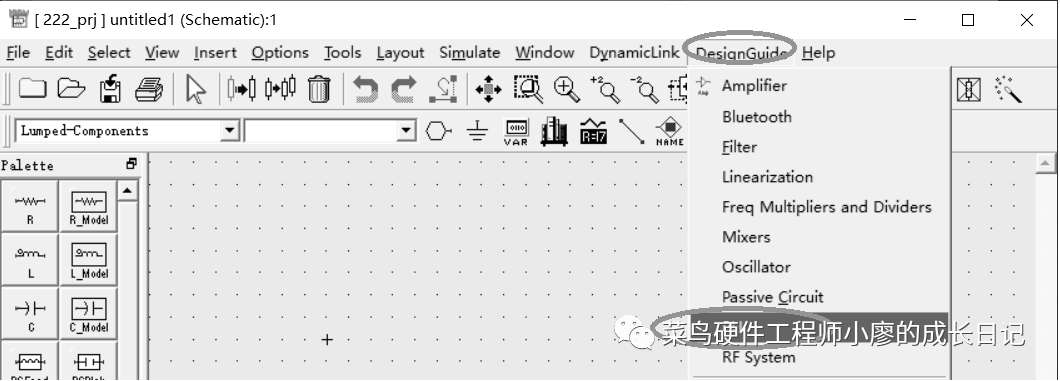

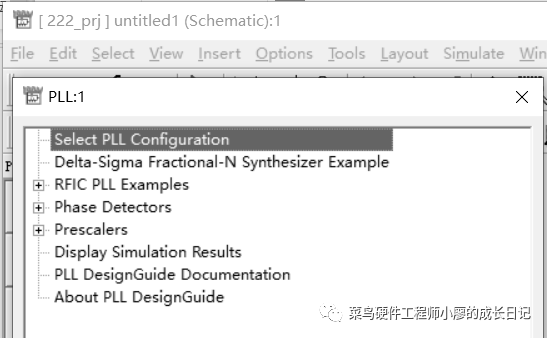

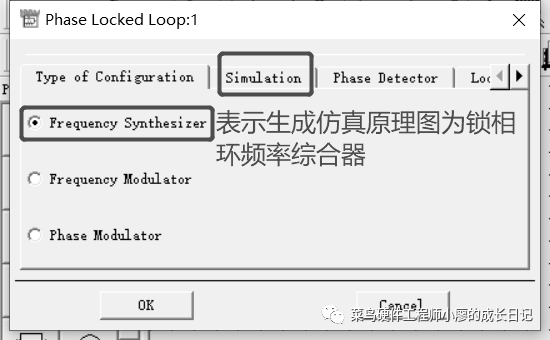

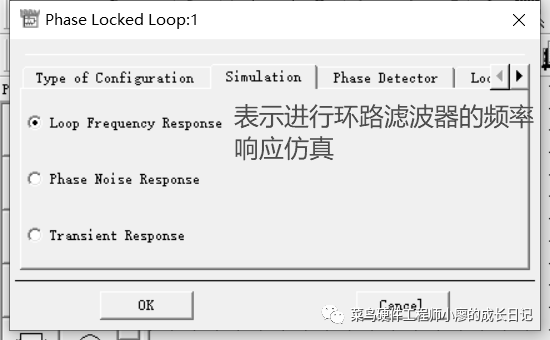

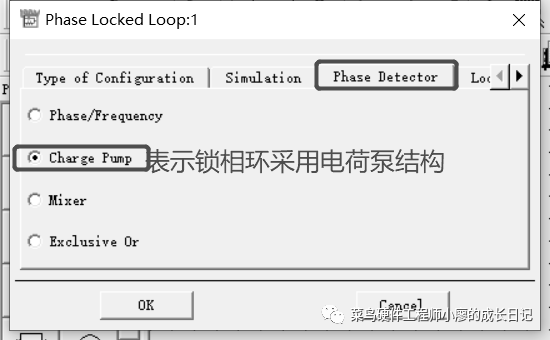

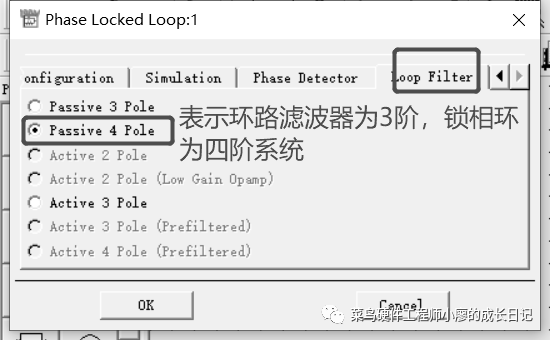

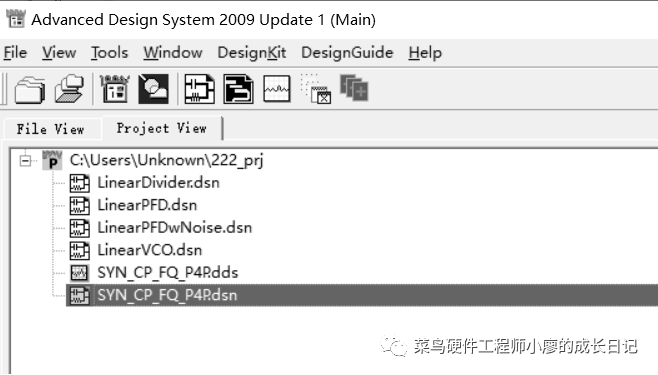

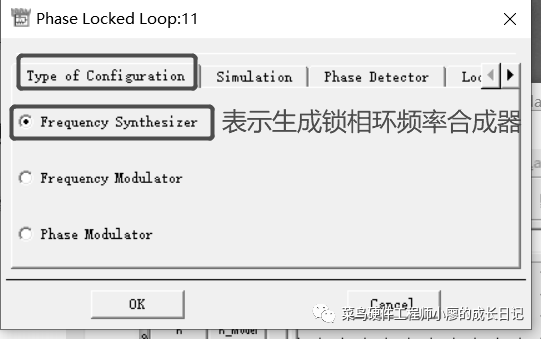

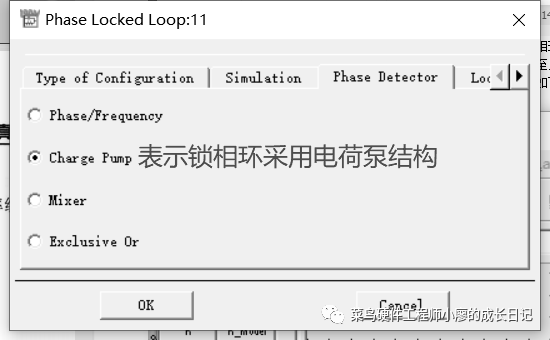

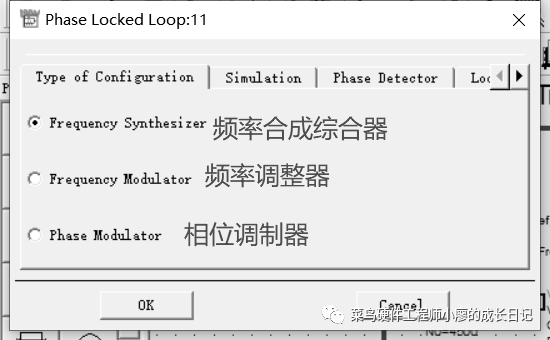

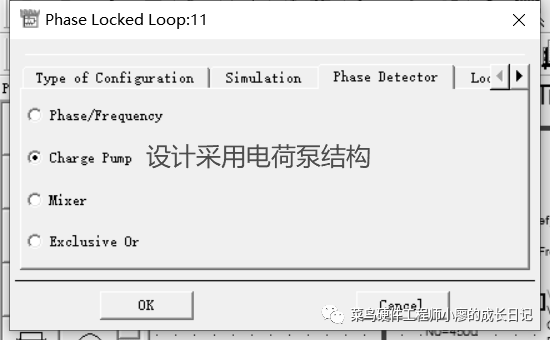

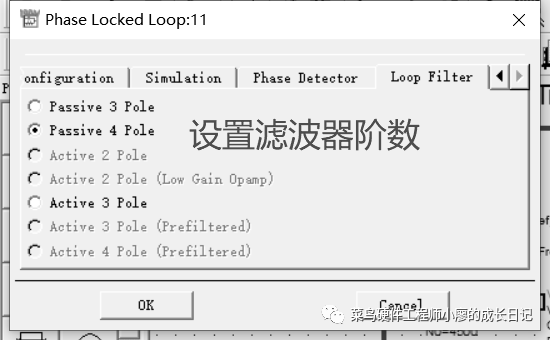

1、运行ADS新建“pll_lab”的工程,并建立“pll”的原理图。在菜单栏中选择【DesignGuide]->[PLL]命令,选择“Select PLL Configuration”单机[OK]。

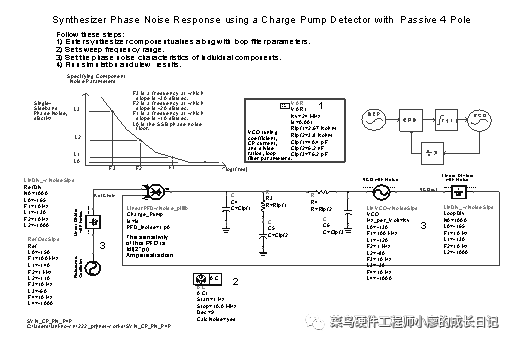

这样设置完成后,生成原理图:

生成的原理图分为了五个部分,1、用于仿真系统闭环特性。2、变量设置区,用于设置环路各个参数。3、用于仿真系统开环特性;4、用于仿真环路滤波器频率响应。5、仿真所需的仿真器、优化器、优化目标及公式编辑器

由于电路中鉴相增益、滤波器器件值、VCO压控增益和分频值等各模块的参数都被设置成变量,在设计中主要对这些变量进行参数设置。

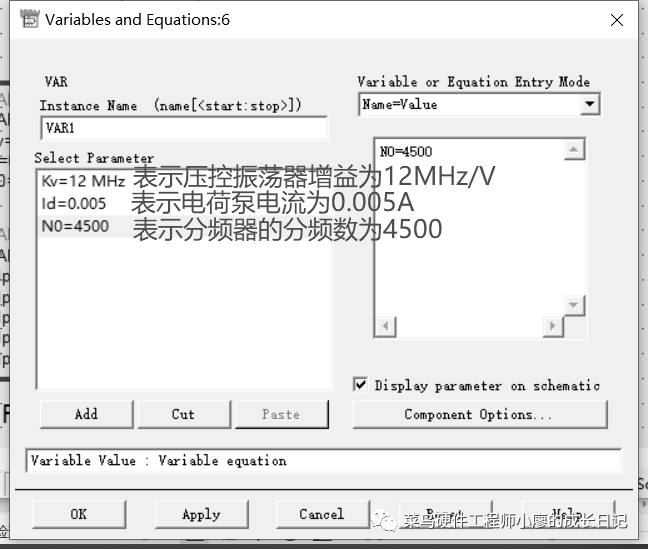

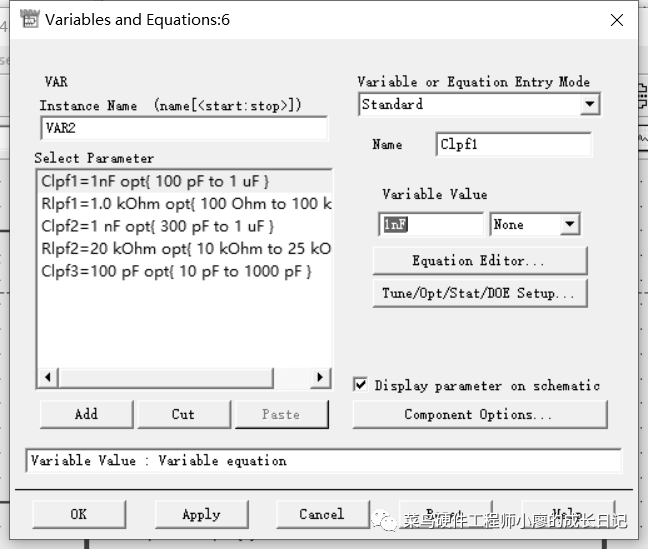

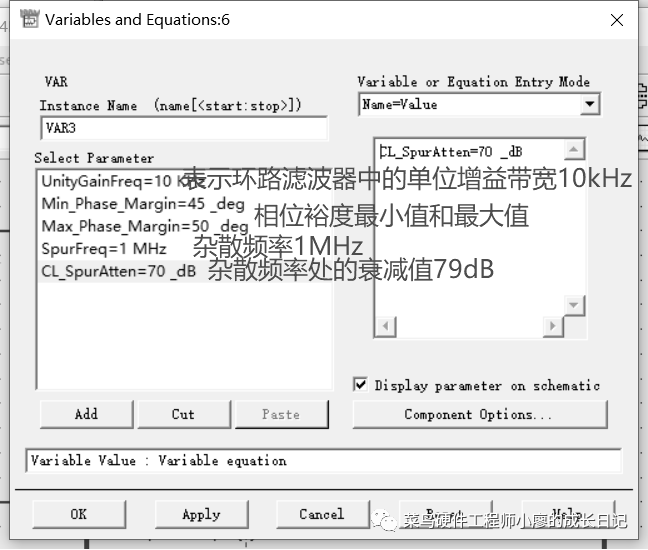

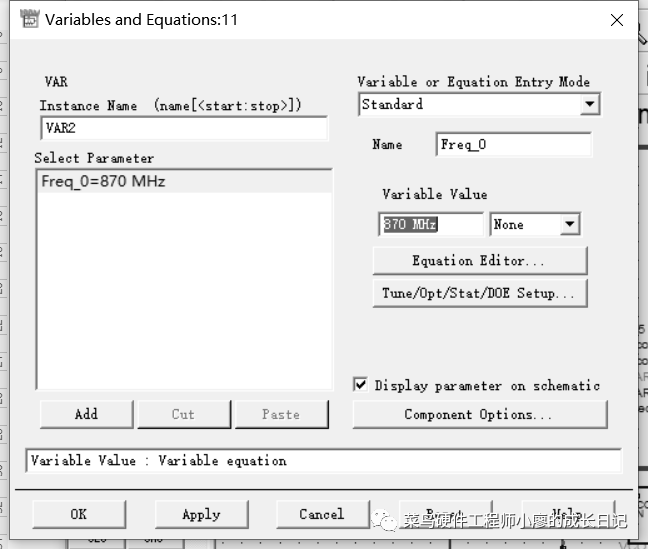

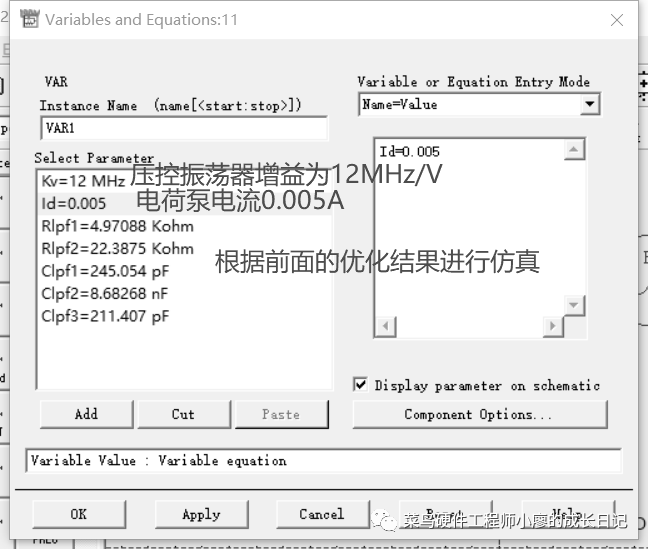

2、双击变量控制器VAR1,VAR2、VAR3进行设置。

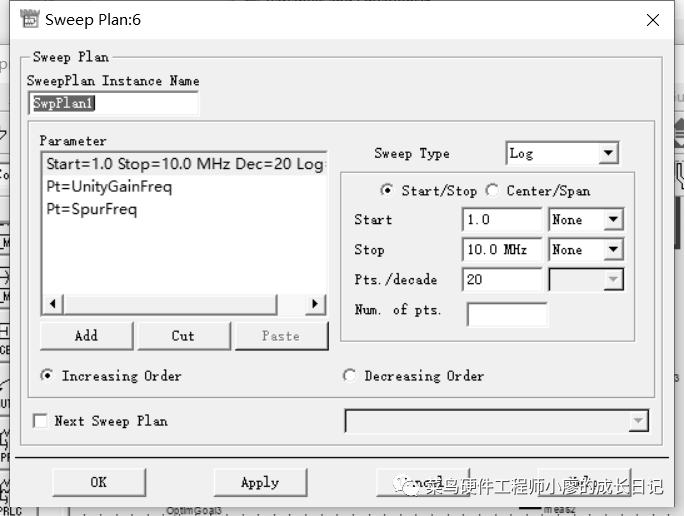

3、设置扫描计划控制器,默认设置

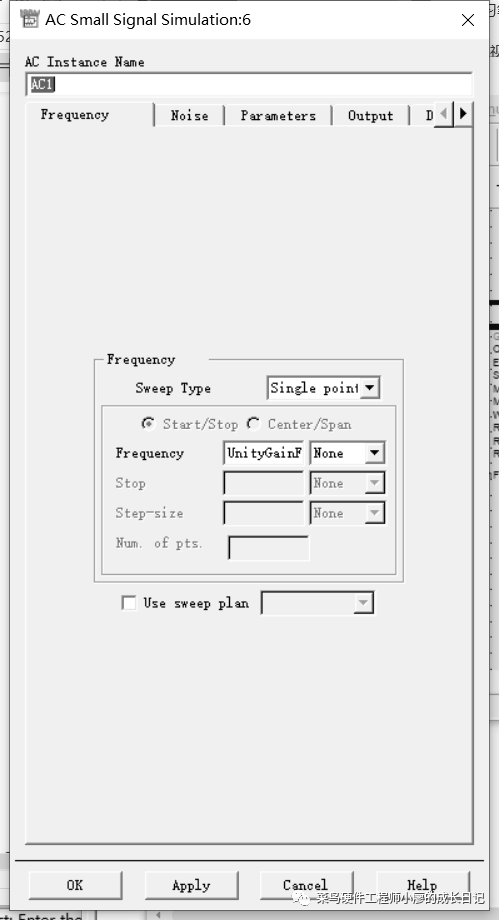

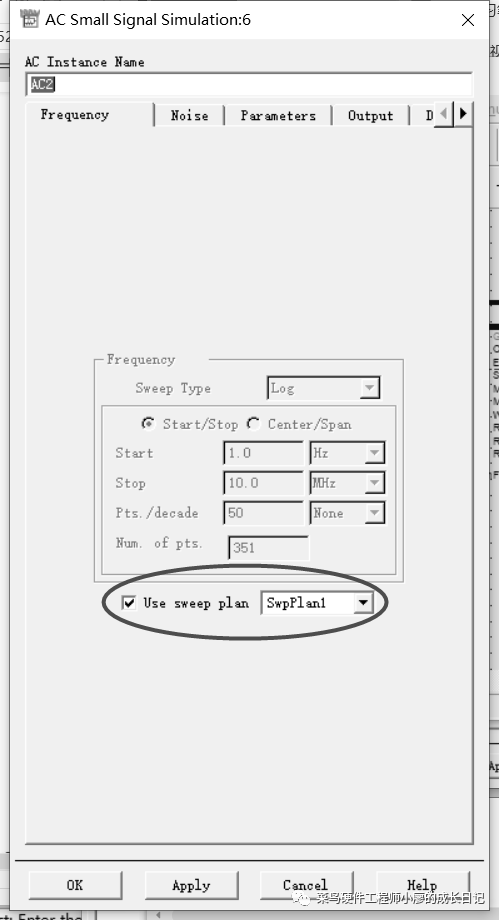

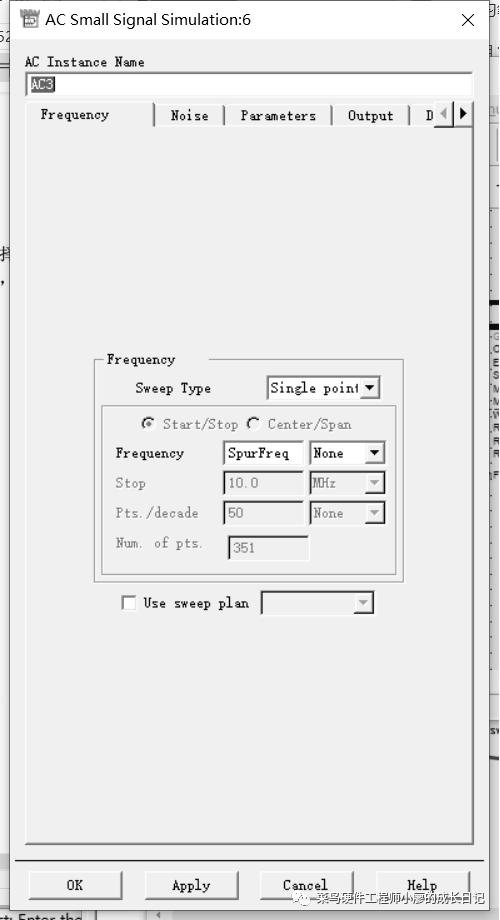

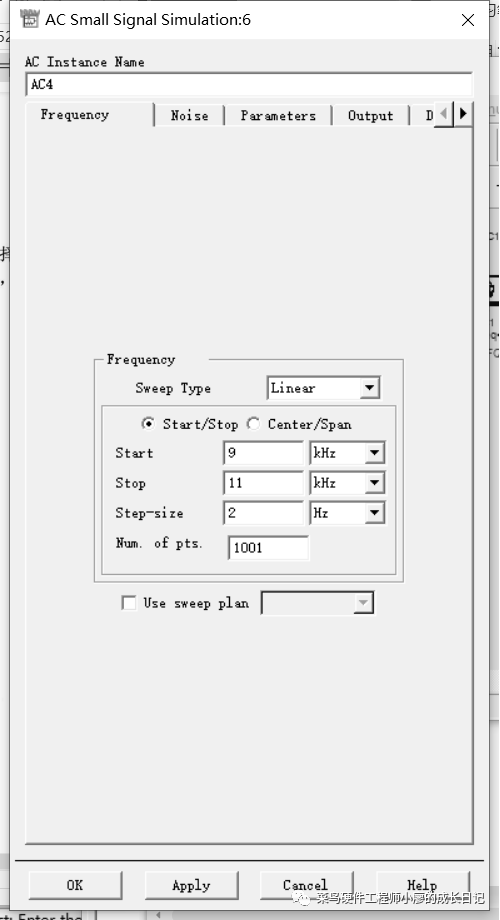

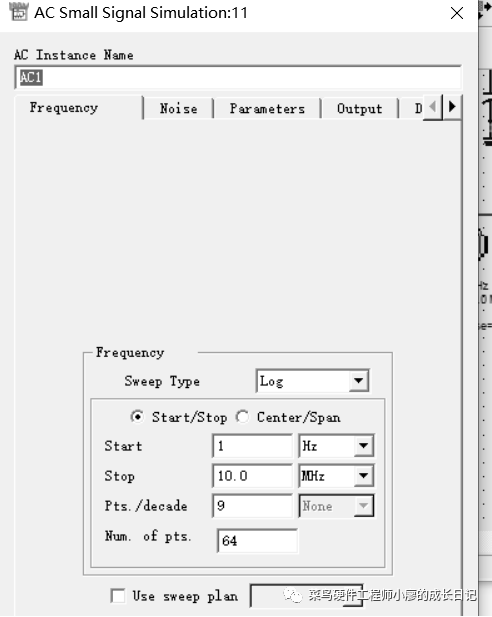

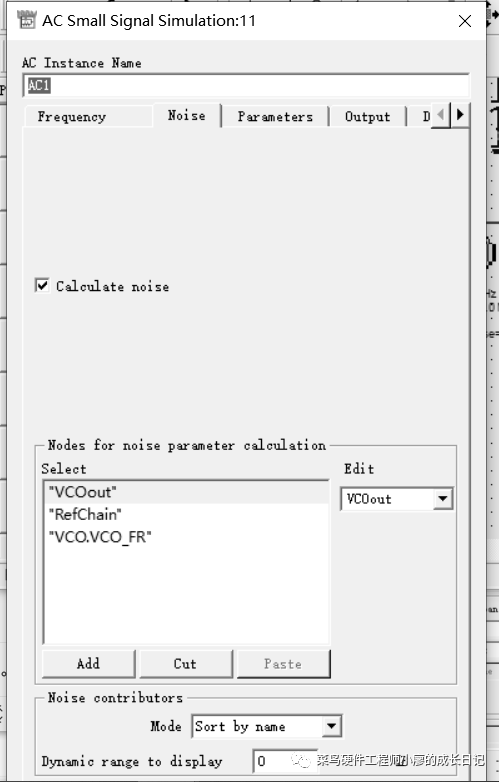

4、设置交流仿真控制器,AC1、AC2、AC3和AC4

同时添加一个AC4

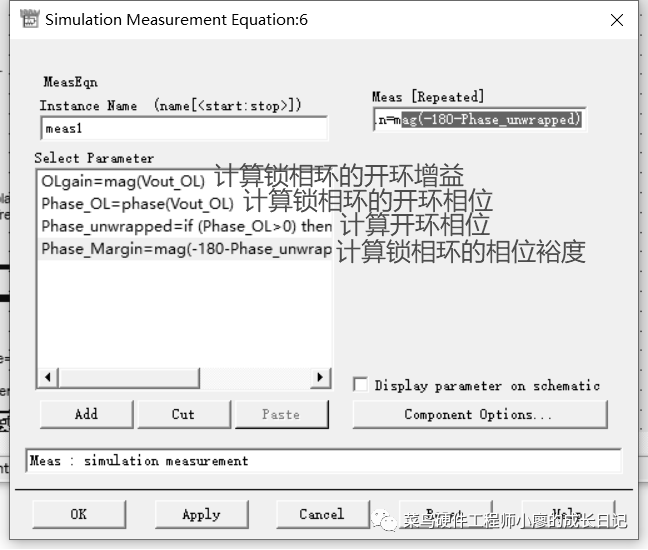

5、设置测量公式控制器,直接保持默认值。

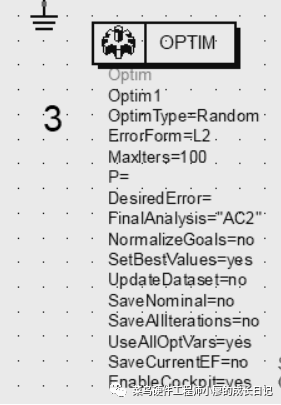

6、设置优化控制器。

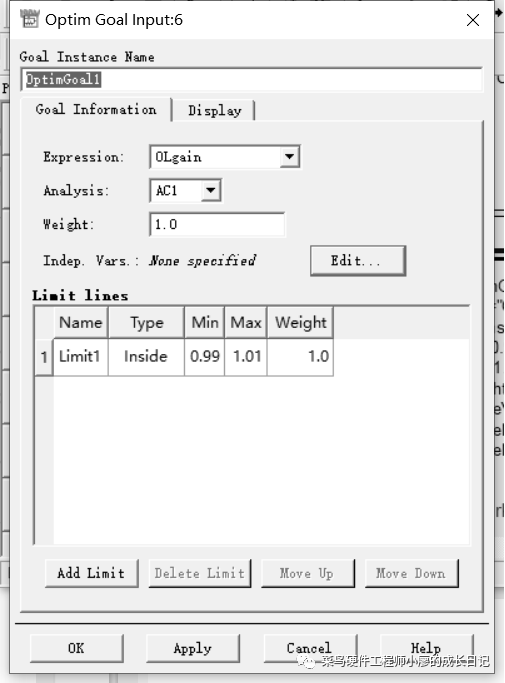

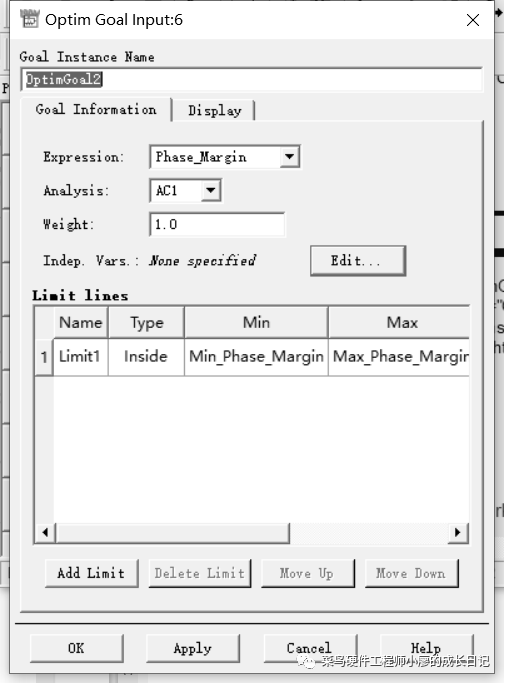

7、设置优化目标,也是保持默认。

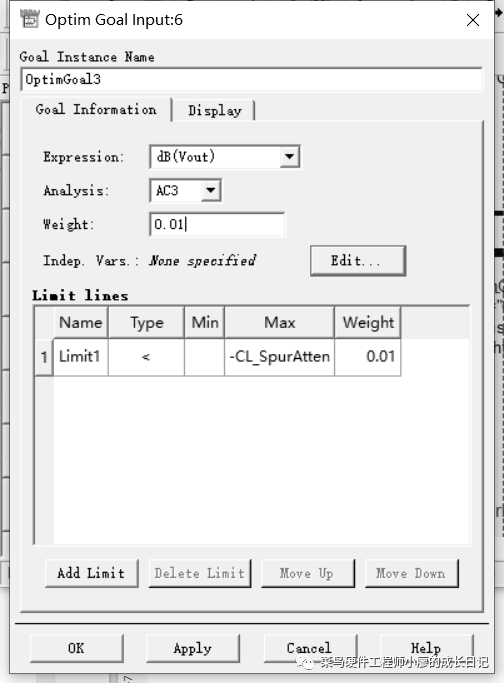

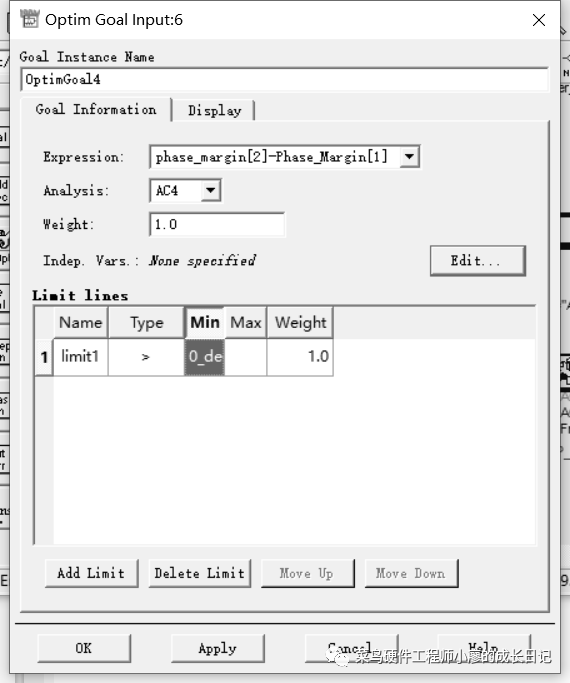

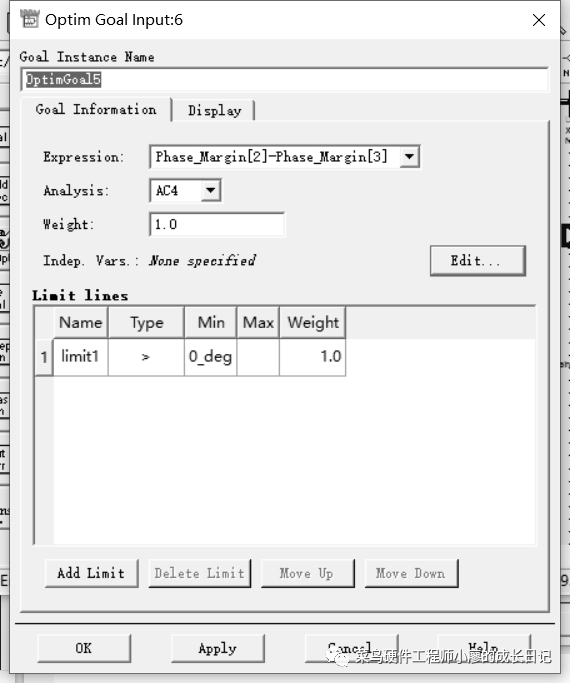

除了以上三个优化目标控制器,为了保证在环路滤波器单位增益带宽在10kHz处的相位裕度达到最大,还需要添加2个优化目标控制器。Goal4个Goal5

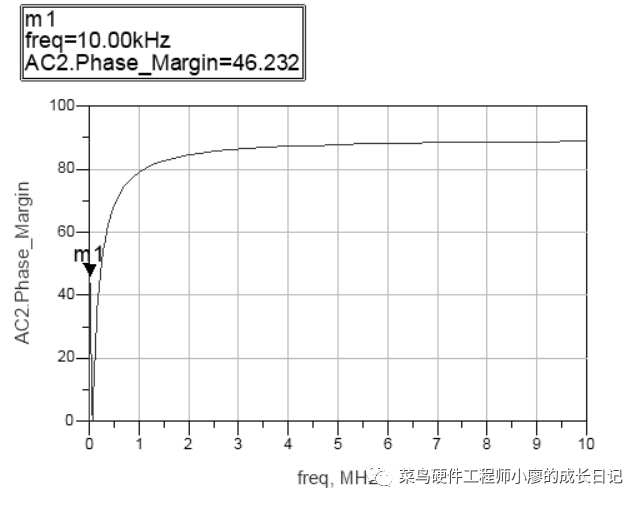

8、对电路进行优化仿真,X显示AC2.Phase_Margain,得到环路相位裕度,在单位增益带宽10kHz时相位裕度达到46.232度,满足45~50度之间的优化要求。

锁相环锁定时间仿真

锁相环锁定时间觉得了锁相环对快速变化频率的信号响应速度,依据不同的系统有不同的设计要求,一般在几十微秒至几百微妙之间。

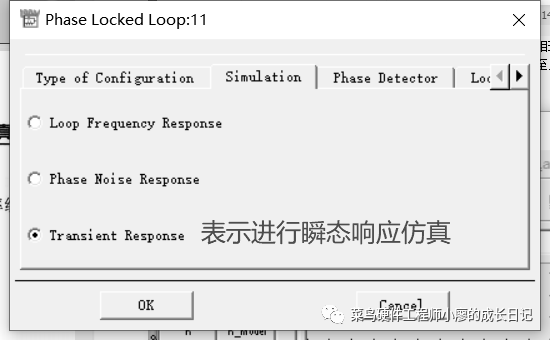

1、同样利用向导完成,设置如下:

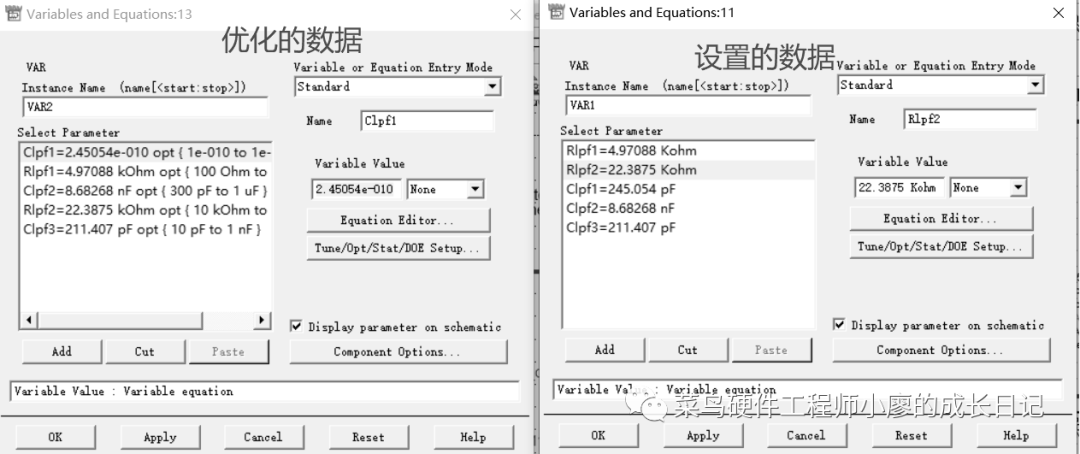

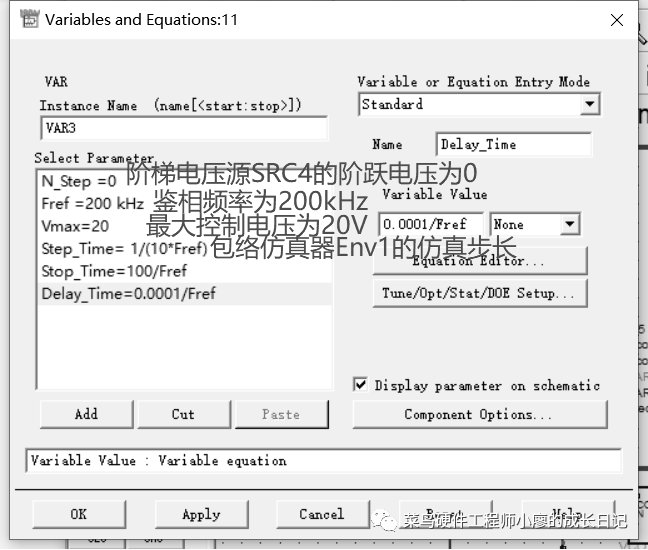

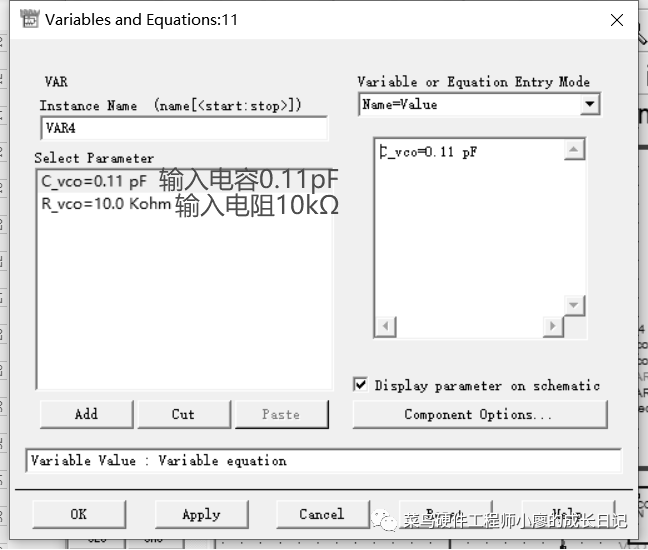

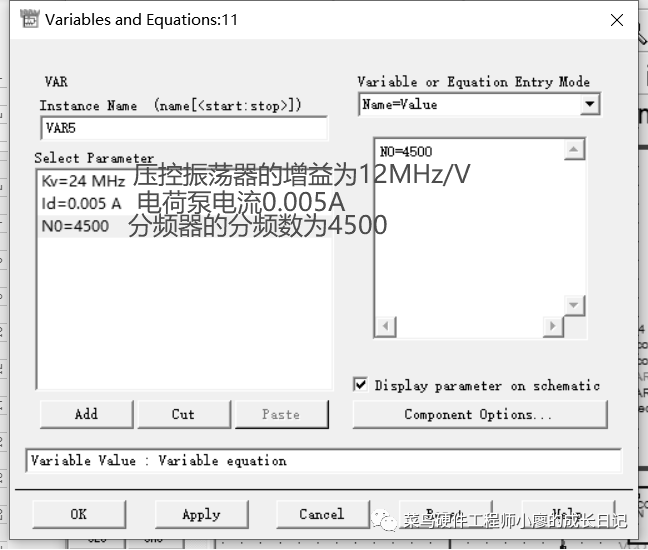

2、对VAR1、VAR2、VAR3、VAR4进行设置

对VAR1的设置要与上面优化的数据相同

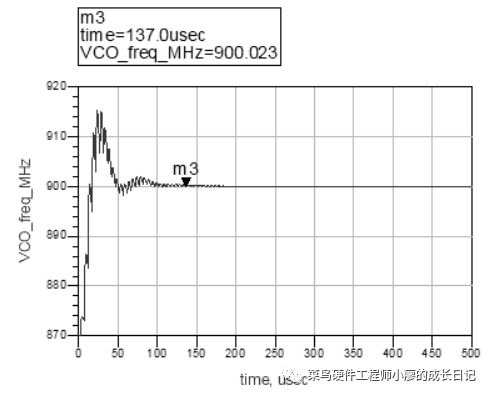

3、设置完成之后进行仿真添加“VCO_freq_MHz”,得到在900MHz,锁定时间大约为137us,满足小于200us的设计目标。

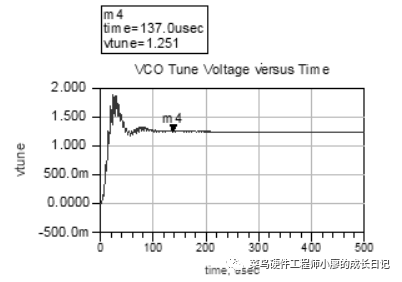

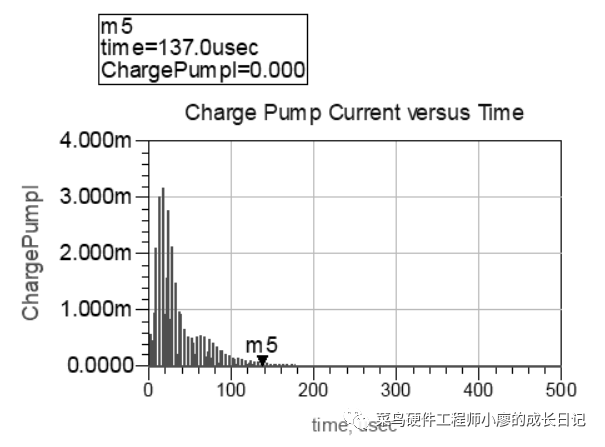

压控振荡器输入锁定电压为1.251V,在锁定状态下电荷泵电流为0,没有电流流过。

锁相环相位噪声仿真

锁相环相位噪声是锁相环最重要的设计指标,该指标决定了锁相环输出频率信号的纯度,在很大程度上影响着集成该锁相环系数的信噪比、动态范围等参数。

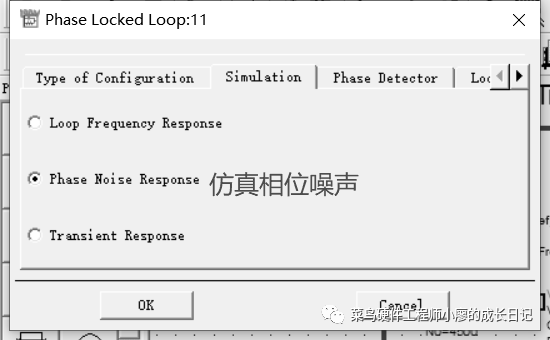

1、继续使用向导进行设计

生成的原理图如下:

2、对变量进行设置

3、对交流仿真控制器进行设置,都是默认。

4、进行仿真

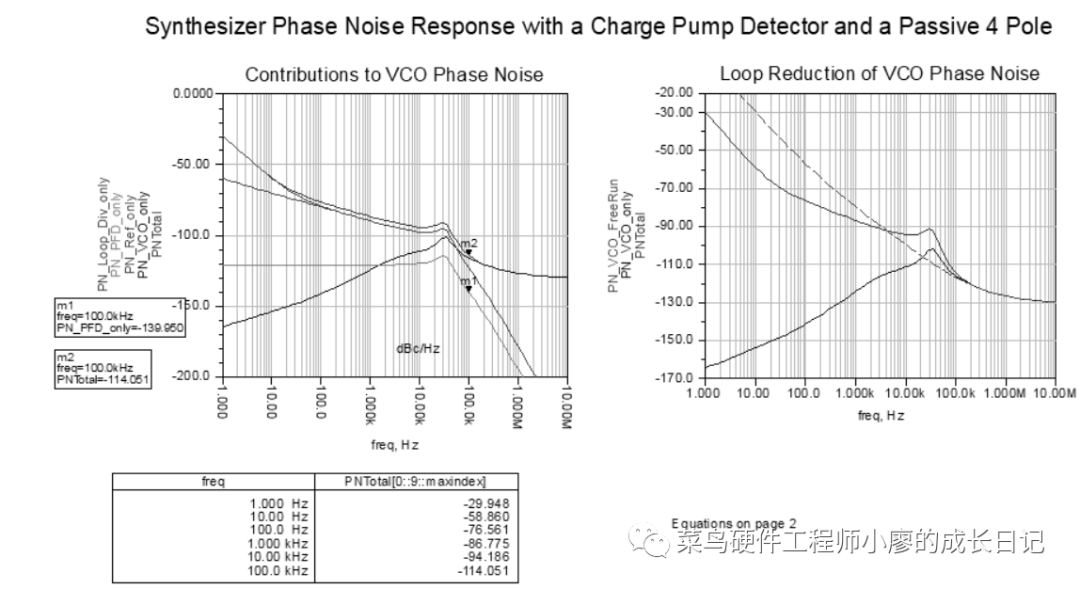

可以看到,在相位噪声100kHz是相位噪声-114.051dBc

从曲线可以看出,在环路带宽内,PLL输出信号的相位噪声主要由参考源、鉴相器(电荷泵)和分频器决定;在环路带宽外,相位噪声主要由VCO决定。即PLL环路对参考源、鉴相器(电荷泵)和分频器的相位噪声呈高通特性。由此可见,参考源、鉴相器(电荷泵)和分频器处的低频干扰很容易耦合到输出信号上,在设计中,需要注意这一点。

-

锁相环

+关注

关注

35文章

584浏览量

87734 -

压控振荡器

+关注

关注

10文章

133浏览量

29290 -

鉴相器

+关注

关注

1文章

60浏览量

23275 -

ADS仿真

+关注

关注

0文章

71浏览量

10434 -

环路滤波器

+关注

关注

3文章

26浏览量

13157

发布评论请先 登录

相关推荐

锁相环知识

请问能使用ADIsimPLL仿真双环锁相环吗?

CD4046锁相环设计

锁相环设计仿真与应用

锁相环设计与仿真的基本知识

锁相环设计与仿真的基本知识

评论