如果我们将两个4G内存插入内存插槽,得到的内存地址空间是0到8G吗?是不是0到4G是第一根内存,4到8G是第二根内存呢?实际情况相差甚远,内存在物理地址空间的映射是分散的。一部分原因是4G以下有Memory map IO(mmio)空间和PCIe的配置空间,另一个原因是Interleaving会打撒内存地址到各个Channel、DIMM甚至是Rank和bank上。今天我们就一起来了解一下x86系统的地址空间分布。

物理地址空间

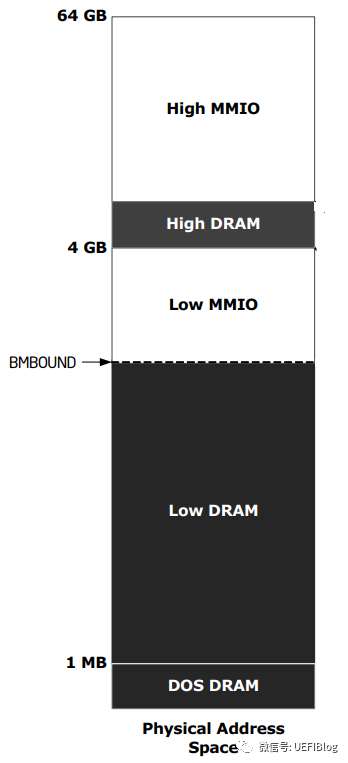

一个典型的物理地址空间是这样的:

其中只有灰色部分是真正的内存,其余都是MMIO。而内存被分为High DRAM和Low DRAM,如图:

为什么要把内存强行分割成两块呢?因为历史的包袱。最早内存都很小,32位的地址(4G)空间看起来永远也用不完,低地址被分配给内存用,高地址就自然而然被分配用来给Memory map IO。既然已经分给它们了,为了兼容以前的驱动,这一块就被固定下来。再有内存就只能从4G以上分配了。

Low MMIO和High MMIO

Low MMIO结构如下图:

其中有几块要特别说明一下:

1.Boot Vector的空间是BIOS内容映射的地址,它的大小是可以调节的,为了满足不同大小的BIOS。

2.Local APIC是APIC中断模式各个内核local APIC寄存器的映射地址。

3.PCI ECAM也有叫做PCIBAR,是PCIe配置地址空间的映射地址。它的起始地址可调,台式机BIOS一般会把它设置得很高,这样4G以下内存会比较大,方便32位Windows使用。举个例子,如果我们把PCIe BAR(BEGREG)设为0x80000000,那么尽管插了8G DIMM,4G以下也不会超过2G的内存可以使用,而2到8G的真实内存都被映射到在4G地址空间以上了,而这些是32位Windows使用不了的。所以有的主板运行32位操作系统发现可用内存小了一大块就是这个原因。它的大小可以修改,一般可以设为64MB和128MB。

High MMIO被BIOS保留作为64位mmio分配之用,例如PCIe的64位BAR等。

Low DRAM和High DRAM

4G以下内存最高地址叫做BMBOUND,也有叫做Top of Low Usable DRAM (TOLUD) 。BIOS也并不是把这些都报告给操作系统,而是要在里面划分出一部分给核显、ME和SMM等功能:

红框中是在low DRAM被“偷”的部分

4G以上的内存最高端叫做Top of Up Usable DRAM (TOUUD) ,再上面就是High MMIO了。

1MB以下比较特殊,里面全部都是已经被淘汰的传统BIOS和DOS关心的内容,我们叫它DOS Space或者Legacy Region:

在那里,我们习惯用传统的实模式地址来划分它们的具体内容:

1.0~640KB,传统DOS空间。

2.A段和B段,传统SMM空间。VGA的MMIO也被映射到这里,可以通过寄存器切换。

3.C段和D段,legacy opROM映射空间和EBDA空间。

4.E段和F段,BIOS空间的Lower和Upper映射地址。BIOS的rom内容也会被映射到这里,方便Legacy BIOS实模式跳转到保护模式。

内存的Interleave

从前面可以看出内存在地址空间上被拆分成两块:Low DRAM和High DRAM。那么在每块地址空间上分配连续吗?现代内存系统在引入多通道后,为了规避数据的局部性(这也是Cache为什么起作用的原因)对多通道性能的影响,BIOS基本缺省全部开启了Interleaving,过去美好的DIMM 0和DIMM 1挨个连续分配的日子一去不复返了。

什么是Interleaving?简单来说,就是让内存交错起来,如下面的动图:

这是一个bank层级的模4的interleaving。在桌面电脑上,常见的还有Channel级的、DIMM级的和Rank级的。

服务器上Interleaving更是不可或缺,它的粒度更细,可以达到数十bytes层级的interleave,它和内存的其他特性,如类似磁盘阵列RAID的内存spare, mirror特性,构成了复杂异常的内存映射系统。在BIOS里面,台式机/笔记本内存映射相对简单,只有一个大表和数十个寄存器;而在服务器BIOS中,有数个相互关联的大表和寄存器阵列来解码(decode)内存的请求,代码的硬件逻辑也是相当复杂。关于它,我会有一篇专栏文章讨论地址译码和地址反向解码,详细内容那里再说,这里只需要知道,物理内存分布在各个DIMM上就够了。

物理地址到内存单元的反推

BIOS实际上一手导演的内存的分配,它当然可以从任何物理地址反推回内存的单元地址。我们可以用下面一组数据来唯一确定某个内存单元:

Channel #;DIMM #; Rank #;Bank #;Row #;Column #

在内存分配表缺失的情况下,BIOS甚至可以通过它填过的寄存器重建这个映射表。但实际上BIOS并不希望一般用户知道这些信息,因为有安全性问题。

暴露内存信息容易招来内存侧信道攻击(Side Channel),比较有名的有Row hammer攻击。简单的来说它是通过反复写某个内存单元,借助内存的特性,希望影响相邻Row/Column的内容。

有些情况确实需要知道这些信息,就是内存出错的时候。和大家想象的不同,内存是会出错的。尤其云服务器中内存的出错是十分频繁的。出错起来也千奇百怪,开始可能是偶尔的随机错误,经过ECC等校正后,就再也不会复现;而有时是某个Bit总是出错,进而慢慢的整个row、column或者相邻的cell开始出错,从可以纠正的错误变成不可修正的错误,导致服务器必须停机。这时候就必须知道哪个内存坏了,进而换掉它。

报告给操作系统,但这个信息里面只有物理地址,如何才能知道是哪个内存单元坏了呢?在Linux上面可以通过edca(参考资料4),有编程经验的同学可以通过edca的程序接口(参考资料3),可以得到更加丰富的信息。

如何关掉Interleaving

对内存有特殊需求的朋友,如果希望内存连续,可以在BIOS里面关闭所有的Interleaving来达成这个目标:

注意是所有的。之后可以通过SMBIOS来看到内存分布信息(dmidecode)。

结论

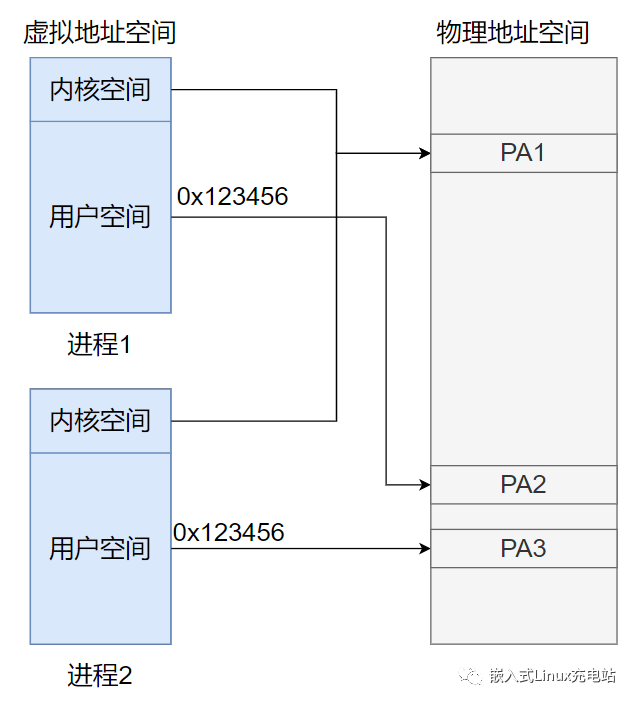

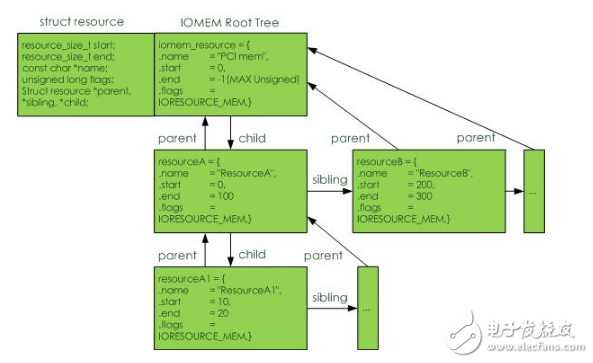

BIOS作为内存的大管家,也负责内存的分配和映射memory map。它会把这些信息通过E820, GetMemoryMap函数和SMBIOS传递给操作系统。操作系统在此基础上再建立页表,产生虚拟地址。

-

寄存器

+关注

关注

31文章

5356浏览量

120559 -

Linux系统

+关注

关注

4文章

594浏览量

27422 -

DRAM芯片

+关注

关注

1文章

84浏览量

18024 -

PCIe接口

+关注

关注

0文章

120浏览量

9723 -

DOS系统

+关注

关注

0文章

9浏览量

1404

发布评论请先 登录

相关推荐

鸿蒙内核源码分析:物理地址的映射

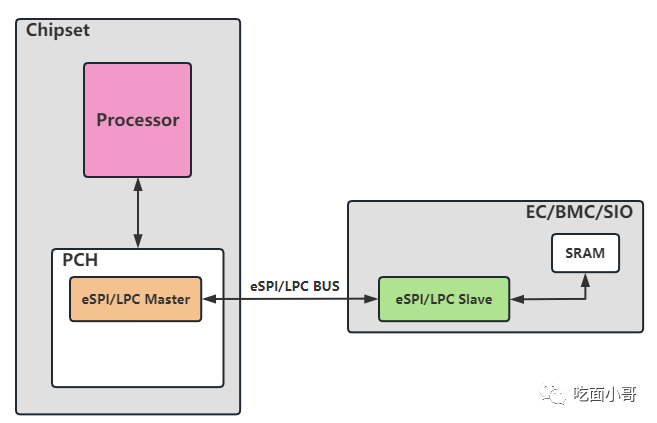

EC SRAM映射到CPU Memory空间的共享内存设计

【HarmonyOS】虚拟地址<->物理地址是如何映射的

鸿蒙内核源码分析(内存映射篇):虚拟地址与物理地址之间是如何映射的

Linux虚拟内存和物理内存的深刻分析

鸿蒙内核中虚拟地址与物理地址之间是如何映射的

Linux虚拟地址空间和物理地址空间的关系

内存是怎么映射到物理地址空间的?内存是连续分布的吗?

内存是怎么映射到物理地址空间的?内存是连续分布的吗?

评论