Axiom Microdevices,Inc AX502 design guidelines on MTK platform,很具代表性。

具体还是要参考所用的PA的Design Guideline

实际调试来说,考虑返回路径,除了Top分割外,其它层无需这样分割,对于平台性能差的芯片厂商的芯片而言地分割仔细可能会好点,目前来说不需要每分割。

1. PA输出匹配

PA输出匹配根据不同的PCB会有些不同,PA应当根据当前的PCB匹配在50欧姆。参考PA load pull 图表。

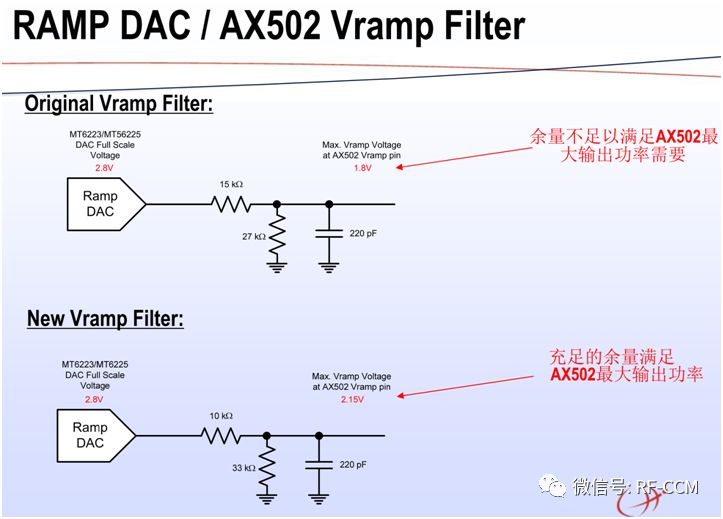

参考原理图中Vramp 滤波器是针对XCV对DAC噪声以及PA最大输出功率对DAC值范围的要求设计的。主要还是要依据Qualcomm的参考原理图,控制Switch 打开的时间可以调整ramp底部的台阶形状。可以很快的ramp-down并且保持开关谱不会变差,即PA+ASM Switch控制,可通过更改相关NV来解决。

**3. **PA ramping profile

这个PA Ramp是基于参考原理图中所示的PAVramp滤波器的情况下获得的值,如果实际中的Vramp滤波器不同于原理图中所示,则整个PAramp需要重新调。

4. PVT和开关谱

PVT和开关谱之间是相辅相成的。3GPP规定MS(Mobile Station) 在时域满足PVT的同时在频域也需要满足对开关谱的要求。为了满足PVT和开关谱的要求,两项指标需要进行调整,分别是:

- PA Timing对时序进行调整。

- PA rampingprofile.

我们提供针对AX502调试的PAramp文件作为Ramp的初始值以便进一步微调。需要注意的是,这个PA Ramp是基于参考原理图中所示的PA Vramp滤波器的情况下获得的值,如果实际中的****Vramp 滤波器不同于原理图中所示,则整个PA ramp 需要重新调 。

5. 为什么在AX502 LB输入要串一个8.2nH 的电感, HB输入串一个3.9nH的电感?这些值会根据不同的layout 需要改变吗? Layout****的时候这些电感应当怎样放置?

电感是用来匹配PA输入的。这些电感需要尽量靠近PA。具体值可以根据不同的layout做一些微调。

6. 为什么在AX502 HB输出串联一个6pF 的电容, LB输出串联一个12pF 的电容? Layout****的时候需要注意什么?

为了改善二次谐波性能以及隔直。尽量靠近PA放置,可以是普通精度

的电容。

7. Vbat管脚上的大电容推荐值是多少?

22uF

8. 为什么在VbatC管脚上串联一个10nH****的电感?可以去掉么?

经过调试如果不需要可以去掉。

9. 为什么要在VbatC管脚上并联一个82nF****电容而不是其它值?

经验值!可以换成100nF。

**10. **VBATC 的作用是什么 ?

VbatC是给PA内部除了功放电路以外的RF电路供电的,例如输入放大器,和其它敏感电路像功放控制模块和偏置模块供电。对这些电路来讲,一个干净低噪的电源是有必要的。

**11. **Vbat 宽度有没有最小值 ?

Vbat主干部分应该至少在2mm以上。连接各个管脚的分支最细不应该低于0.7mm(或30mil)。

12. TRX HB输出的pi型网络以及低通滤波器件应当如何放置?

低通滤波器件和pi型网络是MTK推荐用来TRX输出匹配用途的,应当非常靠近MT6139输出管脚并且放置在TRX的屏蔽框内。

13. LB的****Tx SAW 滤波器需要怎么放置? Layout****中可以去掉么?

Tx SAW 滤波器是推荐抑制杂散的,应当靠近XCV输出管脚。如果不需要可以去掉。

14. PA器件布局相关

1. PA输入匹配,靠近 PA ,PA 输出匹配,靠近 PA

2.Vbat旁路电容,靠近Vbat管脚

3.TxSAW 滤波器是推荐抑制杂散的,应当靠近****XCV 输出管脚 。如果不需要可以去掉

**15. ****Phase Error **问题解决办法

HB的Phase error 性能对反向牵引VCO的二次谐波很敏感。

VCCRF 2.8V LDO 需要加上磁珠进行很好的隔离。并且需要加一些大小值比较合适的旁路电容。另外,尽量避免VCCRF这条线离PA太近。最好将PA的VDD与DA和TxEN连在一起。平台厂商推荐的RF屏蔽和接地原则需要严格的遵守。

**16. 调试Phase Error ** 需通过以下步骤来解决 :

- 首先要确保PA已经匹配了。

- 然后尝试调靠近PA Vbat的几个旁路电容,把其中一个或全部47pF电容改成7pF可能有些帮助。在PAVDD管脚上放置一个12pF的旁路电容也许会有改善。

- 进一步,可以尝试在MT6139VCCTXMOD管脚附近放一个6.8pF电容接地,VCCTXBUF上放一个22pF的电容接地。

- 如果通过以上步骤问题还是存在,那么可以开始调试XCV输出的pi型滤波器来进行改善。通过将串联电感的值变大变小进行粗调,然后调试两边的并联电容进行细调。

**17. **** 15. ** 为什么调制谱 **±200kHz offset ** 不过 ?

基本上这个问题与PA无关。检查是否频率误差太大。

**18. ** 为什么调制谱 ± 1.2MHzoffset在Low Band 不过 ?

这是由于从TRX到PA HB的传输线不是50Ohm,因此当PA工作在LB的时候HB的off-impedance 会影响LB的输入匹配。在HB输入串联一个电感就可以解决这个问题。

**19. 这个PA的up and down- ramping **为什么台阶很高?

这是因为T/R switch 此时没有用来调整PVT。可以调整PA和ASM打开的时间来调节这个台阶。

**20. ** 为什么开关谱余量很小 ?

需要调整Tx Timing 和PA ramping来满足开关谱的要求。但是这两项都会根据不同的layout有一些微调,我们提供的文件只能作为初始化文件,可能后续还需要做一些微调来获得开关谱更多的余量。

**21. **不带屏蔽盖的情况下调好了 Phase Error ,为什么盖上屏蔽盖以后 **Phase Error **又变差了。

这是因为盖上屏蔽盖从空间上改变了TRX的负载。可以用不带屏蔽盖调试PhaseError一样的方法调试后,盖上屏蔽盖检验是否调

** 22. V-drop @ HPM**

在GSM大功率发射的时候总是会遇到VBAT下降的问题,这个问题的根源是电源走线通常有0.2Ω的阻抗。而大功率发射时候的最大电流基本为1.5~1.6A,所以1.50.2Ω=300mV,而可以接受的最大数据为1.60.2Ω=320mV,所以若电源电压下降300mV内的话可以接受,但是需要注意PDN的设计,尽量使得PDN的阻抗最小。

** 23. PA DC Block CAP**

如果一个射频器件的输入或者输出脚内部没有加隔直电容,而且脚上面有静态偏置电压的话,一般都需要加隔直电容。

隔直电容的作用是防止前后级之间由于偏置电压不同,导致偏置电压拉升或降低,PA工作状态改变。可通过测量来判断“脚上面是否有静态偏置电压” 。

-

电感器

+关注

关注

20文章

2321浏览量

70389 -

低通滤波器

+关注

关注

14文章

471浏览量

47305 -

ASM

+关注

关注

1文章

68浏览量

19003 -

VDD

+关注

关注

1文章

311浏览量

33081 -

PCB走线

+关注

关注

3文章

133浏览量

13902

发布评论请先 登录

相关推荐

为什么在AX502 LB输入要串一个8.2nH的电感?

为什么在AX502 LB输入要串一个8.2nH的电感?

评论