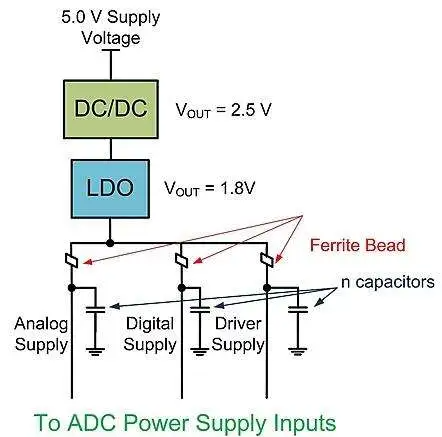

我们发现,使用DC/DC转换器降低LDO的输入电压是驱动ADC电源输入的一种更有效的方法。提醒一下,下面的图 1 给出了此拓扑。输入电源电压为5.0 V,降压至2.5 V,然后输入至LDO,ADC电源电压具有1.8 V输出。

图1

利用 DC/DC 转换器和 LDO 驱动 ADC 电源输入

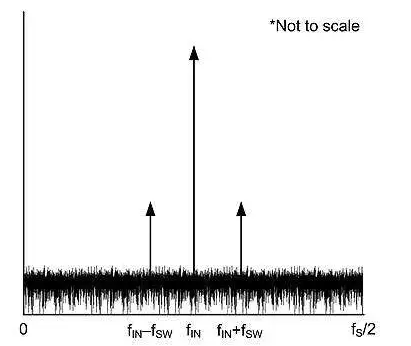

我想花点时间进一步扩展一下我之前在本例中提到的一个主题,即围绕ADC基波输入音的潜在杂散。这些开关杂散的位置将取决于DC/DC转换器的开关频率和ADC的输入频率。开关杂散将与输入信号混合,杂散将在fIN — fSW和fIN + fSW产生(如下图2所示)。

图2

带开关杂散的数字化ADC数据的FFT

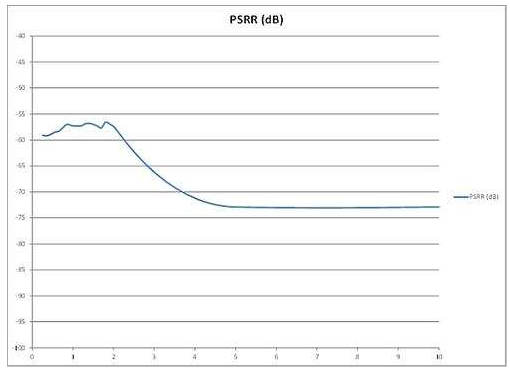

好消息是,通过适当的设计,这些杂散的幅度可以最小化,并且在许多情况下低于ADC频谱中的谐波或其他杂散,因此它们不是问题。因此,让我们看看关于这些马刺需要考虑的一些事情。一些普遍的想法是,LDO将“清理”这些开关杂散,因为LDO具有高PSRR(电源抑制比)。实际上,PSRR通常非常适合高达几百千赫兹的LDO。

超过几百千赫兹,PSRR通常会开始相当快地退化。通常,系统中的许多电源噪声通常都在此频率范围内,因此LDO可以很好地充分抑制它。AD9683(AD9250的单通道版本)等ADC的PSRR在2 MHz以上表现出更好的PSRR,如下图3所示,PSRR高达10 MHz。这在开关频率周围留下了一个区域,其组合PSRR低于预期。

图3

AD9683的PSRR曲线

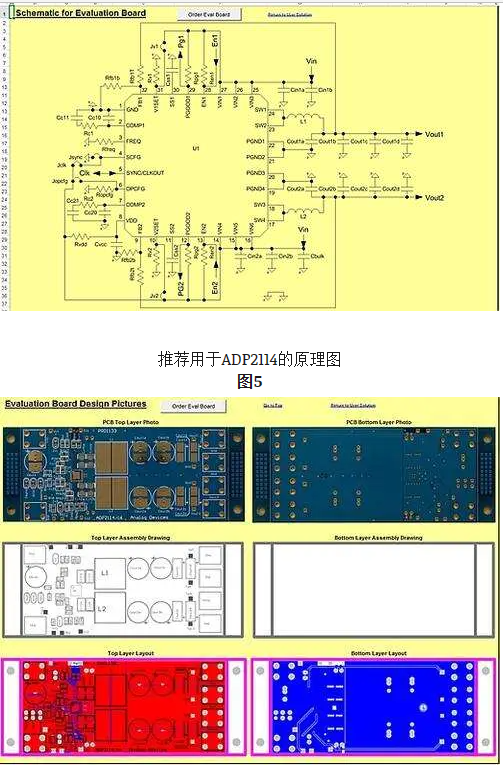

DC/DC 转换器的开关频率通常为 400-500 kHz,最高可达 1-2 MHz。以这种速率产生的开关杂散可能不会被LDO和/或ADC完全滤除。这些杂散可以直接通过,并可能出现在ADC的输出频谱中,如图2所示。也就是说,除非DC/DC转换器布局和输出滤波设计正确,否则它们将通过。这就是为什么拥有适当的电路设计和布局很重要的原因,如图4和图5所示,我们上次也看过。

图4

推荐的ADP2114布局

如图3所示,通过在LDO输出端采用适当的电路设计和良好的滤波器设计,可以大大降低开关杂散。然而,这本身并不是全部,注意布局也很重要。与任何高频或开关器件一样,重要的是要注意电流返回路径,以确保开关噪声不会进入ADC或可能也位于同一电路板上的其他组件。保持这些当前返回路径非常小非常重要。在设计中,将它们与敏感节点保持物理隔离也很重要,这样开关噪声耦合就会降至最低。

如您所见,需要考虑许多方面,但这就是工程同时如此具有挑战性和乐趣的原因。

审核编辑:郭婷

-

电源

+关注

关注

185文章

17969浏览量

252901 -

转换器

+关注

关注

27文章

8783浏览量

148862 -

ldo

+关注

关注

35文章

2145浏览量

154446

发布评论请先 登录

相关推荐

ADC接口:电源,第5部分

ADC接口:电源,第5部分

评论