概述

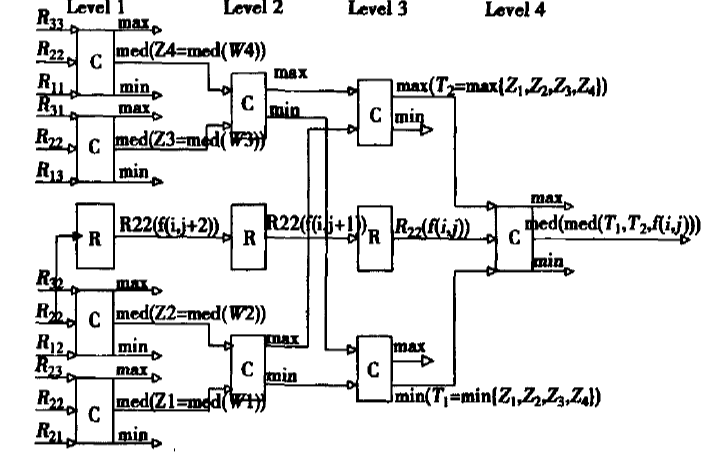

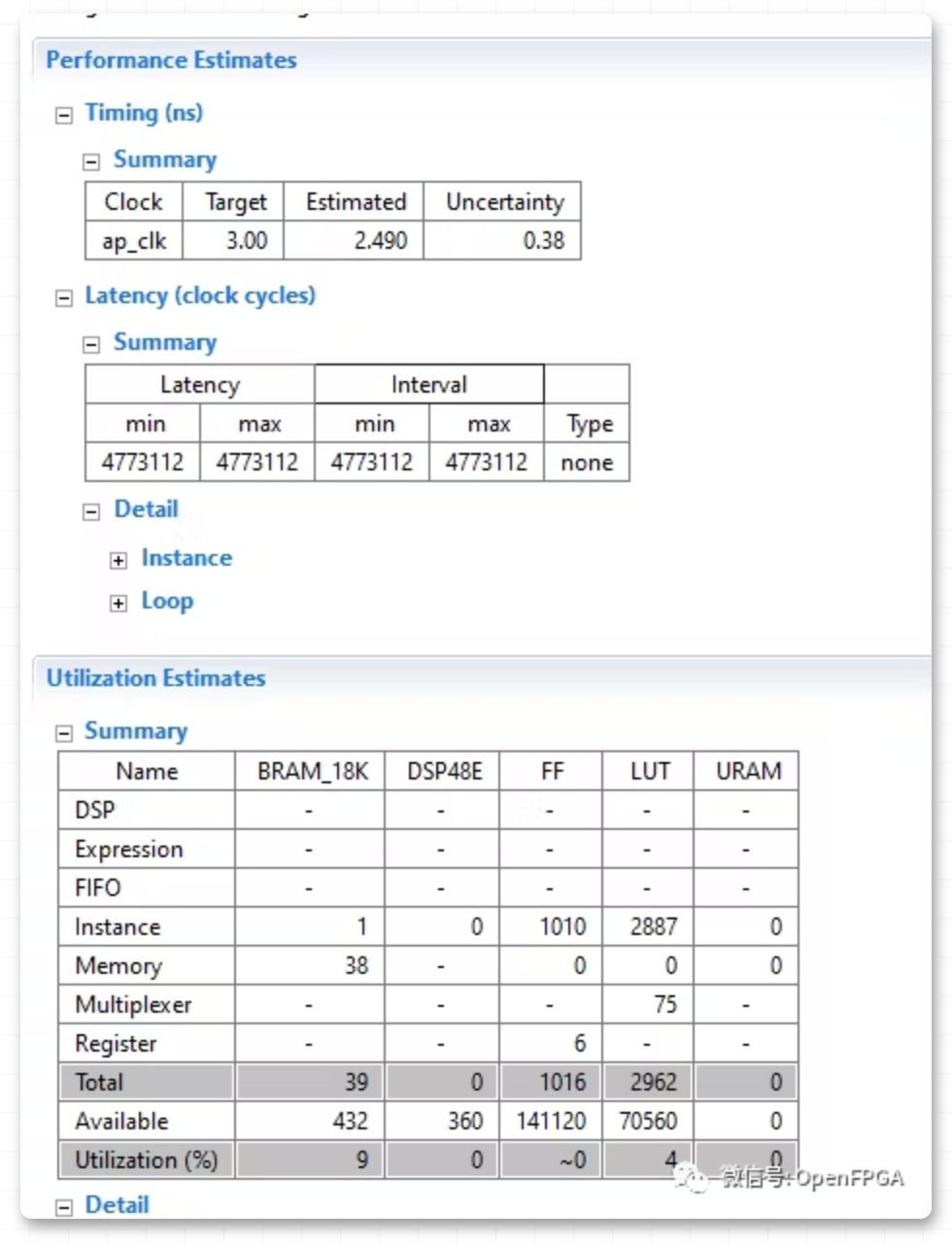

该项目包含使用高级综合 (HLS) 的 2D 中值滤波器算法的实现。该项目的目标是在不到 3 ms的时间内对测试图像进行去噪,同时消耗不到 25% 的可用 PL 资源。特征如下:

包含具有任意精度数据类型的高效数据类型管理。

采用 HLS 编译指示来确保最佳系统性能。

通过多个测试用例进行验证。

内容

该项目包含以下内容:

2D中值滤波器算法的源代码文件

C 仿真文件

协同仿真文件

综合文件

包含干净和有噪声的图像数据的 CSV 文件

仿真和综合过程的屏幕截图

设置和安装

该项目已在 Vivado HLS 中设计和测试。要设置并运行项目:

克隆此仓库:git clone

打开 Vivado HLS 软件并导入项目。

加载包含图像数据的 CSV 文件。

运行 C 仿真以确保算法正常运行。

进行综合和协同仿真。

用法

将项目导入 Vivado HLS 后:

运行 C 仿真以验证中值滤波器的功能。

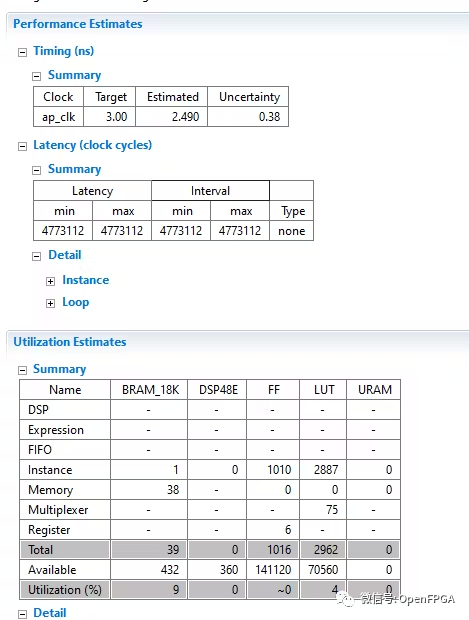

执行综合过程以查看资源利用率报告并进行必要的调整。

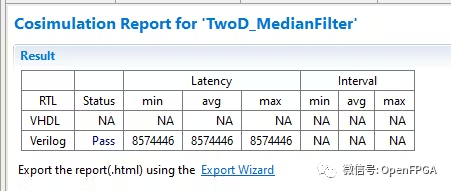

执行协同仿真以确保综合设计的行为符合预期。

请注意:可能需要根据所使用的 FPGA 板调整代码中的 HLS 编译指示以获得最佳性能。

最终设计应用于测试数据时,在不到 12 ms的时间内实现了去噪,总体 PL 资源利用率约为 13%。

审核编辑:刘清

-

FPGA

+关注

关注

1629文章

21754浏览量

604235 -

滤波器

+关注

关注

161文章

7843浏览量

178378 -

Vivado

+关注

关注

19文章

813浏览量

66657 -

HLS

+关注

关注

1文章

130浏览量

24144 -

csv

+关注

关注

0文章

39浏览量

5832

原文标题:2D 中值滤波算法实现

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于算术平均算法的中值数字滤波器设计

使用高级综合HLS开发2D中值滤波器算法

使用高级综合HLS开发2D中值滤波器算法

评论