编 者 按

续接上文,接续扒一扒PCIe中的Flow Control

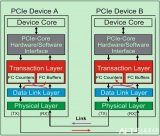

链路层把TLP分为几类?

在处理TLP报文时,根据Fmt字段以及Type字段可以将TLP报文分为二十多种,当TLP报文送至数据链路层时,数据链路层在进行流量控制处理时则不会考虑这么多种情况。数据链路层里面的Flow Control,则会将报文分为三类:

Post:不需要Target端返回响应报文的TLP请求。

Non-Post:需要Target端返回响应报文的TLP请求。

Cmpl:响应TLP报文。

而同时,数据链路层在进行流量管理时会将TLP的数据报文头、数据负载分开进行流量控制。也就意味着数据链路层的流量控制每个VC分为了六个通道:

Post Header

Post Data

Non-Post Header

Non-Post Data

Cmpl Header

Cmpl Data

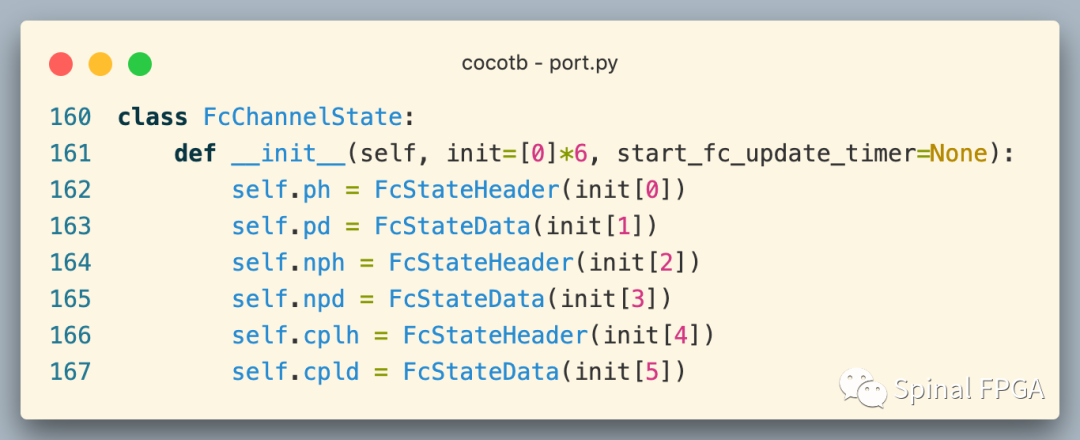

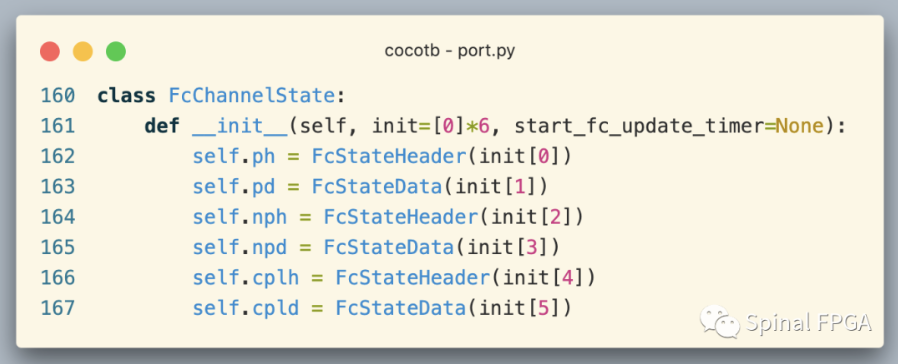

这在cocotb-ext中的FcChannelState中可以看出:

Flow Control初始化

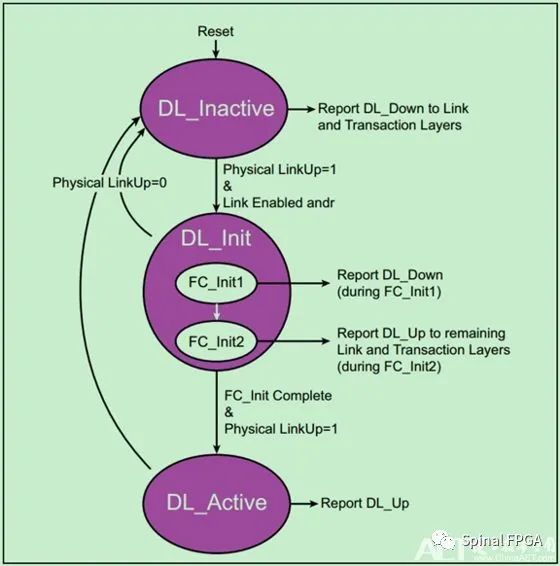

Flow Control的初始化在DL_INIT中:

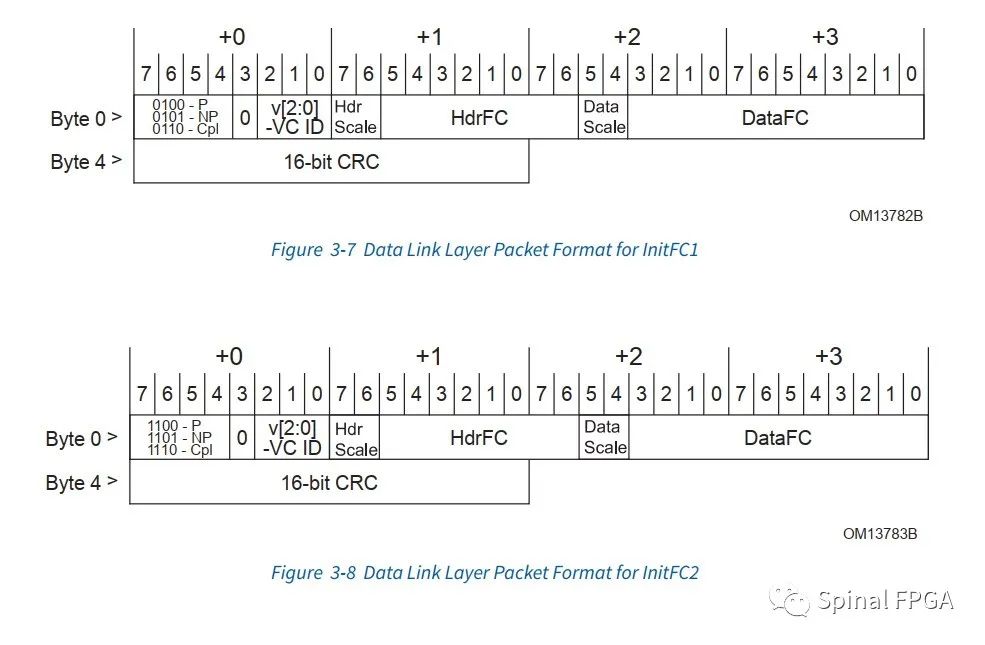

所用到的DLLP报文为:

按照Spec里面的规定,Flow Control的初始化顺序为:

InitFC1-NP (second)

InitFC1-Cpl (third)

无论是InitFC1、InitFC2,其报文格式定义基本相同。InitFC1、InitFC2所做的事情也基本相同,就是告知发送端Header、Data的令牌数。看到一段网上的解释:“FC_Init1和FC_Init2干的活不是差不多嘛,为什么还需要FC_Init2呢?原因是,不同的设备完成FC_Init1的时间可能是不同的,增加FC_Init2是为了保证每个设备都能收到FC初始化DLLP。”

如果FC为0,则表示该通道不受令牌限制,即无流量控制(EP设备以及不支持P2P的RC的Cmpl常设为0,故建议在涉及时对于Cmpl时建议仔细考虑。像Xilinx PCIe IP EP模式的的RC接口,不建议做反压)。

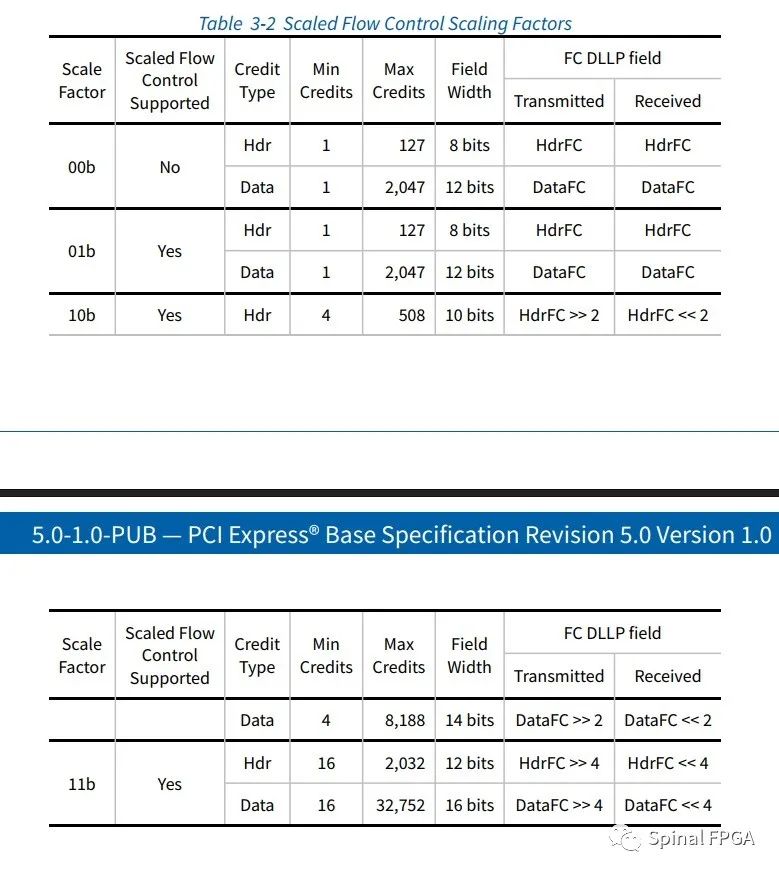

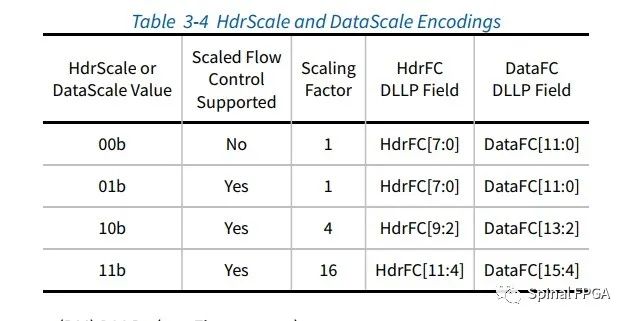

这里着重看下 Scale和FC域,FC域为12bit,随着PCIe链路速度的提升,Spec规定了Scale域以扩大令牌数:

按照协议里,最大可以支持到16bit。而FC域仅有12bit,协议里规定了FC的定义:

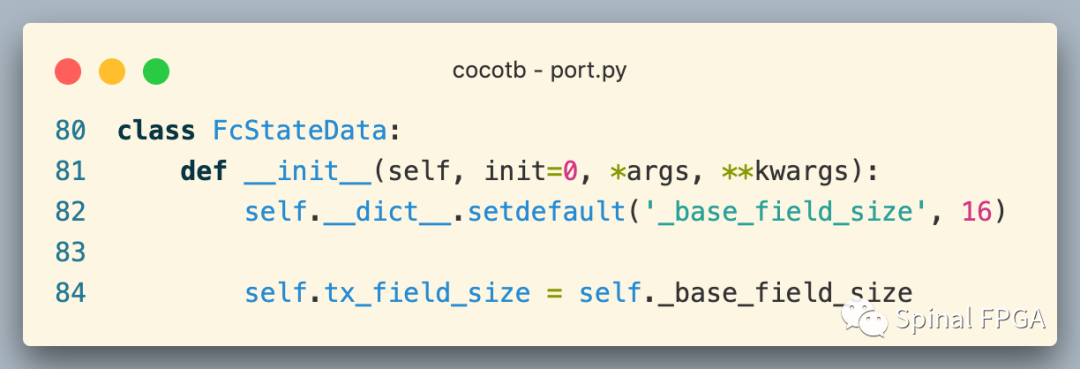

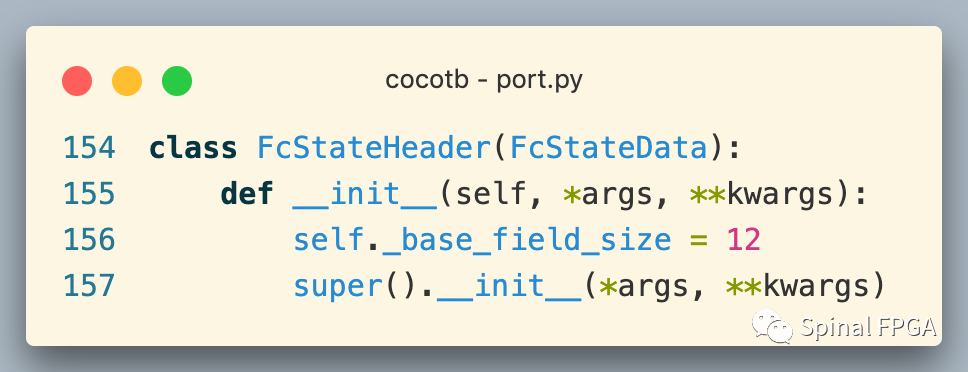

在cocotbext-pcie里,关于FC位宽的定义,Header、Data采用12、16bits:

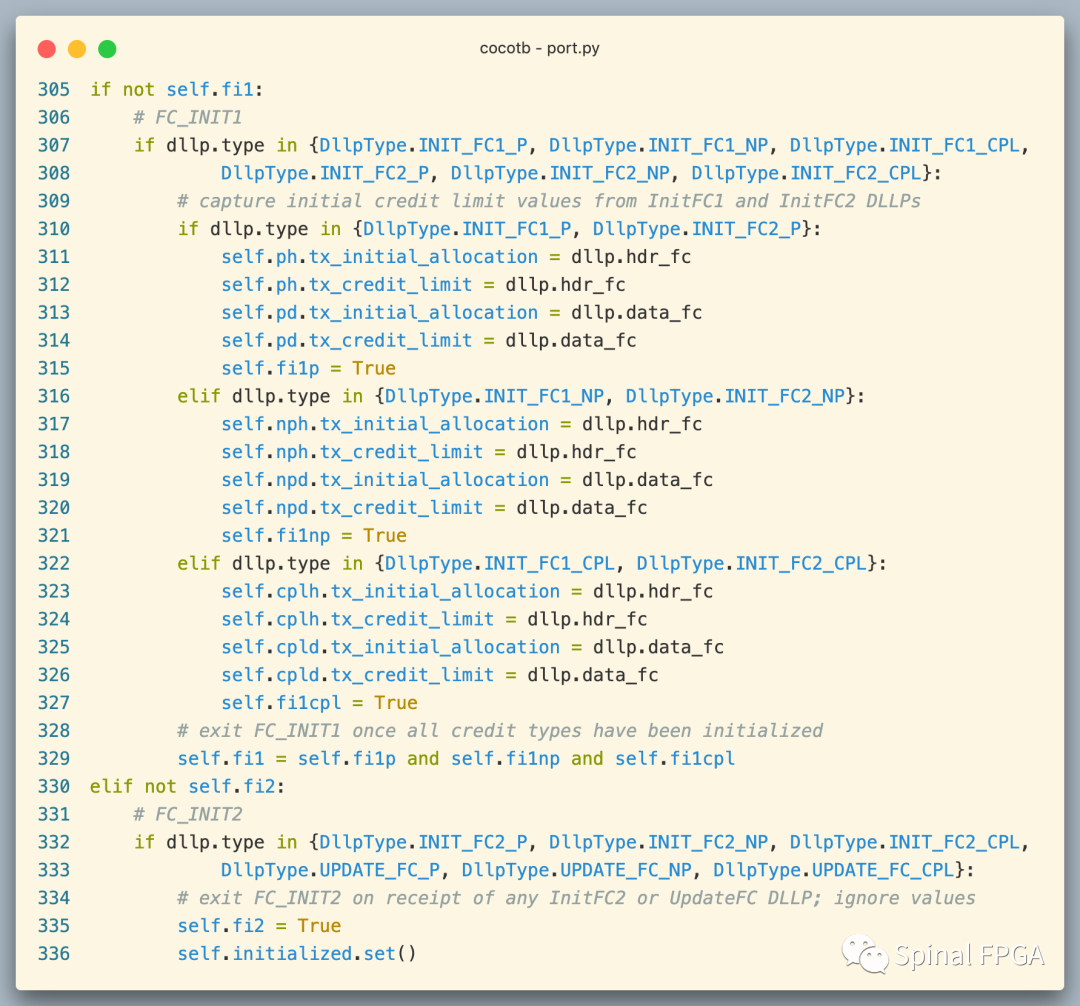

Flow Control的初始化在cocotbext-pcie中也很明了简单:

可以看到,由于FC_INIT1、FC_INIT2内容基本一致,FC2基本没有做什么处理(具体真实的实现不了解)。

》令牌消耗

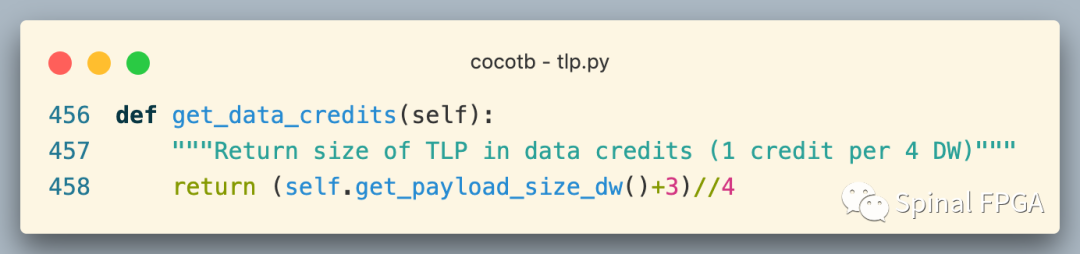

发送端发送一个TLP报文,在数据链路层需消耗Header、Data令牌。每一个TLP报文需消耗一个TLP,而如果有数据负载则每四个DW消耗一个Data令牌:

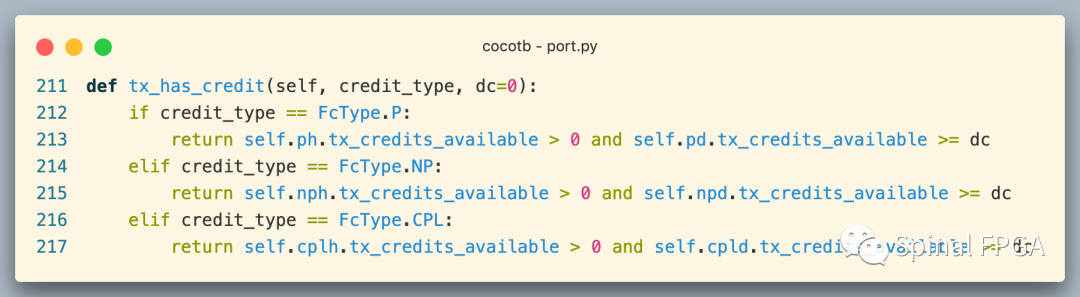

数据链路层进行判定是否能发送该数据出去:

》令牌更新

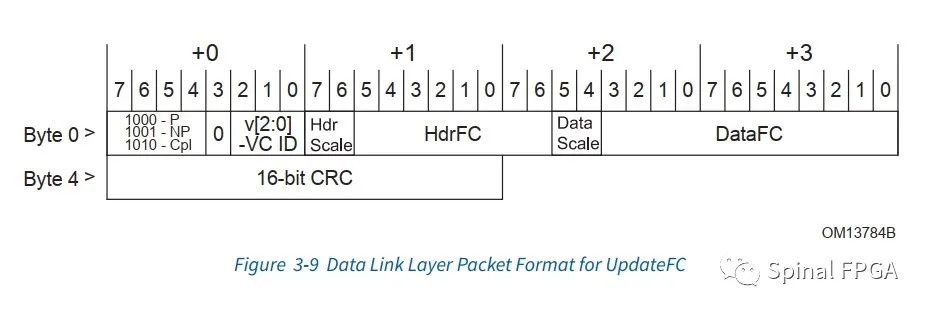

令牌周期性的更新所用到的DLLP格式为:

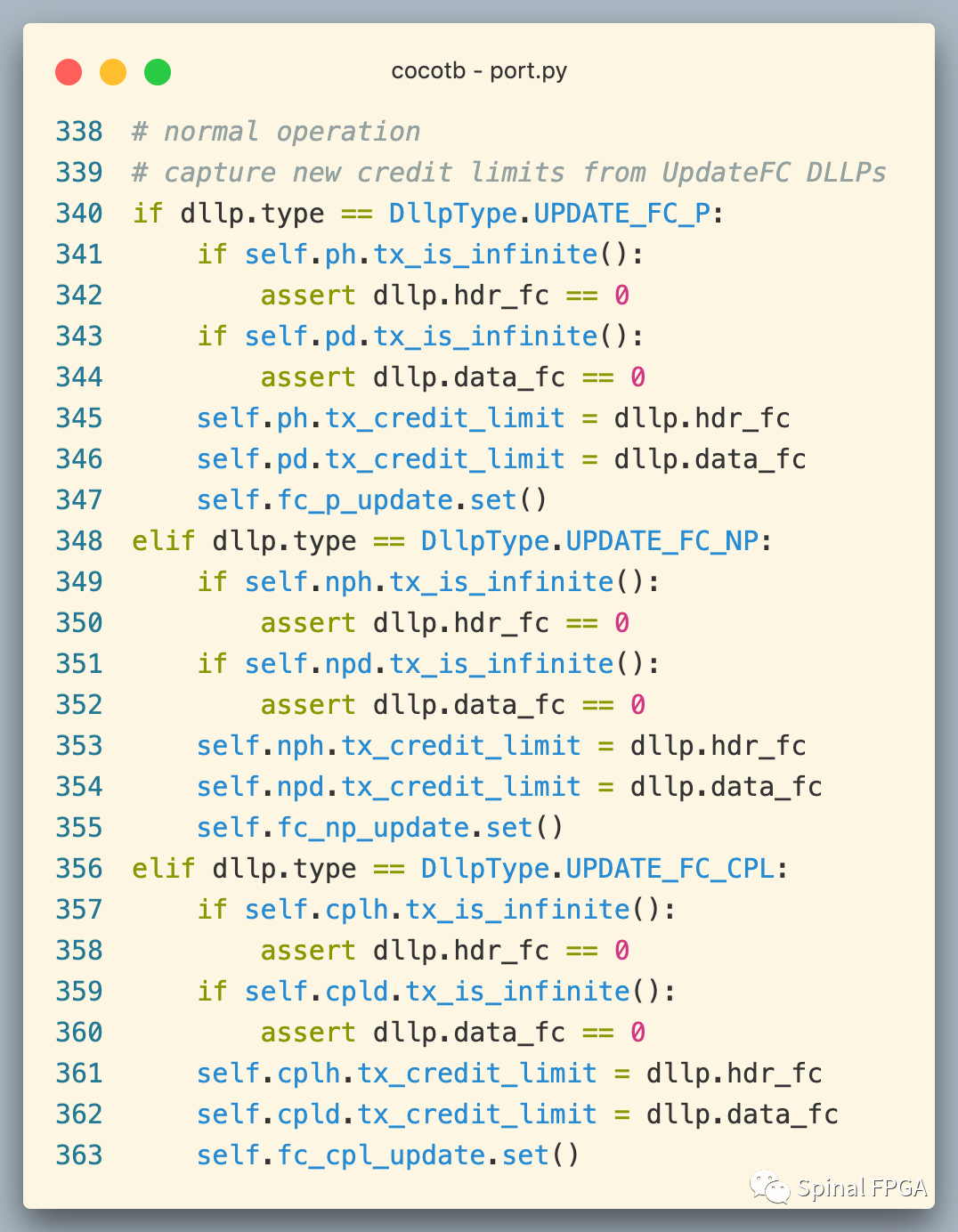

接收端按照HdrFC、DataFC中的内容更新其令牌:

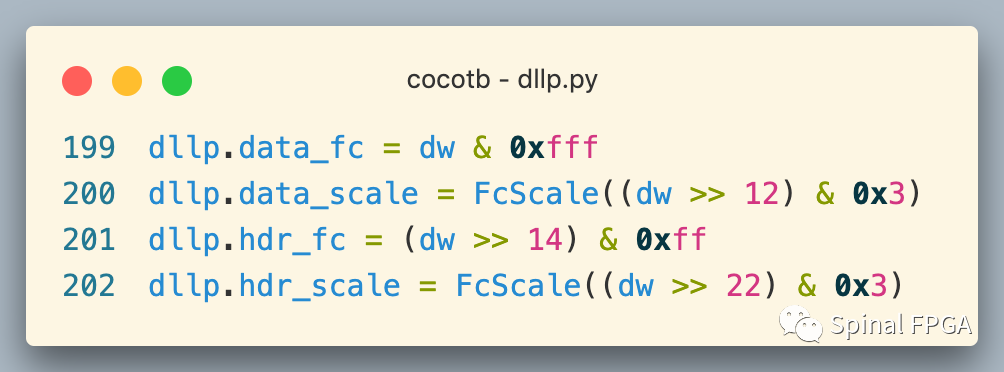

这里面看起来有一点不太合适的地方就是没有考虑Scale,按照DLLP里面的报文解析:

由于FC只有12bit,这里对于16bit的场景支持欠妥。

更新周期

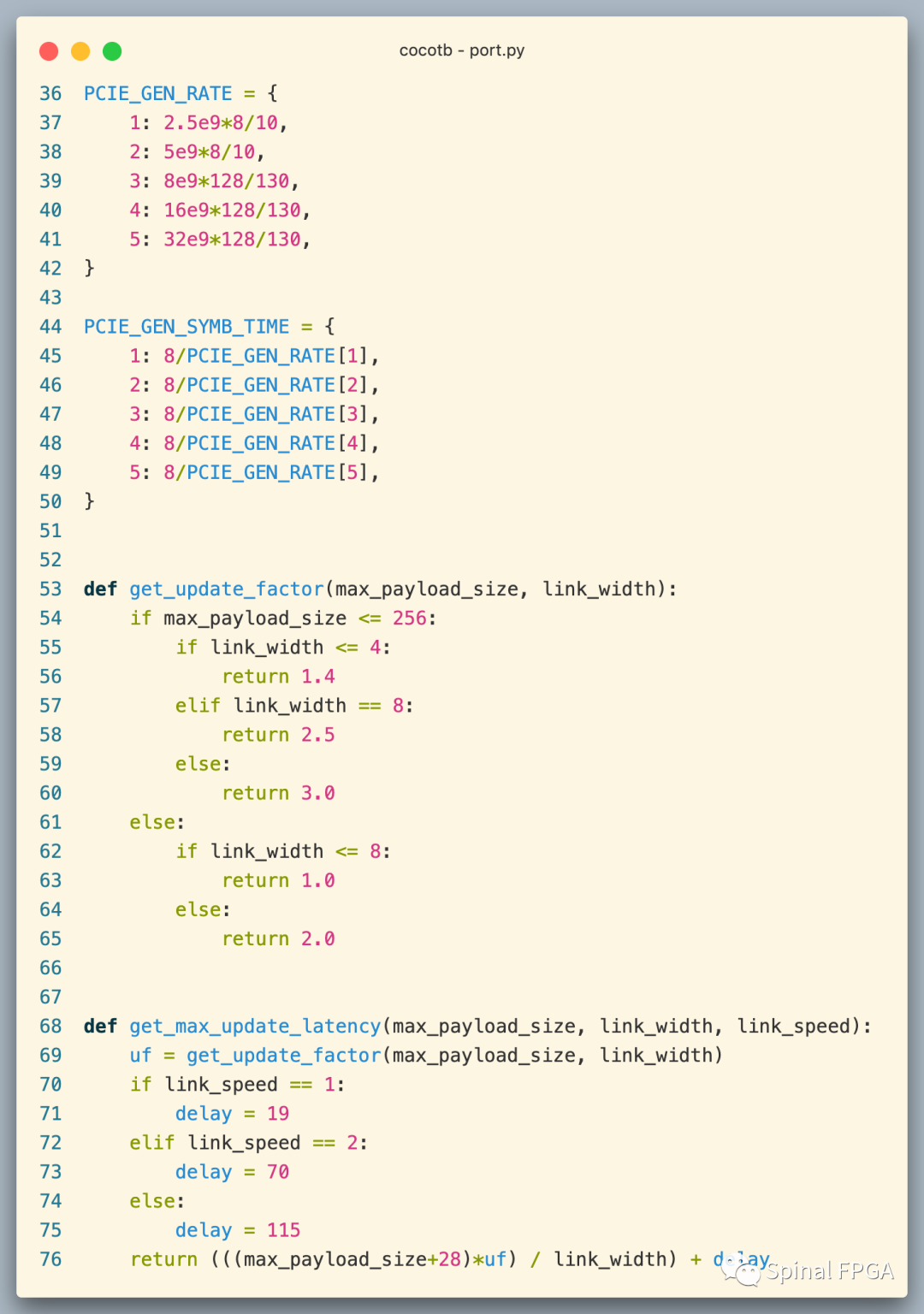

无论是Flow Control还是之前所说到的ACK/NAK,协议中都规定了最大发送间隔时间。在cocotbext-pcie中的计算方式如下:

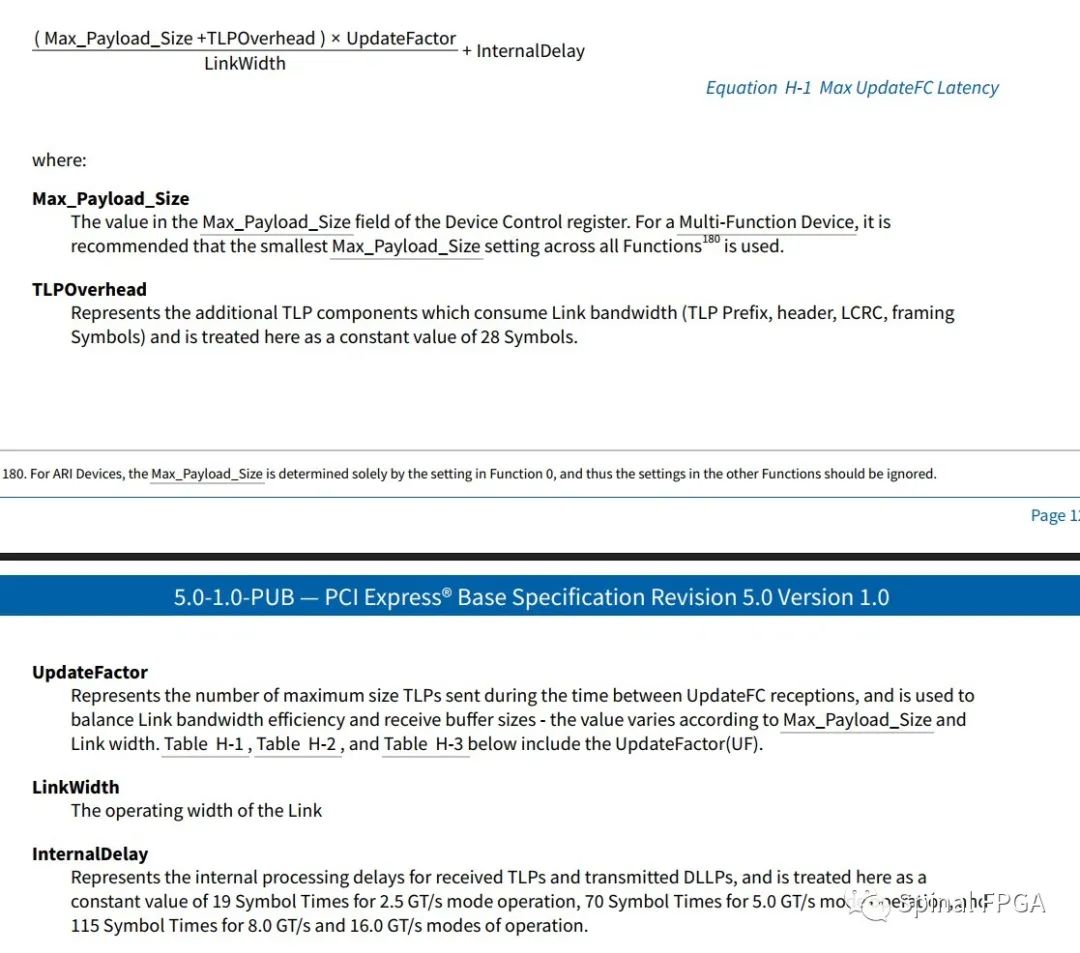

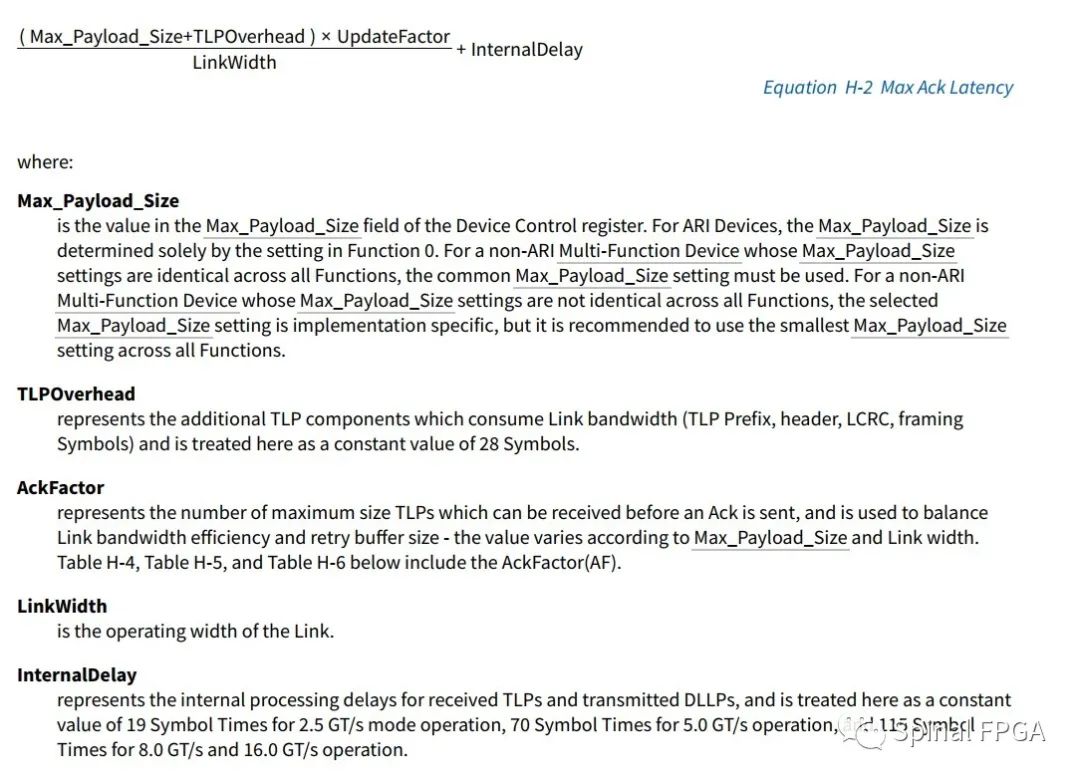

这里面的计算单位是Symbol Time(物理层发送1Byte数据的时间)。这里面可能乍看懵逼,这部分在PCIe Spec 5.0里对应Appendixes H里:

Flow Control Latency:

ACK Latency:

审核编辑:汤梓红

-

FPGA

+关注

关注

1630文章

21796浏览量

605764 -

PCIe

+关注

关注

15文章

1258浏览量

83127 -

TLP

+关注

关注

0文章

32浏览量

15662 -

Flow

+关注

关注

0文章

10浏览量

8857 -

报文

+关注

关注

0文章

38浏览量

4065

原文标题:原来如此—PCIe的Flow Control

文章出处:【微信号:Spinal FPGA,微信公众号:Spinal FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

扒一扒与无线网络相关的那些事

扒一扒我看过的那些Linux相关的书籍

扒渣机产品有哪些参数

扒一扒C语言hello world背后的内幕

美容仪哪个牌子好?来扒一扒令人眼花缭乱的日本美容仪

扒一扒好用的日本家用美容仪品牌,让你享受清洁肌肤的乐趣

扒店saas系统创新性服务平台的优势是什么

扒一扒中断为什么不能调printf?

扒一个超棒的stm32的开源usb-can项目,canable及PCAN固件

扒一扒PCIe中的Flow Control

扒一扒PCIe中的Flow Control

扒一扒PCIe中的Flow Control

评论