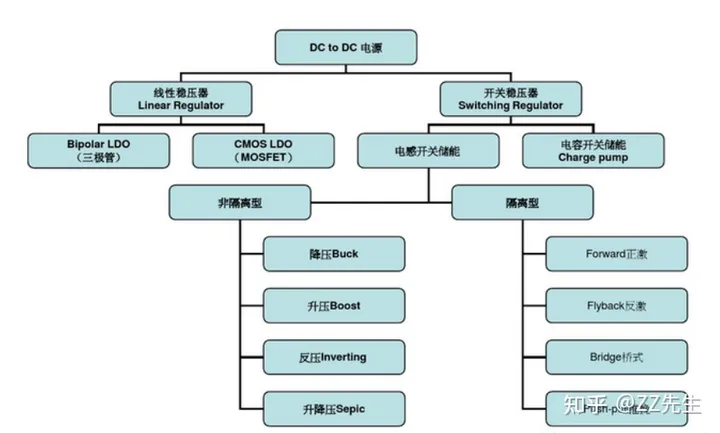

本文旨在帮助设计人员了解DC-DC补偿的工作原理、补偿网络的必要性以及如何使用正确的工具轻松获得有效的结果。该方法使用LTspice中的一个简单电路,此电路基于电流模式降压转换器的一阶(线性)模型。使用此电路,无需执行复杂的数学计算即可验证补偿网络值。

背景知识

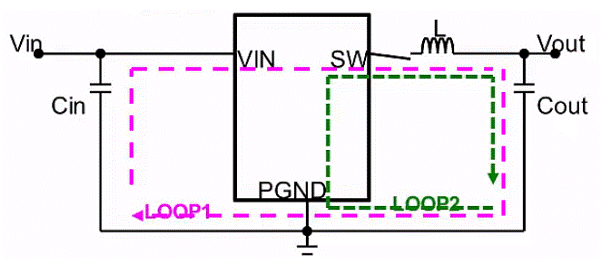

设计DC-DC转换器时,应仔细选择FET、电感、电流检测电阻和输出电容等元件,以匹配所需的输出电压纹波和瞬态性能。在设计功率级之后,闭合环路也很重要。DC-DC电源包含一个使用误差放大器(EA)的负反馈环路。在负反馈系统中传播的信号可能会在其路径中遇到极点和零点。单个极点会使信号相位减小约90°,并使增益斜率减小-20 dB/Dec,而单个零点会使相位增加约90°,并使增益提高+20 dB/Dec。如果信号的相位减小-180°,则负反馈环路可能变成正反馈环路并发生振荡。保持环路稳定并避免振荡是电源的设计准则。

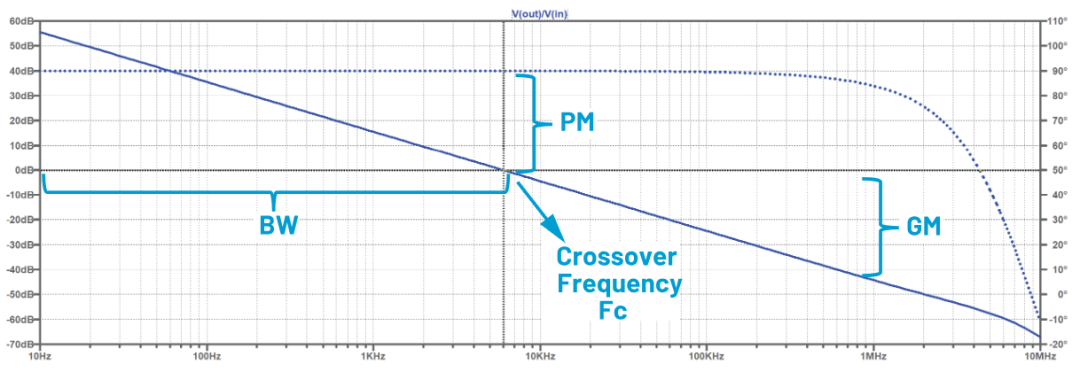

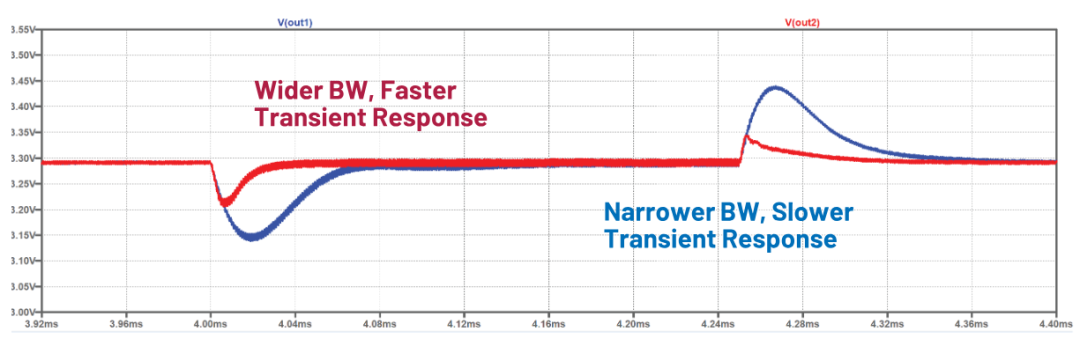

测试DC-DC稳定性的方法有两种。第一种是频率响应分析(FRA),此方法将会创建波特图。第二种方法是时域分析,此方法将会使负载电流发生瞬变,并可观察到输出电压的欠冲和过冲响应。为了实现稳定的设计,应确保避免相位降低-180°的情况,并保持相位裕量(PM)大于45°。相位裕量为60°是较为理想的情况。当电源设计的带宽(BW)较宽时,器件对电流负载变化的响应会更快。电源的带宽是0 dB增益与频率轴交点的频率。该频率也称为交越频率Fc,可观察到其相位高于45°。DC-DC转换器的带宽是其开关频率Fsw的导数,通常在Fsw/10 < Fc < Fsw/5的范围内。越趋近于Fsw/5则意味着带宽越宽,实现起来也会更难。带宽越宽,相位越低,因此需进行设计权衡。增益裕量(GM)是指Fsw/2和–180°处的负增益,-8 dB或更高的值将能很好地衰减可能的开关噪声,或减小相移-180°时的增益可能性。我们希望以-20 dB/Dec的斜率穿过0 dB点。

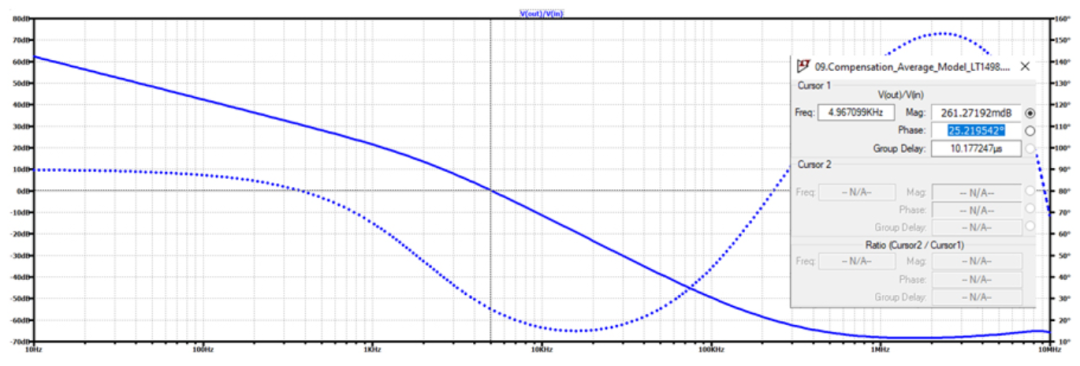

图1.波特图,显示了带宽、相位、

增益裕量和0 dB时的交越频率Fc

图2.电源带宽越宽,

器件对电流负载变化的响应越快

功率级LC滤波器

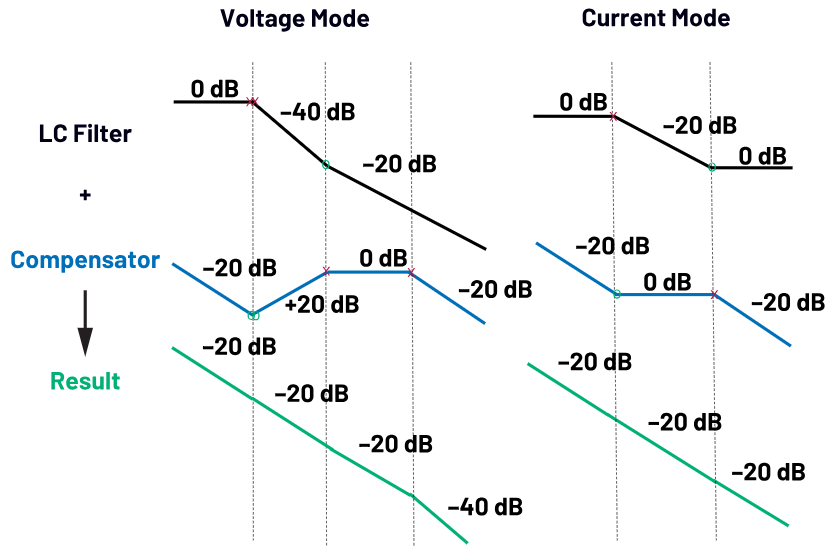

功率级LC滤波器是指给定拓扑(降压、升压等)的电感和等效输出电容。各种拓扑常用的架构有两种:电压模式(VM)和电流模式(CM)。VM架构和CM架构中的同一LC滤波器会产生不同行为。简单说来,用于VM架构的LC滤波器会增加两个极点。CM架构额外包含一个电流检测反馈路径,有助于消除LC滤波器的双极点。VM架构则难以做出补偿,因为LC双极点需要更多的零点来抵消双极点效应,因此需要更多元件。

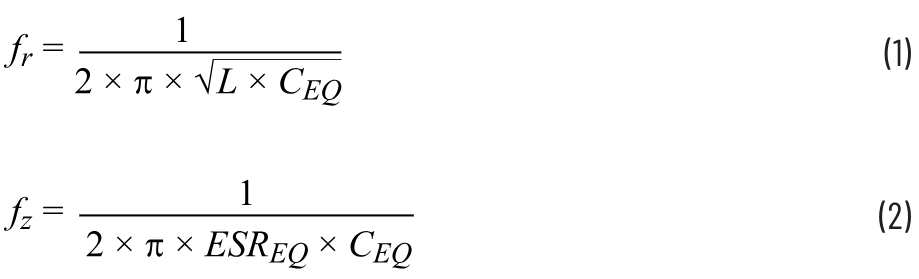

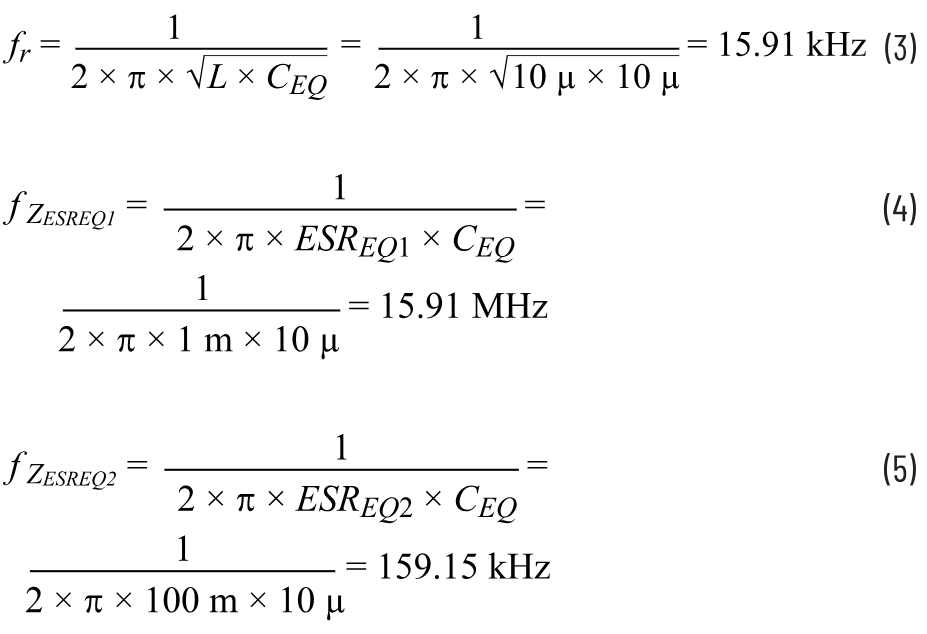

降压VM架构和LC频率行为由于等效输出电容CEQ及其等效ESR (ESREQ),LC滤波器将导致增加两个极点和一个零点:

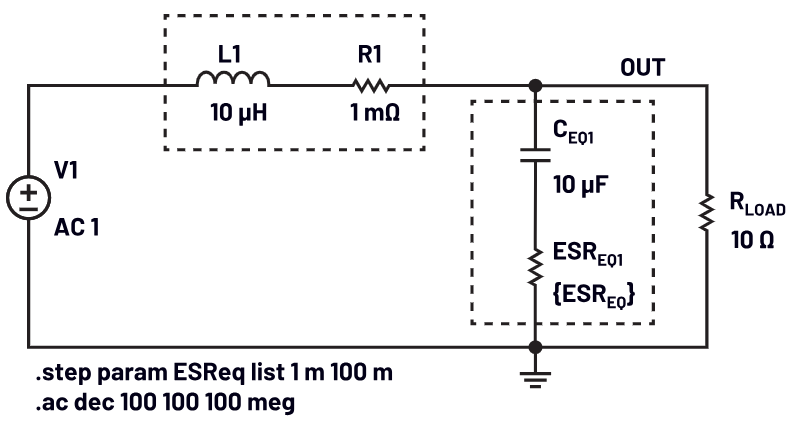

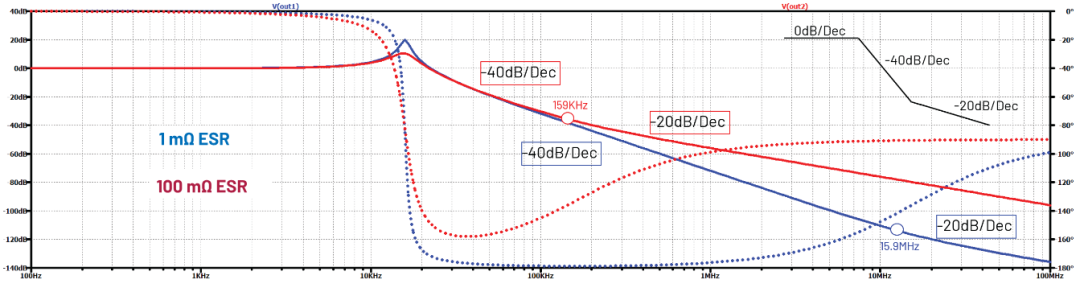

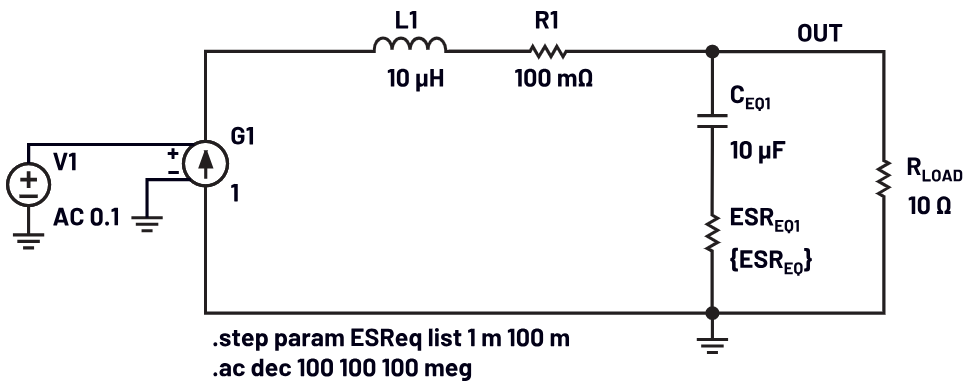

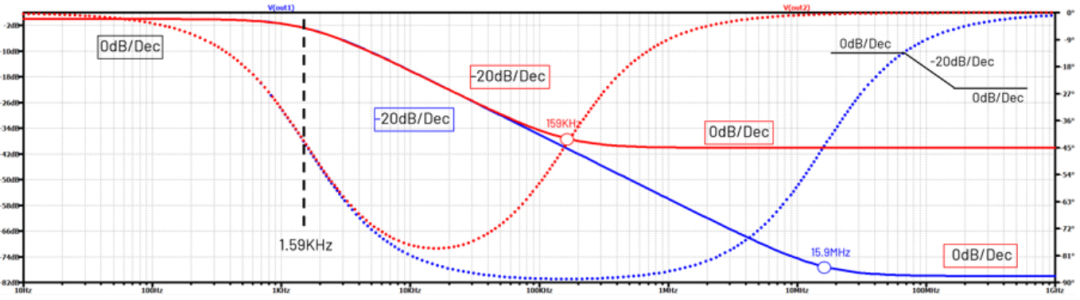

LC滤波器双极点位置与LC寄生电阻无关。电感和等效电容值越大,双极点位置就会越靠近频率轴的原点0 Hz。如果CEQ及其ESREQ值较高,则LC滤波器零点频率位置将向左移动或更接近0 Hz。VM中的LC滤波器行为如图3所示,其仿真结果如图4所示。红线和蓝线之间的差异是电容ESR值造成的,分别为1 mΩ和100 mΩ。Fr位置相同,因为LC值没有改变,但零点位置因ESR值的改变而变化。

图3.VM降压LC滤波器行为的简化模型电路对于VM架构,LC滤波器会增加两个极点和一个零点。频率响应形状始终相同:斜率变化为0 dB/Dec至-40 dB/Dec至-20 dB/Dec。极点和零点的位置取决于电感、总电容和等效电容ESR值。

图3.VM降压LC滤波器行为的简化模型电路对于VM架构,LC滤波器会增加两个极点和一个零点。频率响应形状始终相同:斜率变化为0 dB/Dec至-40 dB/Dec至-20 dB/Dec。极点和零点的位置取决于电感、总电容和等效电容ESR值。

图4.简化VM降压LC滤波器行为的仿真结果

图4.简化VM降压LC滤波器行为的仿真结果

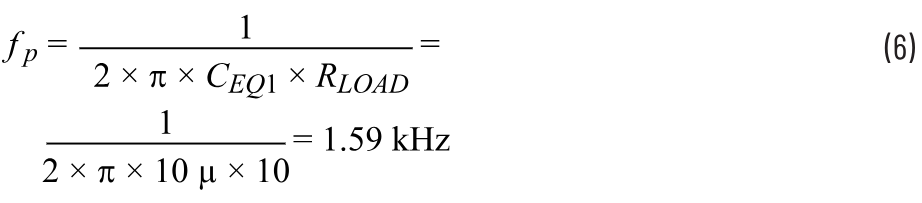

CM架构和LC频率行为可以通过电压控制电流源来仿真CM中LC滤波器的频率行为,如图5所示。ESR在两个数值间步进,以凸显零点位置的差异。由下式计算得出CM降压架构中LC滤波器的极点位置:

RLOAD为负载电阻,即输出电压与电流的比值。例如,若输出电压为5 V,负载电流为2 A,则RLOAD将等于5 V/2 A = 2.5 Ω。零点位置由等效输出电容及其等效ESR决定。同VM架构类似,1 mΩ和100 mΩ ESR对应的两个零点值为:

图5.电压控制电流源用作CM降压的模型;

ESR为步进式

对于CM架构,LC滤波器会增加一个极点和一个零点。频率响应形状始终相同:斜率变化为0 dB/Dec至-20 dB/Dec至0 dB/Dec。极点/零点的频率位置取决于输出电容、等效ESR和负载值。

补偿器

LC滤波器会导致相位损失。补偿网络用于补偿相位,通过向环路添加极点和零点,可抵消LC滤波器引起的相位滞后/超前和增益变化。

图6.CM降压LC滤波器频率响应形状的仿真

图6.CM降压LC滤波器频率响应形状的仿真

电流模式架构补偿器

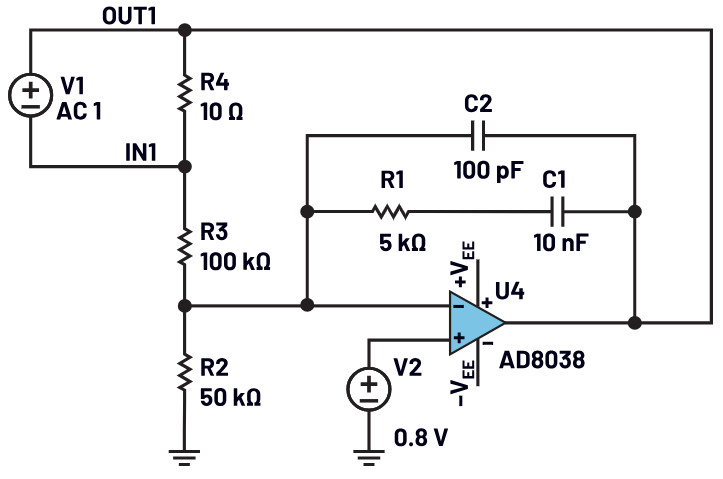

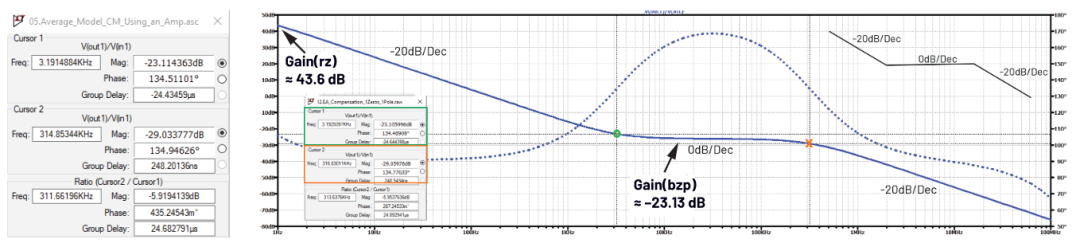

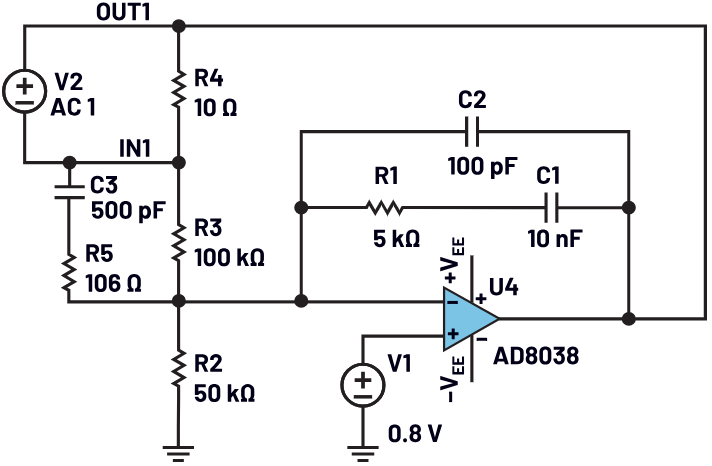

CM架构补偿器称为2型补偿器。图7所示为2型补偿器。AD8038为EA,R2、R3为反馈电阻,R4为电阻,V1通过R4将频率注入环路以执行FRA。补偿网络由R1、C1和C2组成。

图7.LTspice中的2型补偿器模型

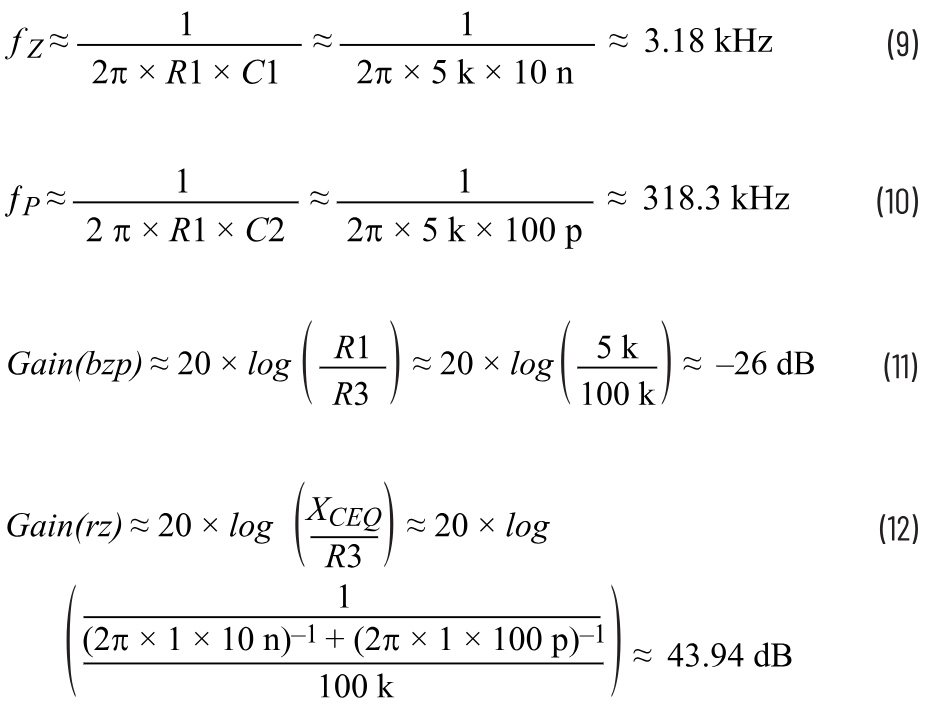

零点/极点和增益的预期结果:

Gain(bzp)为零点和极点之间的增益,由R1与R3的比值决定。Gain(rz)为直流增益。在上述计算过程中,原点处的极点使用1 Hz的频率;因此,补偿器的初始斜率为-20 dB/Dec。图8显示仿真结果与计算值密切相关。

图8.2型补偿器仿真结果、

图8.2型补偿器仿真结果、

极点/零点位置和斜率变化

VM架构补偿器VR

在VM架构中,补偿器有一个额外的极点/零点组合,可抵消LC滤波器的额外相位损失。图9显示了用于VM架构的3型补偿器网络,图10显示了其频率响应。

图9.VM架构补偿器,也称为3型补偿器

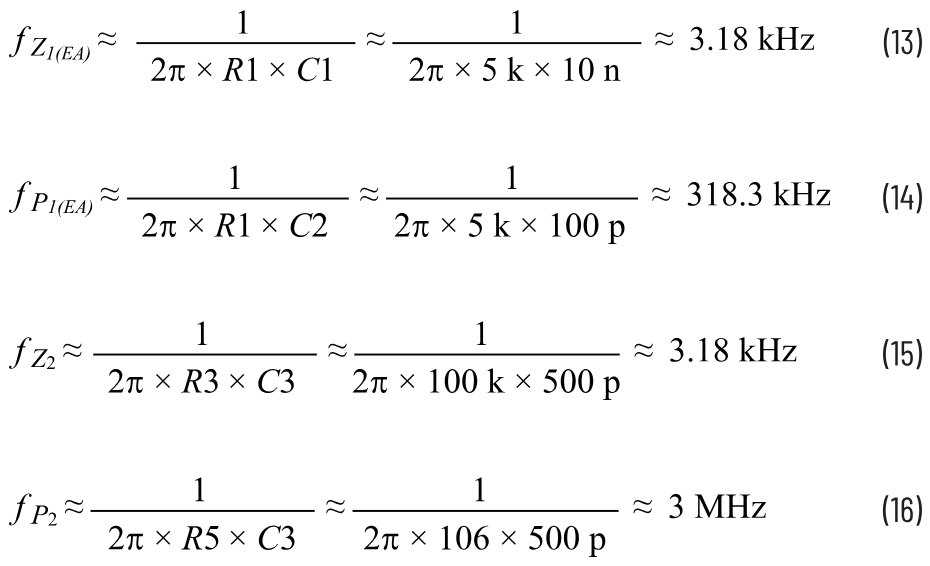

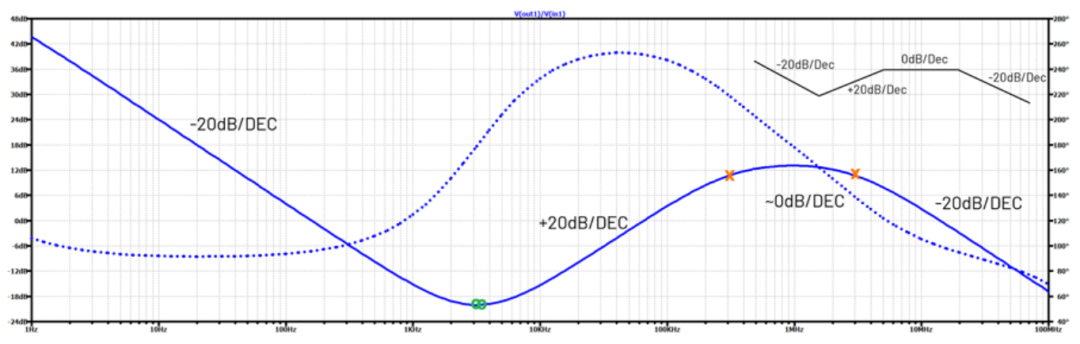

C3和R5是与顶部反馈电阻R3并联的两个附加元件。3型补偿器的极点和零点位置为:

请注意,Fz1(EA)和Fz2被置于同一频率。有时会使用类似3型的补偿方案,即在顶部反馈电阻上设计单个电容,以剔除高频极点,补偿器斜率将继续保持在0 dB。

图10.VM补偿器电路的LTspice交流仿真结果

图10.VM补偿器电路的LTspice交流仿真结果

调整时间常数一致

一种闭合环路的方法是让LC滤波器极点/零点的时间常数与补偿器零点/极点的时间常数一致,这样就可以实现相互抵消,并提供总计-20 dB/Dec的增益斜率。

图11.调整对齐VM和CM中LC滤波器

与补偿器的极点和零点

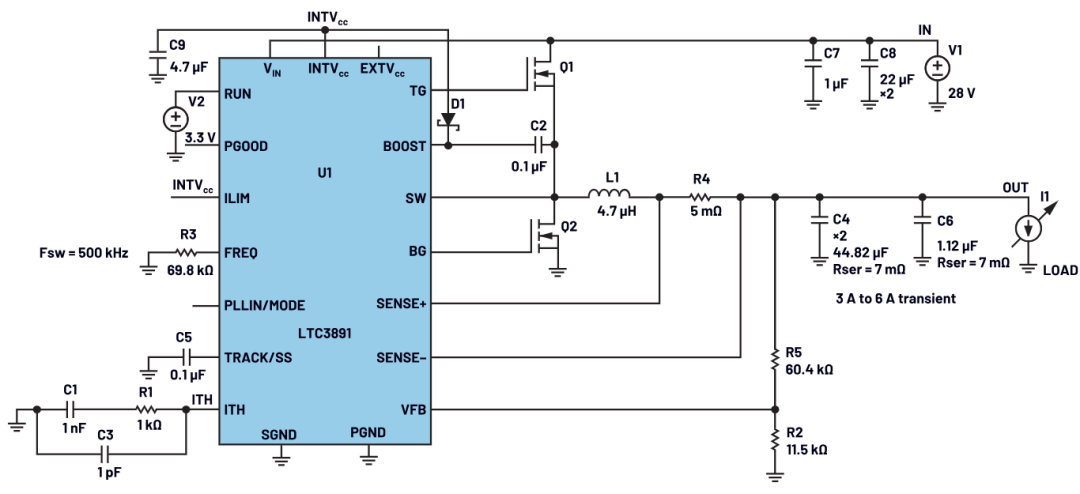

图12.LTC3981 28 V至5 V/6 A设计原理图,

图12.LTC3981 28 V至5 V/6 A设计原理图,

其中补偿网络未对齐

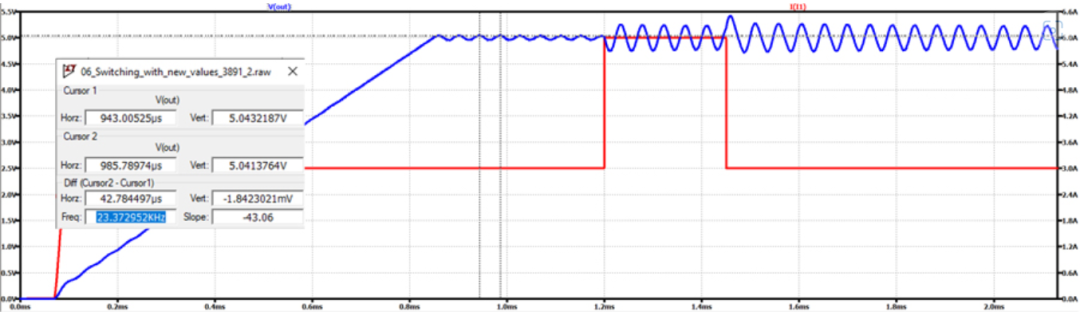

图13.补偿网络未对齐,开关频率与设计频率不同,

瞬态测试引起振荡

使用一阶平均模型对齐极点/零点

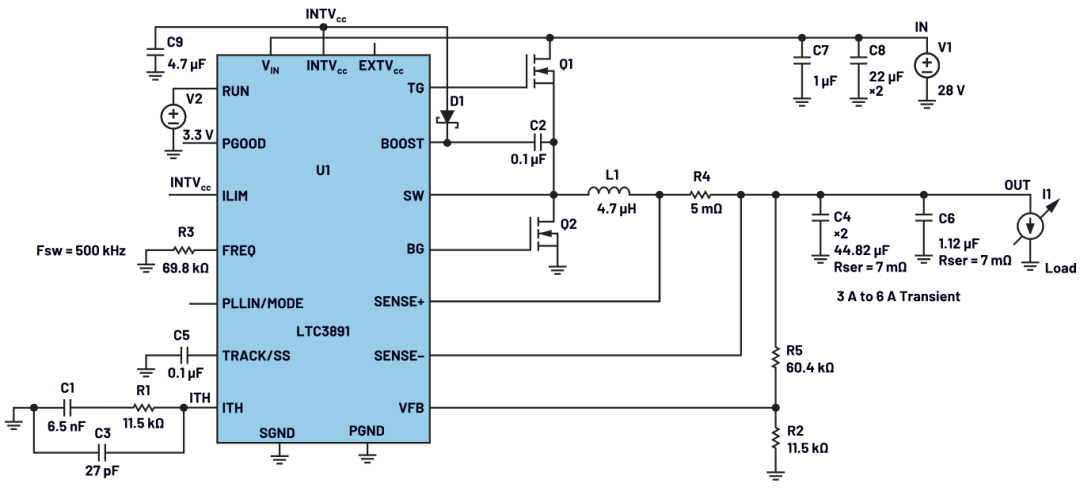

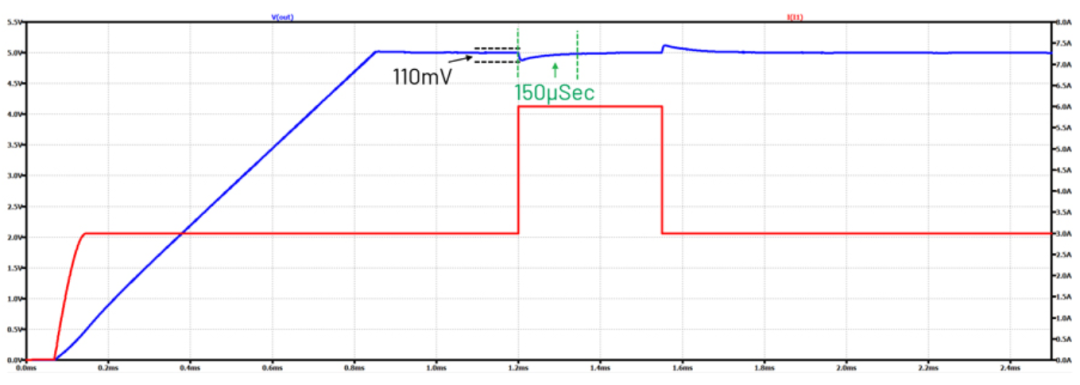

LTC3891是一款CM控制器,用于将28 V降压至5 V/6 A。ITH引脚上的补偿网络与等效输出电容及其总ESR不一致,导致在瞬态负载测试中出现振荡。输出端测得的开关频率为23 kHz,而不是预期的500 kHz。

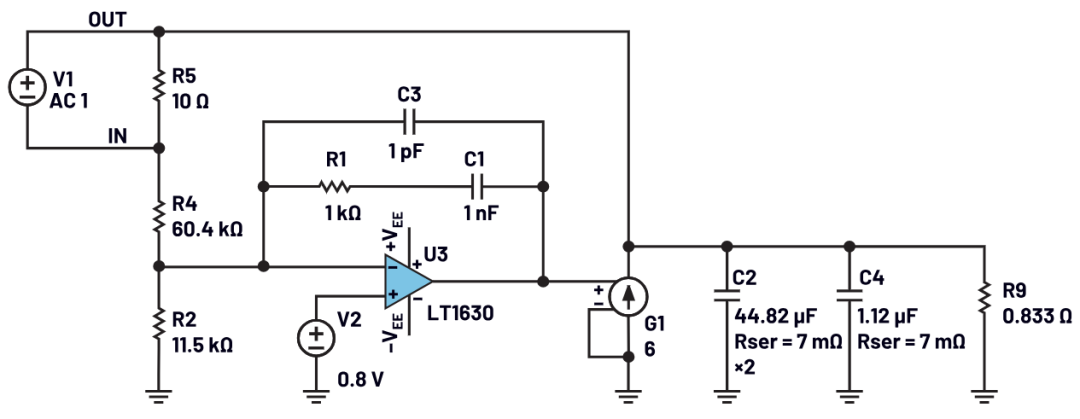

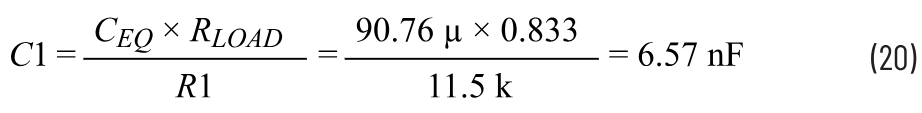

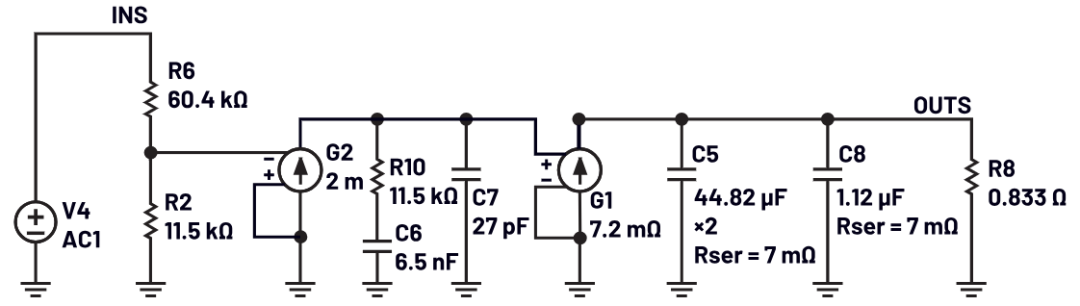

将功率级和补偿器这两个电路组合在一起,形成一个模拟CM架构闭环行为的线性电路。

图14.线性电路模拟CM稳压器,补偿网络未对齐

图14.线性电路模拟CM稳压器,补偿网络未对齐

图15.线性模型的仿真结果,

使用放大器作为误差放大器,常数不一致

G1是电压控制电流源。其值为6,意味着如果G1正输入端的电压为1 V,则其输出端将提供6 A电流。该电路的频率响在不同速率下显示不同的斜率变化,0 dB交越频率处的相位为25°。因此,时域中存在振荡。

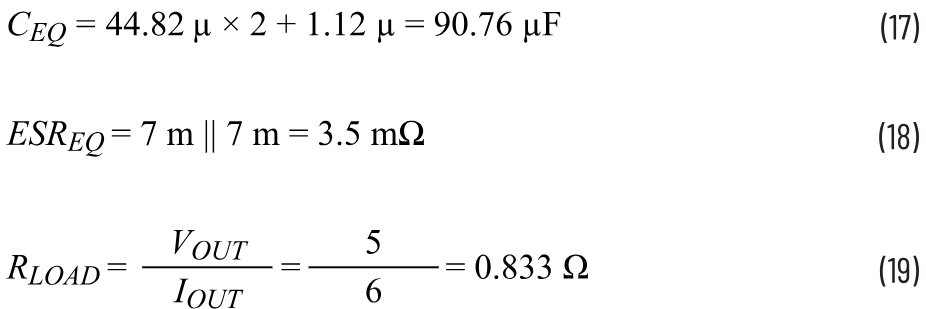

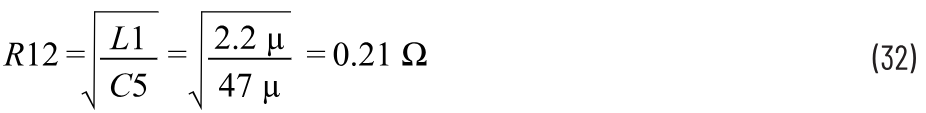

为使时间常数一致,我们首先需要知道功率级的CEQ、ESREQ和RLOAD。

R1由设计人员选择;这里选择R1 = 11.5 kΩ,与R3相同。R1 × C1(z) = CEQ× RLOAD(p)。求解C1:

图16.极点/零点调整对齐后,

使用放大器作为EA的线性模型

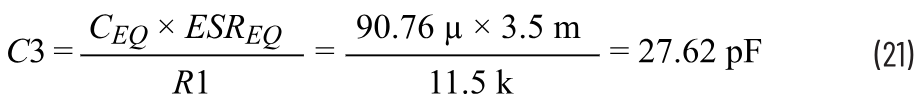

CEQ× ESREQ(Z) = R1 × C3 (P),补偿器极点的时间常数由R1 × C3决定。求解C3:

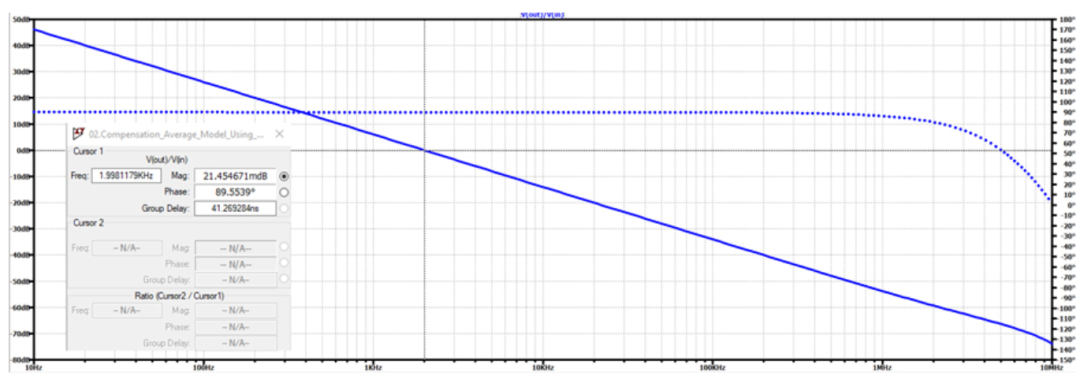

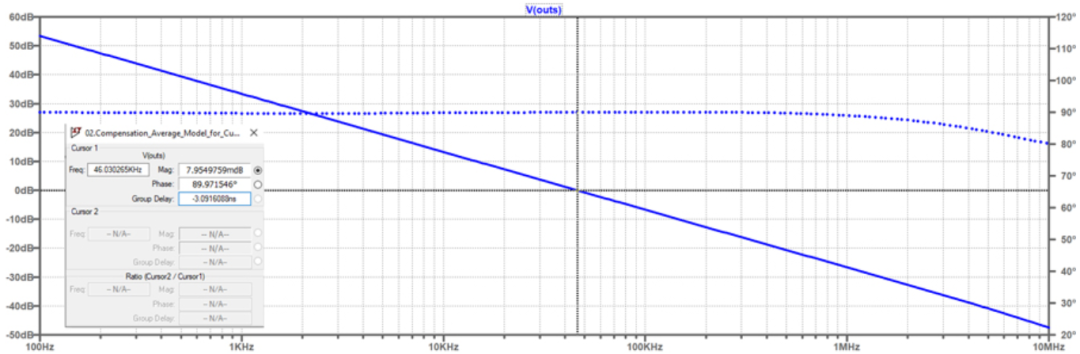

使用此平均模型时,正确仿真结果显示-20 dB/Dec的斜率和90°的相位。如果结果不同,则需要验证计算。

使用运算放大器作为EA的缺点之一在于无法正确预测带宽。尽管如此,此方法仍然非常实用,可帮助验证一致计算。可以通过增加R1电阻值来提高带宽。如果R1增加,则补偿器电容需要按相同比例减小,以保持时间常数一致。R1不可无限制地增加,因为增益越高,0 dB时的相位裕量越低。当时间常数一致时,相位将始终保持为90°。需要利用IC开关模型验证计算值,然后还需进行瞬态响应基准测试。

图17.极点/零点调整对齐后得到的结果,

斜率为-20 dB/Dec,90°高相位值

图18.ITH引脚上的补偿网络

与输出LC滤波器保持一致

图19.保持补偿网络和LC滤波器的相关数值一致后得到的仿真结果,显示了对负载瞬变的稳定响应

用另一个电压控制电流源替代运算放大器,可以简化该线性模型,并提升其准确率。LTC3891数据手册提供了跨导值,1.2 V下gm = 2 mmho。G1正输入为1 V,因此新的电流值将为7.2,因为7.2 A/1.2 V = 6 A/V。新电路(图20)的仿真如图21所示,预测带宽将为46 kHz。

图20.更为简单的对齐电路,使用了G2作为误差放大器,其相应的gm值取自数据手册

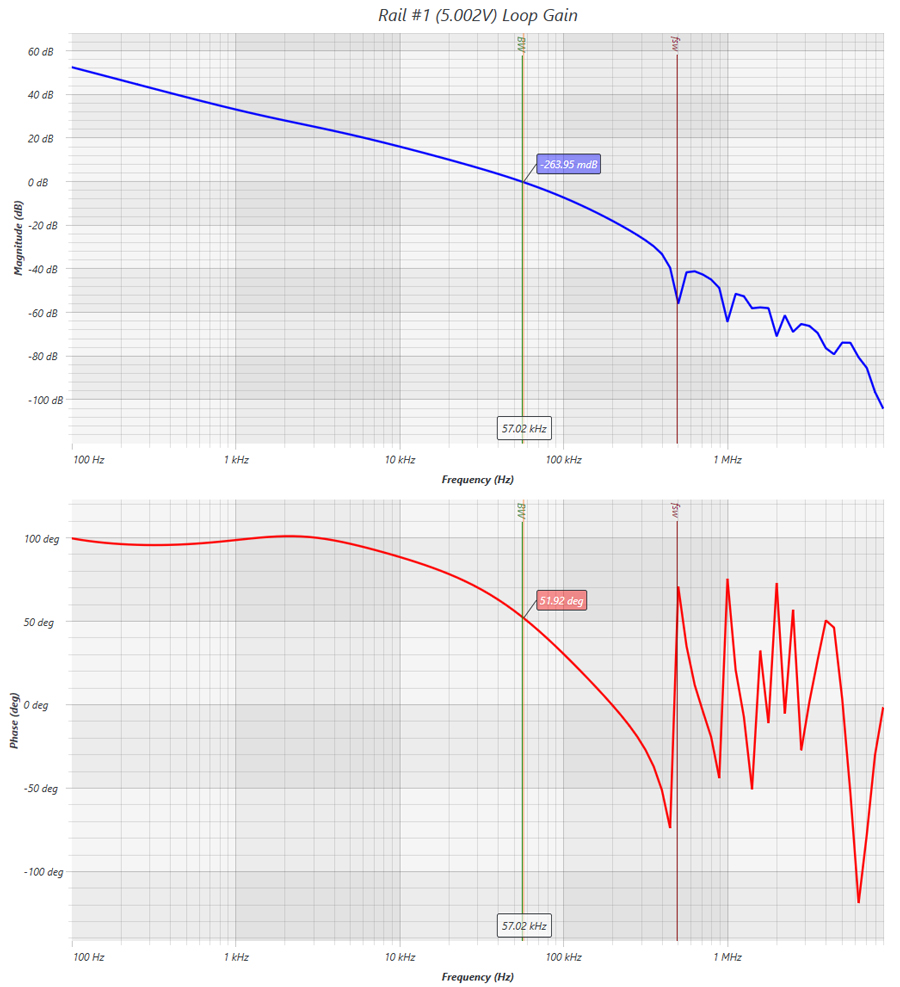

LTpowerCAD预测带宽为57 kHz,相位裕量为52°。增益图看起来非常相似。相位起初非常接近,但在10 kHz之后无法正确预测。

右半平面零点(RHPZ)

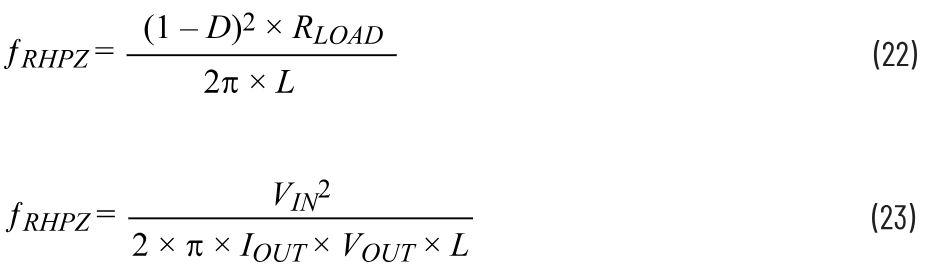

RHPZ零点会增加20 dB的增益,并使相位减小约90°,因此无法进行补偿。对于在连续导通模式下工作的升压、降压-升压和sepic等拓扑,这个零点会限制带宽。RHPZ的频率位置计算如下:

图21.使用G2作为EA的更简单电路模型可提供更宽的带宽

图21.使用G2作为EA的更简单电路模型可提供更宽的带宽

图22.图18中LTC3891设计的LTpowerCAD结果

图22.图18中LTC3891设计的LTpowerCAD结果

通常,在这些公式中,"电感"是需要由设计人员进行权衡取舍的唯一变量。RHPZ位置限制了设计的带宽,因为环路需要在F(RHPZ)/10的频率闭合。此处提供的线性模型电路未考虑RHPZ。

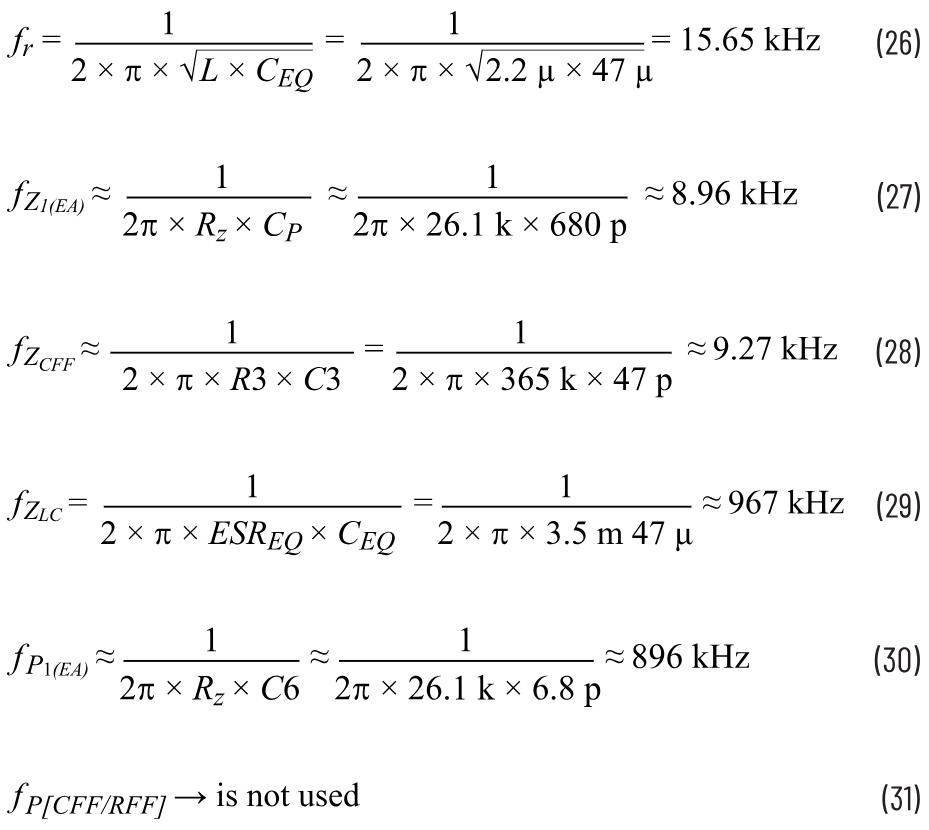

电压模式降压-升压示例

LTC3533是一款VM架构降压-升压型稳压器。在升压模式下,其RHPZ将成为限制因素。当输入为2.4 V的VIN(MIN)时,LTC3533演示板配置为3.3 V/1.5 A。在这种情况下,占空比D将为D = (Vo – VIN)/ Vo = (3.3 – 2.4)/3.3 ≈ 0.27。RLOAD = VOUT/IOUT = 3.3/1.5 = 2.2 Ω。

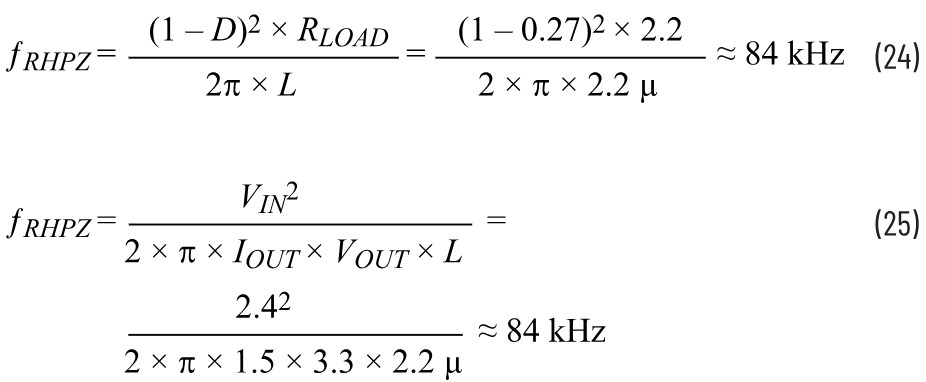

RHPZ位置可以通过以下任一公式求得:

闭合环路的安全位置将是在8.4 kHz。Rt设置开关频率Fsw = 1 MHz。请注意,由于缺少RFF,此补偿是类似3型的补偿,因此Cff不会产生额外的高频极点。

极点和零点的位置为:

LC滤波器的双极点位置在15.65 kHz。两个零点Fz1和FzCff集中在一起,频率约为9 kHz,以抵消LC滤波器的极点。此外,LC滤波器在967 kHz处形成的零点的影响被896 kHz处的极点抵消。

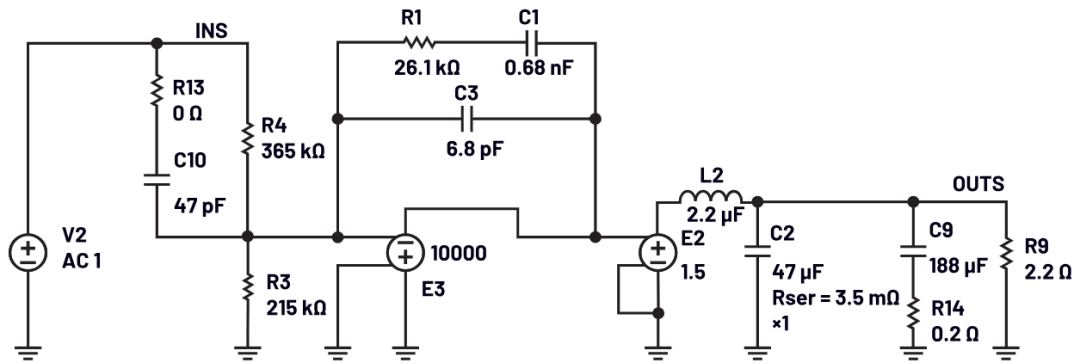

图23.LTC3533演示板原理图

图23.LTC3533演示板原理图

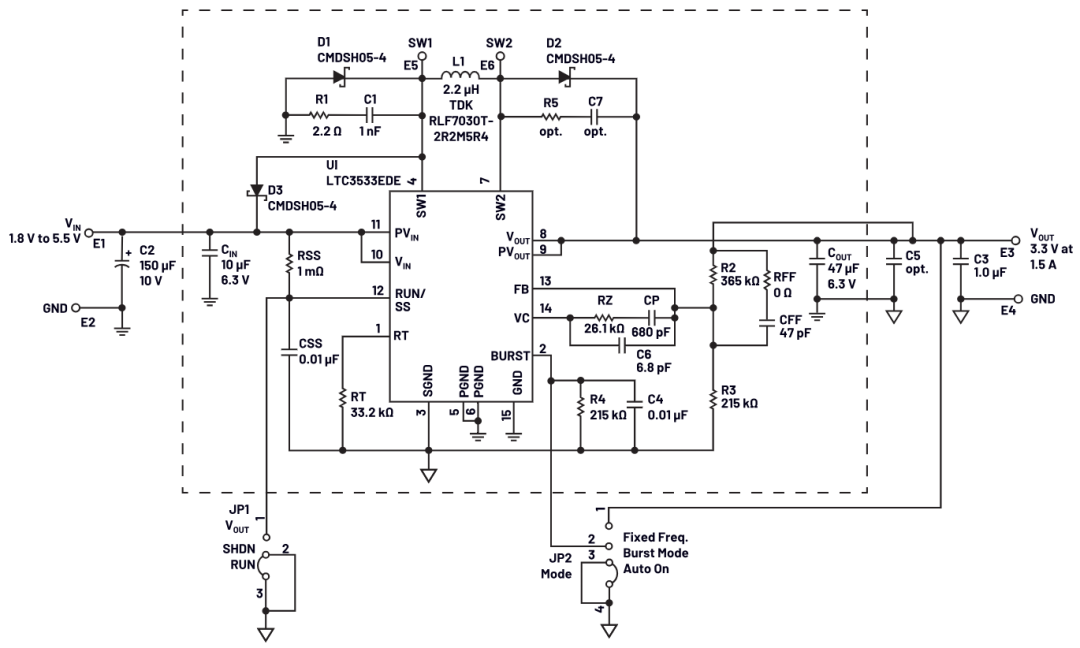

图24.使用运算放大器作为EA的VM架构的一阶模型;

图24.使用运算放大器作为EA的VM架构的一阶模型;

LTC3533演示板值

图25.使用电压控制电压源的VM控制的更简单电路

图25.使用电压控制电压源的VM控制的更简单电路

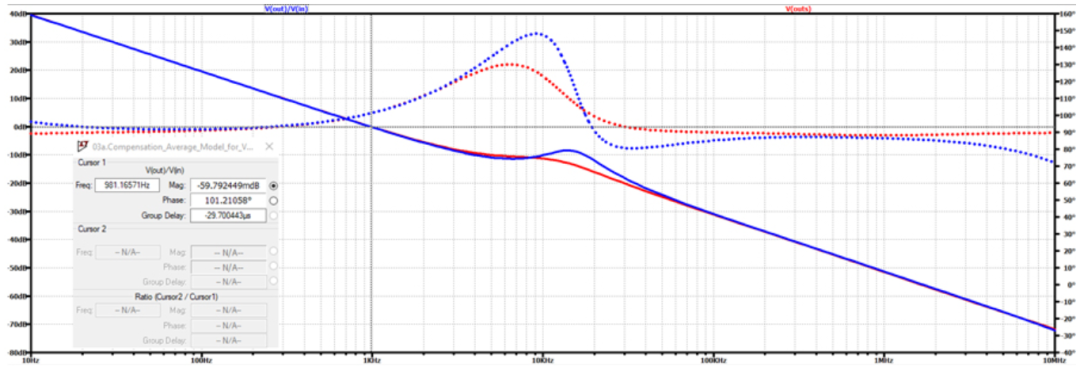

图26.两个电路的仿真结果

图26.两个电路的仿真结果

使用运算放大器作为EA的VM架构的平均LTspice电路,可用来检查极点和零点的对齐情况。通过将电压控制电压源用作EA,可以进一步简化电路。其增益值源自数据手册中指定的误差放大器AVOL,即80 dB。80 dB = 20log10000。因此在仿真中取用了10000。两种电路的仿真提供了非常相似的解决方案。带宽没有像CM电路仿真中那样变化。增益非常相似,相位预测值为90°,但这仅说明了可以进行正确对齐。输出端有一个188 μF附加电容和一个0.2 Ω电阻。如图4所示,电压模式LC滤波器可以产生高Q,尤其是当ESR和DCR的值较低时。为确保LC滤波器具有适当的阻尼,需在输出端额外添加一个RC,具体计算如下:

结论

LTspice电路仿真为验证补偿网络的计算提供了一种高效可靠的方法。虽然所讨论的线性模型不包括电流检测元件、信号增益或RHPZ信息,但仿真速度快和兼容各种DC-DC拓扑的优势将能让相关设计人员大受裨益。此外,如果获得的结果正确,输出将显示-20 dB/Dec的增益斜率和大约90°的相位。

原文转自亚德诺半导体

-

电路

+关注

关注

172文章

5915浏览量

172270 -

转换器

+关注

关注

27文章

8706浏览量

147199

发布评论请先 登录

相关推荐

DC-DC直流升压模块的选型

升降压电路-你会算DC-DC电感值吗?

DC-DC升压模块的工作原理

24v-100v DC-DC电源设计

DC-DC 和LDO 简单介绍

降压型DC-DC转换器与升压型DC-DC转换器的输出纹波差异

电子技术(十九)——DC-DC

DC-DC电路设计要点及计算全解析

DC-DC转换器电路图 Boost升压型DC-DC转换器的工作原理

DC-DC的PCB设计注意的点

【世说设计】ADI拍了拍你,并献上计算DC-DC补偿网络的分步过程教程

【世说设计】ADI拍了拍你,并献上计算DC-DC补偿网络的分步过程教程

评论