今年年初,美国硅谷举办了“首届年度芯粒设计峰会”。此次峰会的主题是:

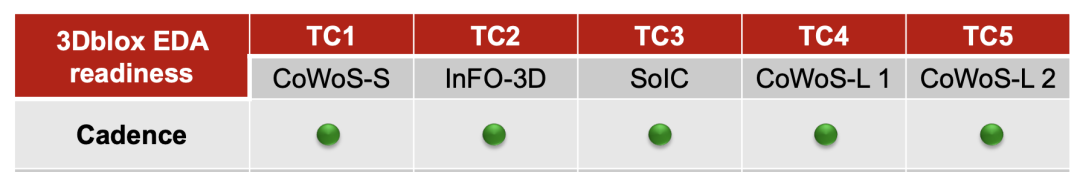

“摩尔定律”已经失效,我们剩下的只有封装。

在笔者之前的文章中提到过:

如今,来自一家公司的多芯粒设计正在大量出货,他们准备围绕芯粒组建自己的生态系统,而芯粒商店这种愿景目前还只是天方夜谭。

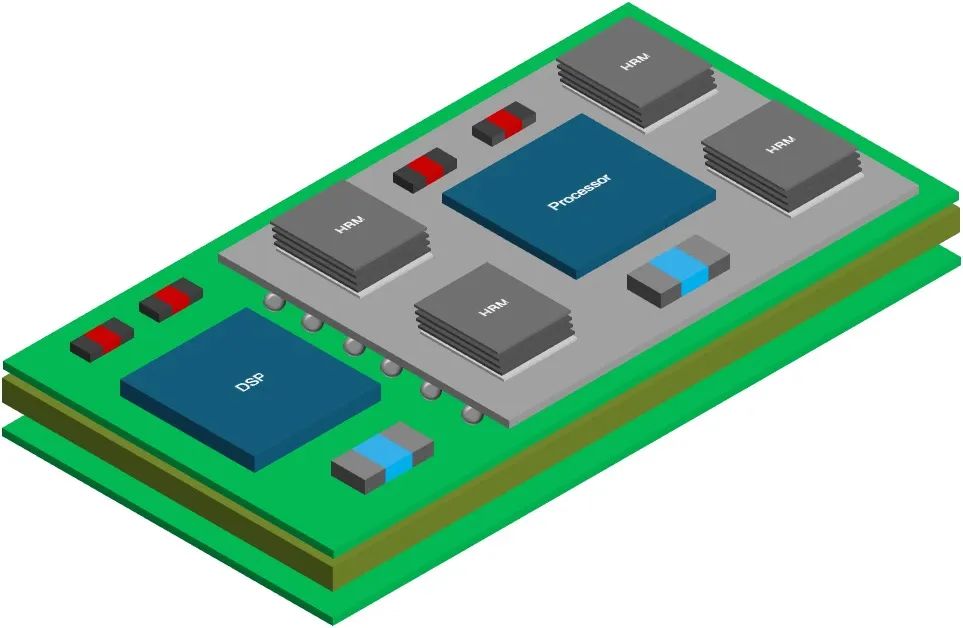

许多公司在制造芯粒时并未考虑到与其他公司的芯粒一同使用的情况,所以,要使用这些不同公司生产的芯粒进行基于芯粒的设计,必然需要解决一些技术问题。这类似于,我们从不同的制造商购买芯片,然后把它们放在一块 PCB 上,以构建一个可以运行的系统,但设计这些芯片的公司从未预想过此种使用场景。

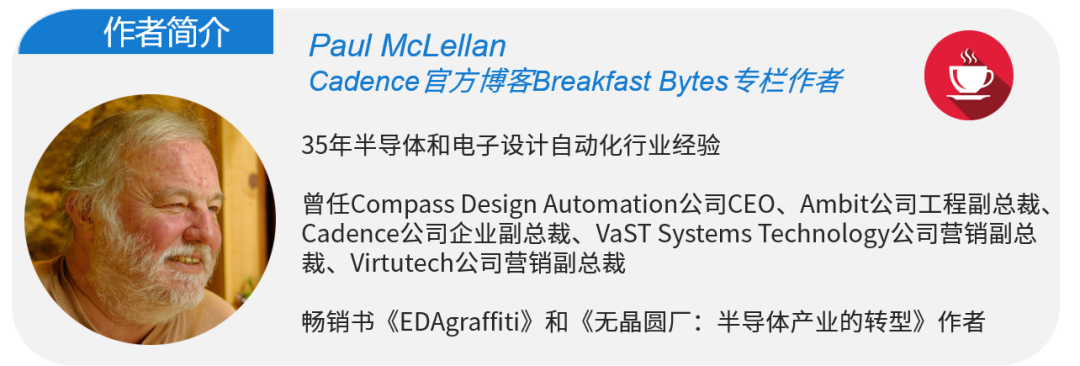

2.5D vs 3D

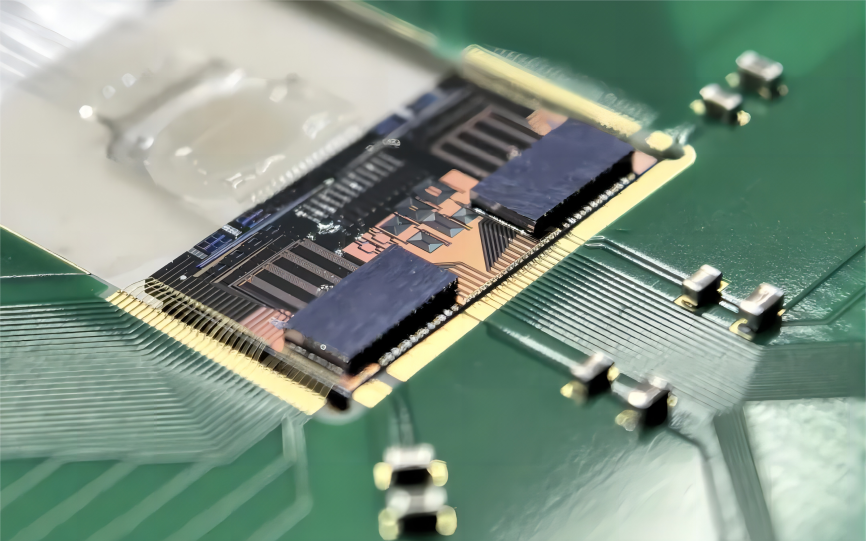

首先在此澄清,我们讨论的是将多个基于芯粒的设计整合到一个中介层上(硅中介层或有机中介层),而不是真正的 3D 设计,即多个裸片彼此堆叠。这种设计已经上市了(例如,索尼的图像传感器有一个包含逻辑、存储器和传感器本身的三裸片堆叠)。然而,堆叠多个裸片通常需要利用硅通孔 (through-silicon vias,TSV),所以需要非常仔细地设计芯片,以确保所有东西都能对齐。要将不同厂商生产的裸片堆叠成真正的 3D 设计,这个过程相当漫长。

目前,任何真正的 3D 裸片堆叠都是由一家公司设计的,将一个大型设计分割成多个裸片。而且除了对齐所有 TSV,还需要解决艰巨的散热挑战。

因此,在后文(以及可以预见的未来)中,我们所说的基于芯粒的设计都是指 2.5D 设计。

交换格式

如果要完成一个基于芯粒的设计,那么我们的设计工具需要具备相应的功能来读取描述芯片的重要信息。目前,有两项重要的标准化工作。

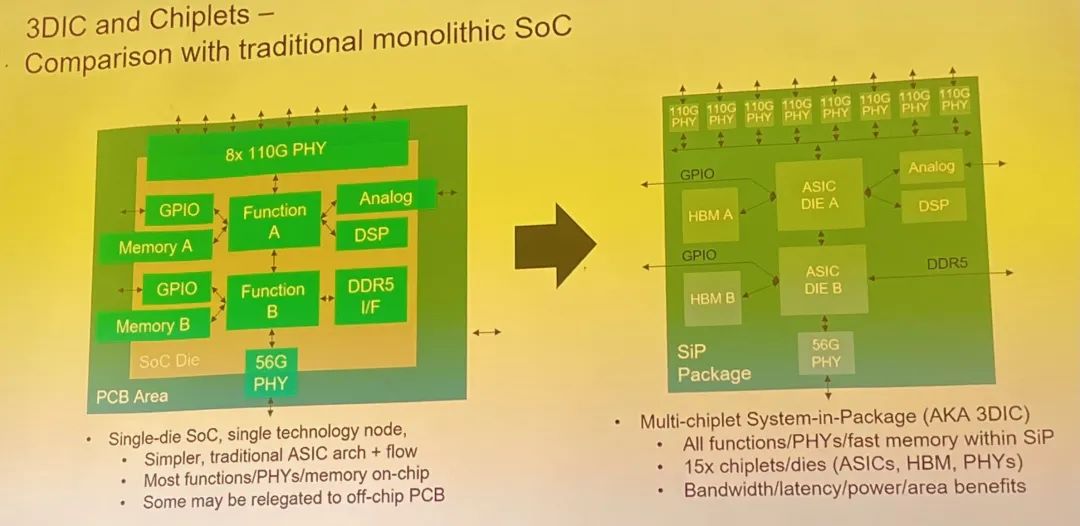

首先,台积电在去年 10 月的 OIP 上宣布推出 3Dblox,3Dblox 是一个开放的标准:

3Dblox 提供了能够代表当前和未来所有 3D-IC 结构的通用语言结构

将 3D-IC 结构模块化,从而使 EDA 工具和设计流程更加简单和高效

确保标准化的 EDA 工具和设计流程符合台积电 3DFabric 技术

3Dblox不是本文重点,Cadence 的工具组合支持 3Dblox(上表中的所有绿点)。

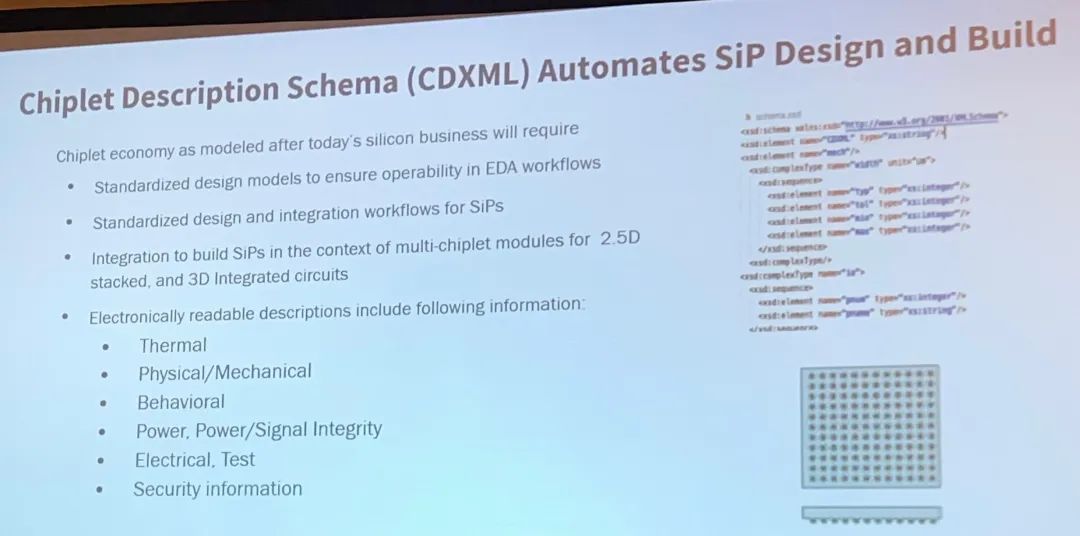

另一个标准是 CDXML,即“Chip Data Exchange Markup Language,芯片数据交换标记语言”。该标准由 OCP(开放计算项目基金会)开发。在芯粒峰会的第一天,JEDEC 和 OCP 就宣布正在合作制定这一标准,并将被纳入 JEP30,即 JEDEC 的零件模型指南。

那么,至少现在我们有两个开放标准:3Dblog 和 CDXML。

通信标准

存在两个可行的通信标准:一个是 Bundle-of-Wires (BoW),目前用于正在进行的设计;另一个是 UCIe (Universal Chiplet Interconnect Express),其 IP 即将上市。然而,尽管有英特尔、AMD、Arm、谷歌、Meta、高通等公司的背书,且 UCIe 有望成为终极标准,峰会的参与者依然认为 UCIe 标准“尚未完全准备就绪”。

已知良好裸片

将多个芯粒封装到一个封装中与只使用单个裸片并不相同。如果使用单个裸片,就要在封装成本和晶圆测试成本之间做出权衡。测试器较为昂贵,因此在晶圆划片前耗费太多精力进行裸片测试比较浪费成本。当然,封装也需要成本,所以也不能浪费太多封装。但如果因为裸片质量不佳而浪费了一个封装,那么并不算浪费了裸片,因为它已经报废了。

如果一个封装内有多个裸片,那么成本计算方式将完全不同。如果在晶圆测试中遗漏了一个不良裸片,那么当它与所有其他裸片一起封装时,则不仅仅是浪费了一个不良裸片(以及封装的成本),也浪费了这个封装中所有质量良好的裸片。另外,多个芯粒的封装成本比单个芯粒要高得多。因此,很有必要在进入组装阶段之前,对每个裸片进行全面测试。这些裸片称为 KGD(Known Good Die),即已知良好裸片。

可以采用一些措施来优化封装过程,例如在只置入部分裸片的情况下测试一个封装。如此一来,可以先置入成本低廉的裸片,然后进行测试,最后再置入昂贵的裸片(如最先进节点的 CPU 或 GPU)。这样可以避免由于某个非常便宜的元件发生故障而导致某个昂贵的元件也被迫报废。

测试

多芯粒设计(甚至是真正的 3D 设计)测试遵循 IEEE 1838-2019 标准,即 IEEE 三维堆叠集成电路测试引入架构标准。

安全性

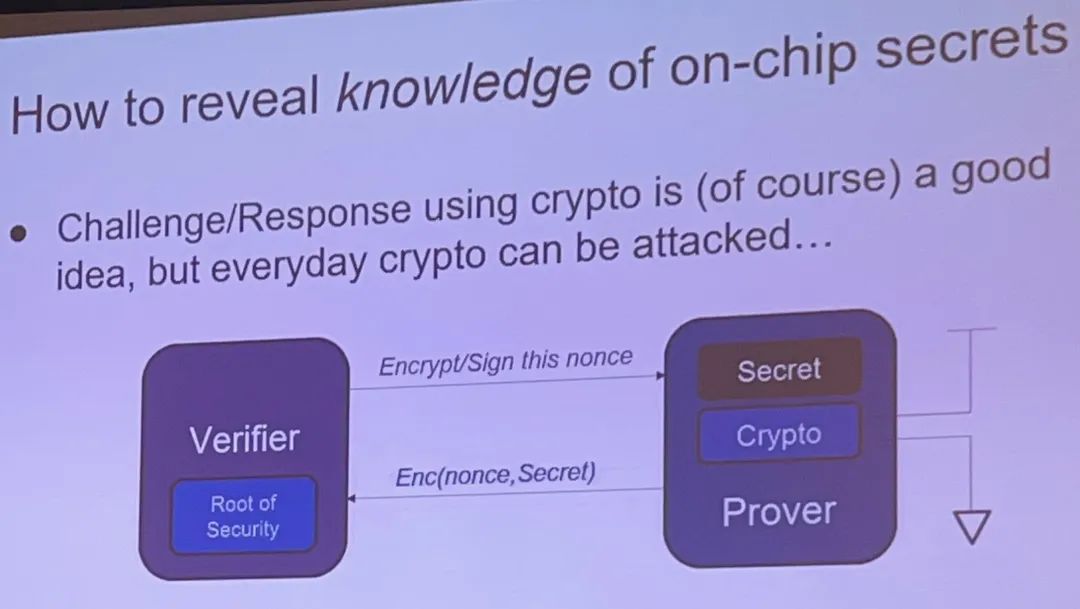

安全方面有很多问题。目前处理安全问题的方式是使用硬件信任根。对于一个基于芯粒的系统,首先需要确定是否信任所有的芯粒,或者判断从陌生供应商那里获得的一个或多个芯粒是否有可能遭到破坏。另外,还需要决定是否用一个芯粒确保安全性(包含有密钥的安全飞地等),然后验证所有其他芯粒是否安全。如果很多芯粒都包含需要启动的微处理器,那么可以集中处理,或者,每个芯粒必须处理自身的安全启动。

正如 Rambus Security 的 Scott Best 所指出的那样,5nm 的安全性设计非常复杂,几乎不可能实现,更不用说反向工程了。但基于芯粒的安全性设计则比较容易。

当我们把设计分解成芯粒时,SiP 就相当于安全性最低的芯粒。

更糟糕的是,虽然在一个 5nm 的芯片上监控大量的内部信号几乎无法实现,但在一个多芯粒设计中监控中介层上的信号却简单得多。在实践中,这意味着需要对任何与安全有关的芯粒之间的通信进行加密。当然,这些芯粒的设计初衷并不涉及到彼此协作,因此加密并不简单。处理这个问题的方法通常是使用某种形式的“挑战-回应”模式,但这种模式需要植入到每个芯粒中。在实践中,需要为芯粒制定某种安全标准。

另外还有一些非主流的方法,如差分功率分析 (Differential Power Analysis,DPA)。

故障排查

如果出现故障该怎么办?使用者可能不了解自己购买的所有芯粒的全部内部细节,该如何确定哪个芯粒是罪魁祸首?

有些人认为这是一个大问题,但其实这就类似于确定哪个 IP 模块引起了 SoC 故障,甚至与确定电路板上哪个芯片引起了板级故障并无二致。一种方法是假设这种情况可能发生,并提供某种方法来启用和禁用系统的各个模块。在微处理器中,这被称为“chicken bits”。

特殊市场

峰会期间还有两个随机出现的话题。

超级计算机,即最高端的 HPC,几乎总是使用 COTS 部件,即“商业现成(commercial off-the-shelf)”部件,如英特尔/AMD CPU、英伟达 GPU、FPGA 等等。正如 Lawrence Berkeley Laboratory 的 John Shalf 所说:

我们无法承担从头开始自研芯片的成本。

所以对他来说,芯粒提供了一种机会——可以购买现成的芯粒(也许可以简称为 COTC),并将其紧密地集成到系统中。

其次是汽车。汽车行业对芯粒不太看好,因为汽车中与振动有关的机械问题都会引发可靠性问题;而且汽车的期望使用寿命是二十年。另一方面,自动驾驶将像其他技术一样受到***极限的限制,因此汽车行业可能会迎难而上,因为无论如何,他们最终都需要使用芯粒。Cadence 欧洲学术网络主管 Anton Klotz 在年初参加一个汽车会议时也听到了类似消息:

自动驾驶芯片的数量不足以证明成本的合理性。通过将不同供应商的芯粒集成在一个中介层上,有望降低总成本;

芯粒比印刷电路板更节能;因此这种集成将大有裨益,有助于增加电动汽车的续航能力,并提供更好的性能

-

芯片

+关注

关注

456文章

51157浏览量

426677 -

pcb

+关注

关注

4326文章

23159浏览量

399565 -

芯粒

+关注

关注

0文章

59浏览量

148

发布评论请先 登录

相关推荐

国内首款2Tb/s 3D集成硅光芯粒成功出样,华为、英伟达等巨头争相布局

Arm宣布其芯粒系统架构正式推出首个公开规范

Arm发布芯粒系统架构首个公开规范

今日看点丨Arm 发布芯粒系统架构首个公开规范;纳芯微推出车规级D类音频功率放大器

集成芯片与芯粒技术详解

Imec牵头启动汽车芯粒计划

强势入局芯粒技术链 东方晶源PanSys产品重磅发布

北极雄芯“启明 935”系列芯粒成功交付流片

芯德科技扬州晶圆级芯粒先进封装基地项目封顶

英特尔OCI芯粒在新兴AI基础设施中实现光学I/O(输入/输出)共封装

英特尔突破技术壁垒,推出全新硅光集成OCI芯粒

国信光电子创新中心发布首款2Tb/s硅光互连芯粒

为什么选择将AMBA CHI用于芯粒呢?

行业资讯 I 芯粒峰会:基于芯粒的设计面临哪些挑战

行业资讯 I 芯粒峰会:基于芯粒的设计面临哪些挑战

评论