随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC(Analog to DigitalConverter)、DAC(Digital toAnalog Converter)的指标都提出了很高的要求。 比如在雷达和卫星通信中,所需要的信号带宽已经达到了2GHz以上,而下一代的5G移动通信技术在使用毫米波频段时也可能会用到2GHz以上的信号带宽。 虽然有些场合(比如线性调频雷达)可能采用频段拼接的方式去实现高的带宽,但是毕竟拼接的方式比较复杂,而且对于通信或其它复杂调制信号的传输也有很多限制。

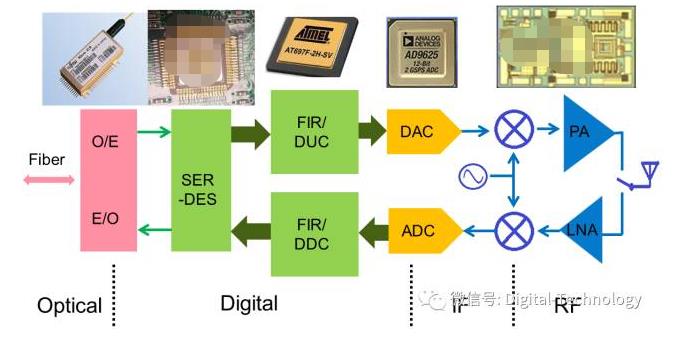

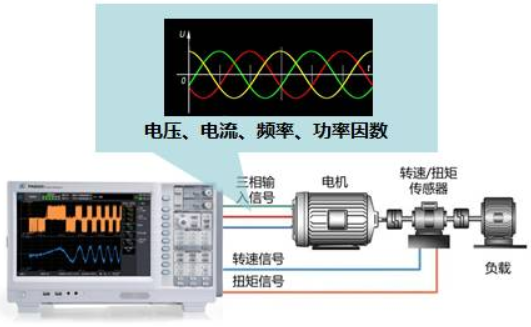

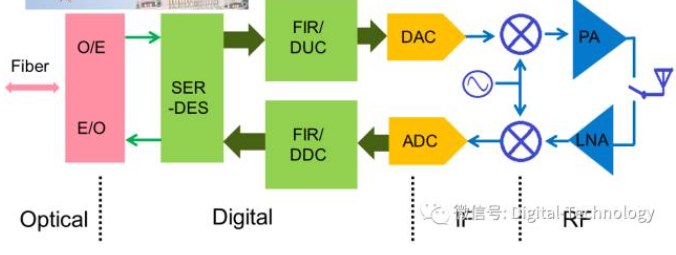

根据Nyquist采样定律,采样率至少要是信号带宽的2倍以上。同时为了支持灵活的制式、相控阵或大规模MIMO的波束赋形, 现代通信和雷达的收发机模块越来越普遍采用数字中频直接采样 ,这其实进一步提高了对于高速模数转换芯片的性能要求。下图是一个典型的全数字雷达收发信机模块的结构。

图****1 高速ADC/DAC在现代全数字雷达中的应用

可以看到,ADC/DAC芯片是模拟域和数字域的边界。一旦信号转换到数字域,所有的信号都可以通过软件算法进行处理和补偿,而且这个处理过程通常不会引起额外的噪声和信号失真。因此,把ADC/DAC芯片前移、实现全数字化处理是现代通信、雷达技术的发展趋势。

在全数字化的发展过程中,模数转换芯片需要采样或者输出越来越高的频率、越来越高带宽的信号。而在模拟到数字或者数字到模拟的转换过程中造成的噪声和信号失真通常是很难补偿的,并且会对系统性能造成重大影响。所以,高速模数转换芯片在采样或者进行模数转换时的性能对于系统指标至关重要。

目前在很多专用领域,使用的模数转换芯片的采样率可以达到非常高的程度。比如Fujitsu公司可以提供110G~130GHz的IP核,Keysight公司在高精度示波器里用到了单片40GHz采样率、10bit的ADC芯片,以及高带宽任意波发生器里用到了92GHz采样率、8bit的DAC芯片等。这些专用的超高速模数转换芯片通常用于特殊应用,比如光通信或者高端仪表等,比较难以单独获得。

在商用领域,很多高速模数转换芯片的采样率也都已经达到了GHz以上,同时也可以提供12bit以上的分辨率。 比如TI公司的ADC12J4000是4GHz采样率、12bit分辨率的高速ADC芯片;而ADI公司的AD9129是5.6GHz采样率、14bit分辨率的高速DAC芯片。这一方面要求ADC有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。

目前国内对于高速ADC/DAC的技术发展非常重视,很多国内研究所和大学都在开展相关课题的研究。 在面向新一代宽带无线移动通信网的国家科技重大专项中,也明确提出了把分辨率不低于12比特,采样率不低于3Gsps的基站所需的大宽带、高动态范围ADC/DAC芯片做为关键的核心技术之一。因此,如何对如此高带宽、高采样率、高分辨率和大动态范围的ADC/DAC芯片进行有效地测试,验证其在高速采样情况下的性能指标是一个很关键的问题。

二、高速ADC性能测试原理

**对于高速的ADC芯片(>100MHz)测试来说,其主要指标分为静态指标和动态指标2大类。**静态指标主要有:

• Differential Non-Linearity (DNL)

• Integral Non-Linearity (INL)

• Offset Error

• Full Scale Gain Error

动态指标主要有:

• Total harmonic distortion (THD)

• Signal-to-noise plusdistortion (SINAD)

• Effective Number of Bits (ENOB)

• Signal-to-noise ratio (SNR)

• Spurious free dynamic range (SFDR)

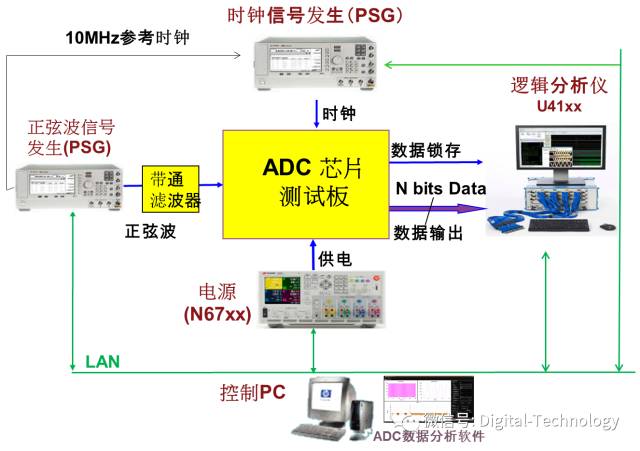

要进行ADC这些众多指标的验证,可用的方法很多。 最常用的方法是给ADC的输入端提供一个理想的正弦波信号,然后对ADC对这个信号采样后的数据进行采集和分析。 因此,ADC的性能测试需要多台仪器的配合并用软件对测试结果进行分析。下图是最常用的进行ADC性能测试的方法。

图****4 高速ADC测试方法

在测试过程中,第1个信号发生器用于产生正弦波被测信号,第2个信号发生器用于产生采样时钟,采样后的数字信号经FFT处理进行频谱分析和计算得到动态指标,经过直方图统计得到静态指标。

图****5 通过直方图测试静态参数

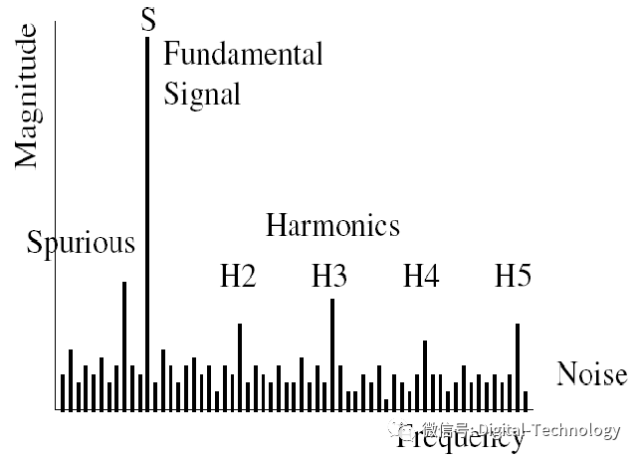

动态指标通常是对正弦波的采样数据进行FFT频谱分析,然后计算频域的失真间接得到。 一个理想的正弦波经A/D采样,再做后频谱分析可能会变成如下图的形状。除了主信号以外,由于ADC芯片的噪声和失真,在频谱上还额外产生了很多噪声、谐波和杂散,通过对这些分量的运算,可以得到ADC的动态参数。

图****6 通过FFT频谱分析测试动态参数

三、高速ADC性能测试系统

通过前面介绍可以知道, 要进行高速ADC芯片的性能验证,需要两台足够纯净的信号发生器分别产生正弦波输入和采样时钟,另外需要有数字采集设备同步采集ADC的数字输出,最后用软件进行后分析数据处理。 下图是一个典型可以支持到2.5GHz采样率、14bit分辨率ADC的测试系统。

图****7 2.5GHz采样率、14bit以内ADC的测试系统

如图所示,测试中使用微波信号源产生高精度、高纯净度的正弦波信号送给被测的ADC做为基准信号,ADC会在采样时钟的控制下对这个正弦波进行采样,变换后的结果用逻辑分析仪采集下来。各测试设备的主要功能和要求如下:

· PSG是非常纯净的模拟源,其相噪特性非常优异,其在产生2.5GHz频率信号时的抖动约为23fs RMS,因此可以产生非常纯净的正弦波和采样时钟。对于高精度ADC的测试来说,测试中信号源产生的信号还需要用带通滤波器进一步滤去谐波和杂散信号,滤波器的中心频点等参数要根据用户实际使用的测试频率组合选择。

· 由于ADC的模拟部分对于数字噪声非常敏感,因此ADC的供电要模拟和数字部分分开,PCB板上还要对模拟部分电源做充分滤波。测试中采用高质量的N6700系统提供多路电源供电,其电源的噪声<0.5mVRMS。另外,如有需要,N6700还可以模拟电源的波动或者异常以检验对于ADC性能的影响。

· ADC转换后的结果要通过逻辑分析仪采集下来,逻辑分析仪工作在状态采样模式,需要使用的通道数取决于ADC的位数,状态采样率取决于ADC的采样率,存储深度取决于采样率和FFT分析的频率以及直方图统计需要的数据量。U4164逻辑分析仪可以支持单边沿到2.5Gbps或者双边沿到4Gbps的状态采样速率,以及到每通道200M点的存储深度。

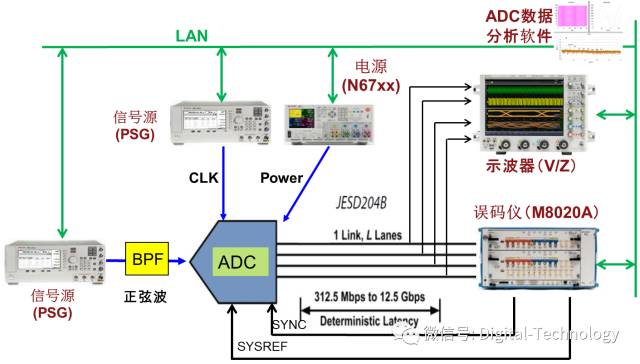

对于采用了JESD204B接口的ADC芯片来说,其数字接口的输出不再是并行接口,而是高速的串行接口,接口速率可达12.5Gbps甚至更高。 对于这么高速的串行数据捕获,可以采用高速的多通道的M8020A误码仪的接收端做为接收设备,误码仪需要具备至少4个通道,同时每个通道都要内置相应的信号均衡和独立的时钟恢复能力才能正常恢复数据。M8020A误码仪除了能用于数据捕获以外,还能够模拟出实际信号的速率、预加重、抖动、噪声等用于JESD204B接口的DAC芯片的测试。

图****8 JESD204B接口的高速ADC测试系统

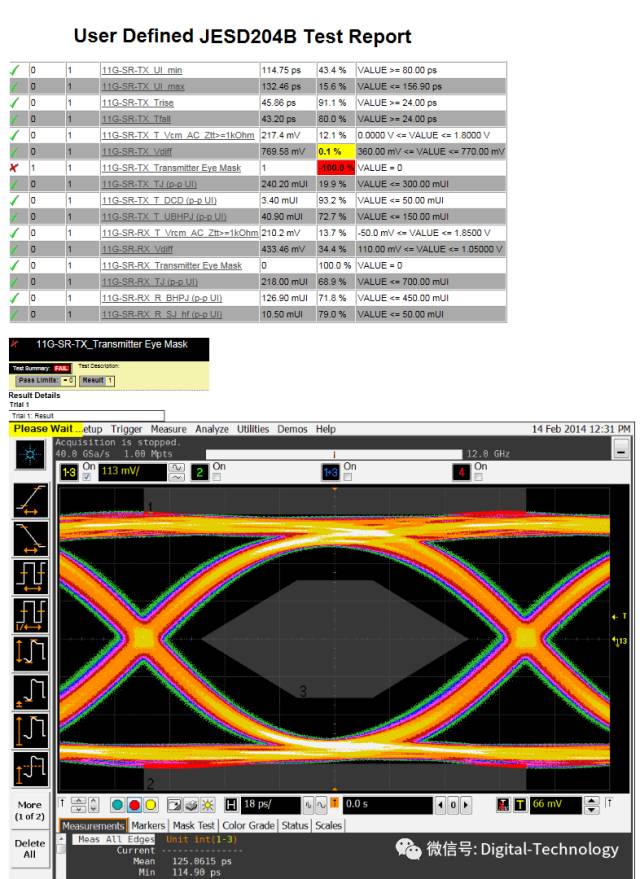

对于JESD204B接口的芯片,除了捕获数据进行ADC的性能分析,高速数字接口本身的信号质量验证也非常重要。 JESD204B接口的电气层面参考的是OIF组织的CEI(Common Electrical Interfaces)规范,目前最高速率为12.5Gbps,但也不排除未来提高到25Gbps的可能性。对于发送端信号质量的测试,主要是用宽带示波器捕获其发出的信号,并验证其信号质量满足规范要求。按照目前目前规范中的要求,12.5Gbps信号的最快上升时间在24ps,需要至少20GHz以上带宽的示波器来进行信号质量测试。同时,示波器里还要配合上相应的眼图、模板、时钟恢复、抖动分析等测试软件。下图是JESD204B信号质量测试报告的一部分。

图****9 JESD204B接口信号质量测试报告

根据不同的测试精度、频率、采样率需求,上述测试方案可能会有相应变化,也有可能会有不同的选件。测试中的ADC测试板、滤波器、时钟变换电路、电缆等附件需要另行设计或专门选购。

四、测试结果分析

ADC产生的测试数据被逻辑分析仪、FPGA板或者误码仪捕获下来后,需要送到测试软件进行性能分析。 测试结果可以通过相应的软件对ADC的采集结果进行分析,这个测试软件可以用户自己开发实现全自动测试,也可以手动控制仪器采集数据后用Matlab做后处理。

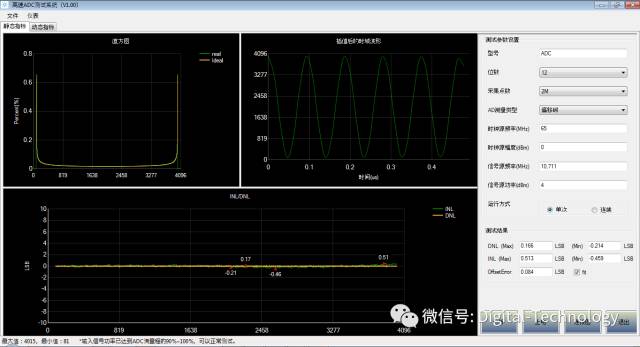

下图是静态参数的分析结果举例:

图****10 ADC静态参数测试结果举例

下图是一个ADC动态参数测量的结果举例:

图****11 ADC动态参数测试结果举例

五、高速DAC测试系统

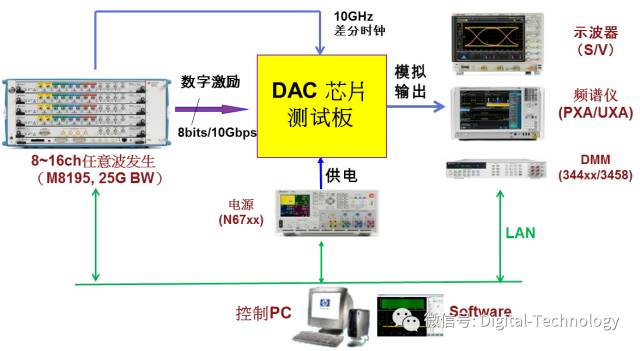

对于DAC来说,测试方法和ADC相反,是在输入端加数字激励信号,在模拟输出端测试其输出性能的指标。 下图是一个10GHz采样率、8bit DAC的测试系统。

图****12 10GHz采样率、8bit DAC的测试系统

系统主要测试参数:非线性、上升时间、SNR、SFDR、SND、ENOB参数测试。

测试中使用多通道、高带宽的任意波发生器产生采样时钟和多路数字激励信号,并行数据经DAC转换成模拟量后送给测试仪器做分析。 根据测试项目的不同,需要的测试仪器也不同。对于静态参数的测量用的是万用表,对于动态参数的测量用的是频谱仪。

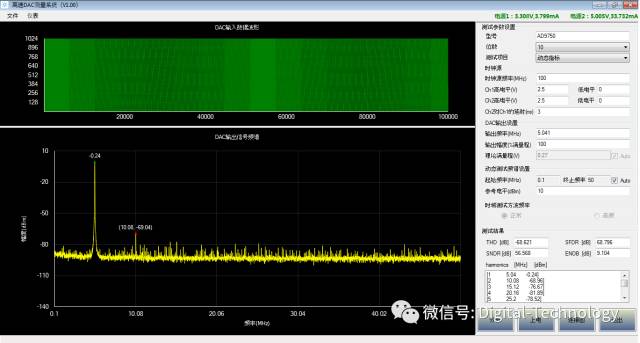

DAC产生的测试数据被捕获下来送到测试软件进行分析。测试结果可以通过相应的软件对DAC的采集结果进行分析,这个测试软件可以用户自己开发实现全自动测试,也可以手动控制仪器采集数据后用Matlab做后处理。下图是一个DAC动态参数测量的结果举例:

图****13 DAC动态参数测试结果举例

-

示波器

+关注

关注

113文章

7145浏览量

197024 -

adc

+关注

关注

100文章

7970浏览量

557295 -

dac

+关注

关注

44文章

2857浏览量

197737 -

信号发生器

+关注

关注

28文章

1738浏览量

113730 -

ADC转换器

+关注

关注

1文章

32浏览量

8698 -

MIMO技术

+关注

关注

0文章

44浏览量

7946

发布评论请先 登录

在高速和超高速运行情况下,高速变频电机的测试至关重要

基于FPGA的超高速FFT硬件实现

超高速环回设备测试应该选择哪个设备

用于3bit相位体制DRFM系统的单片超高速相位体制ADC设计与实现

安捷伦科技宣布发布USB 3.0超高速物理层一致性测试解决方

基于ADS的4GSps超高速ADC设计

微电子所在超高速ADC/DAC芯片研制方面取得突破性进展

基于LVDS的超高速ADC数据接收设计

讲一下超高速ADC/DAC的应用及测试

ADC12D1800 12位、单通道3.6 GSPS超高速ADC数据表

讲一下超高速ADC/DAC的应用及测试

讲一下超高速ADC/DAC的应用及测试

评论