今天我们要介绍的时序分析概念是 min pulse width ,全称为最小脉冲宽度检查。这也是一种非常重要的timing arc check,经常用在时序器件或者memory上面。

一般情况下,由于cell本身有变异,rise和fall delay不相同,这样可能会造成时钟信号脉冲宽度减小。

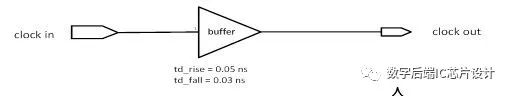

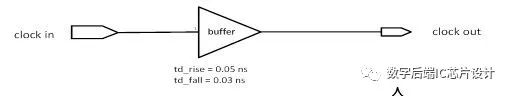

如下图一个周期为1ns,duty cycle 为50%的clock信号

在经过一个buffer(rise delay: 0.05, fall delay:0.03)

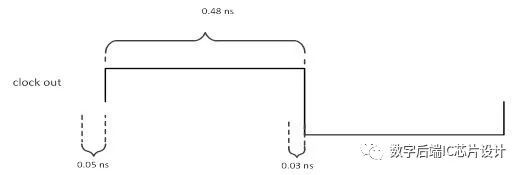

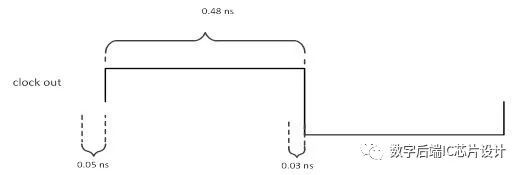

clock信号波形变成如下图所示:

因此,可以知道,如果某个cell的rise delay大于fall delay,那么输出时钟的脉冲宽度要比输入时钟小。如果时钟信号经过一系列相同类型的单元,则时钟信号的脉冲宽度将会持续减小。如果小于某个最小宽度,可能会导致器件不能正常的捕获数据。

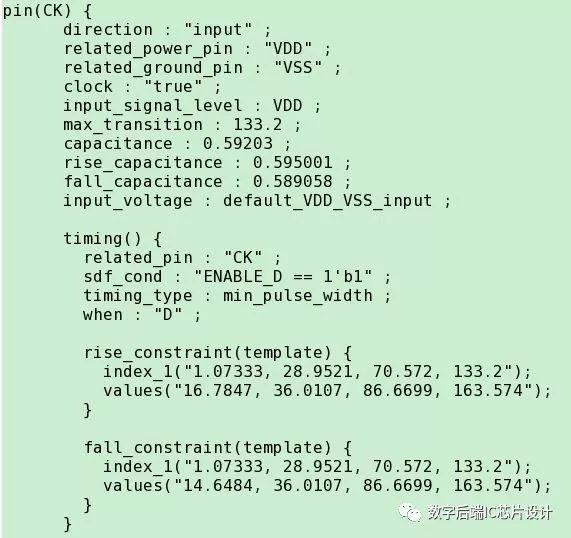

因此,在做timing分析时,我们是必须对cell的pin做min pulse width检查。通常有两类方法:

1) sdc里面定义

set_min_pulse_width 2.0 [get_clocks CK1]

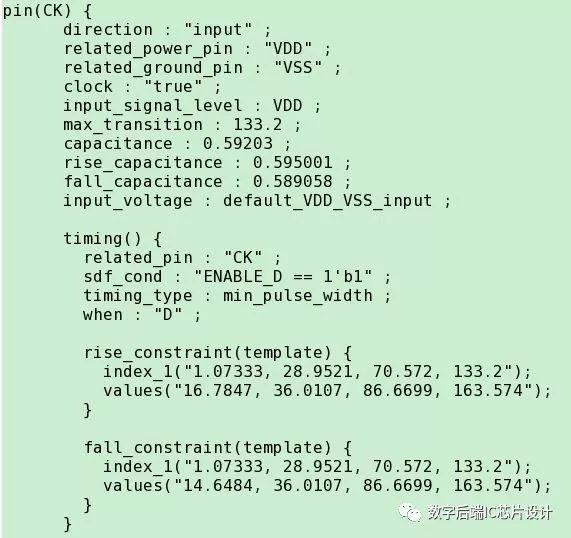

2)library里面定义

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

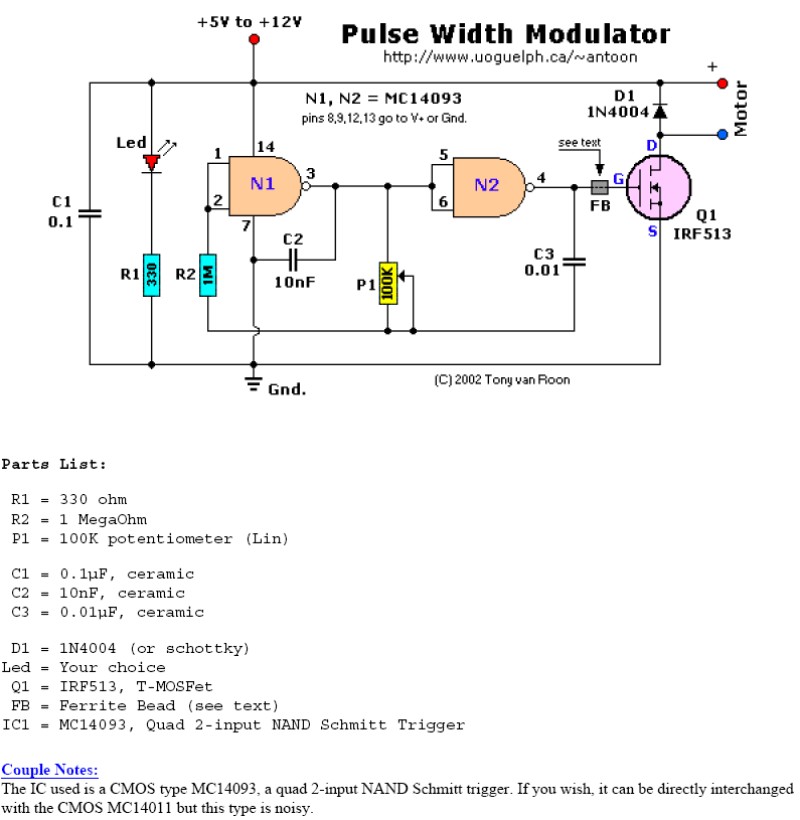

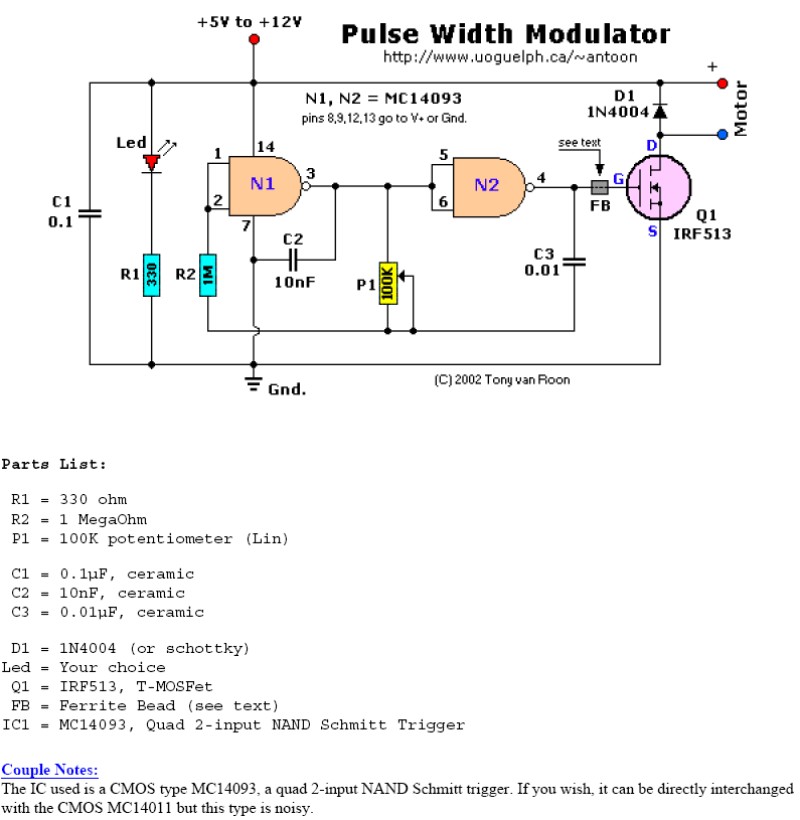

Pulse Width Modulator circuits:Couple Notes:The ic used is a CMOS type MC14093a quad 2-input NAND

发表于 03-14 08:31

•1832次阅读

Abstract: Build a general-purpose pulse-width modulator using three op amps from a quad-op-amp

发表于 05-03 14:33

•657次阅读

Pulse Width Modulation.多种集合,符合热爱PCB绘图的学习者的胃口,喜欢的朋友下载来学习。

发表于 03-21 15:14

•0次下载

PULSE WIDTH VHDL程序,感兴趣的小伙伴们可以瞧一瞧。

发表于 11-11 11:55

•0次下载

时序分析基本概念介绍——时序库Lib。用于描述物理单元的时序和功耗信息的重要库文件。lib库是最

![的头像]() 发表于

发表于 12-15 17:11

•1.2w次阅读

时序分析基本概念介绍——Timing Arc

![的头像]() 发表于

发表于 01-02 09:29

•2.5w次阅读

今天我们要介绍的时序分析概念是Combinational logic. 中文名组合逻辑单元。这是逻辑单元的基本组成器件。比如我们常见的and, or, not, nand,nor等门电

![的头像]() 发表于

发表于 05-14 17:27

•5809次阅读

: true; min_pulse_width_low : 0.126; min_pu

![的头像]() 发表于

发表于 06-17 14:16

•1798次阅读

今天要介绍的时序分析基本概念是lookup table。中文全称时序查找表。

![的头像]() 发表于

发表于 07-03 14:30

•1689次阅读

今天我们要介绍的时序分析概念是clock gate。 clock gate cell是用data signal控制clock信号的cell,它被频繁地用在多周期的时钟path,可以节省

![的头像]() 发表于

发表于 07-03 15:06

•3210次阅读

今天我们要介绍的时序分析概念是 **AOCV** 。全称Stage Based Advanced OCV。我们知道,在OCV分析过程中,我们

![的头像]() 发表于

发表于 07-03 16:29

•2110次阅读

今天我们要介绍的时序分析基本概念是MMMC分析(MCMM)。全称是multi-mode, multi-corner, 多模式多端角

![的头像]() 发表于

发表于 07-04 15:40

•2869次阅读

今天要介绍的时序分析基本概念是Slew,信号转换时间,也被称为transition time。

![的头像]() 发表于

发表于 07-05 14:50

•3637次阅读

今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分

![的头像]() 发表于

发表于 07-06 15:00

•3811次阅读

今天主要介绍的时序概念是时序库lib,全称liberty library format(以• lib结尾),

![的头像]() 发表于

发表于 07-07 17:15

•3338次阅读

时序分析概念min pulse width介绍

时序分析概念min pulse width介绍

评论