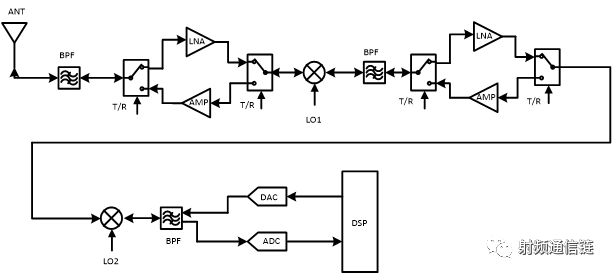

当信号在印制电路板上的传输时,如果信号的工作频率不高,在设计时一般不需要考虑阻抗匹配问题,即可获得较好的信号传输质量。而当电路板的工作频率越来越高,进入射频段时,系统内的高频噪声、串扰等问题造成电路性能下降,因此在高速电路里必须仔细考虑阻抗匹配。

终端匹配的主要目的是实现阻抗匹配以减少信号反射现象的发生,并降低因反射产生的噪声串扰,而最终提供一个完全阻抗匹配的传输环境以确保信号完整性。

终端匹配原理

常用的终端匹配技术主要有戴维南终端匹配技术、串联终端匹配技术以及二极管终端匹配技术三类。

1、戴维南终端匹配技术

将两个终端电阻R1和R2分别连接到电源和地上。由于戴维南终端匹配技术的直流电源直接采用电路的电源,所以不必外加电源。在电阻R1和R2的选择上,原则上是R1与R2并联等于微带线特性阻抗Z0才能实现阻抗匹配,因此最简单的方法为R1=R2=2*Z0,这样戴维南阻抗Rt=(R1*R2)/(R1+R2)=Z0。

戴维南终端技术对上升时间和传输延迟影响不大,所以适用于ECL、TTL、Fast等较高速的电路,但因为直接将终端电阻连接到直流电源上,所以不适合CMOS电路。

2、串联终端匹配技术

串联终端匹配技术的电路,它是在驱动级的输出端串联一个电阻,该电阻尽可能地接近驱动级,即驱动级输出和串联电阻之间的布线尽可能的短,其目的在于使串联电阻成为驱动级的一部分以达到比较好的电阻匹配,如果驱动级输出和串联电阻之间的布线过长,则会出现传输线效应而降低串联电阻的效果。使用串联电阻时需要注意:

(1)驱动级的波形会因为前端电阻而被截取一半,所以在传输线上只有一半的信号。

(2)因为前端电阻,所以接收端所接收到的信号强度为驱动级的一半。

(3)加入前端电阻后,通常上升时间会增加,但反射的信号减小。

(4)串联电阻值由驱动级的输出阻抗和传输线的特性阻抗来决定R=Z0-R0,其中R为串联电阻值,Z0为传输线的特性阻抗,而R0为驱动级的输出电阻。

(5)对信号上升时间的影响,可以将电路看成一个简单的RC低通滤波器,其RC时间常数为Z0C,因此由信号幅度10%上升至信号幅度90%的上升时间为T10%-T90%=2.2Z0RC,即上升时间较慢,但是消化功率较小。其中T10%和T90%分别表示信号幅度10%和信号幅度90%的时间点。

3、二极管终端匹配技术

二极管终端匹配技术的电路,将两个二极管分别反向并连在电源和地端,这种终端技术适合于传输线的阻抗未知时,因为二极管内部的阻抗无法和线路的阻抗匹配,所以该电路无法有效改善反射,但是其主要目的在于可将过冲信号(overshoot和undershoot)限制在VCC+Vf和VGND-Vf的电压范围内,防止有太大的噪声产生并且也可以保护电路元件。

终端匹配仿真实例

在射频电路板设计中,终端匹配技术在很大程度上决定了一个系统的成败,在采取合理的匹配措施之前,首先要对无匹配射频系统中的信号质量有一个直观的了解,本节主要通过75Ω传输线电路仿真来进行讨论,仿真实例主要包括:

1、无匹配75Ω传输线电路仿真及过充现象观察

2、采用戴维南终端匹配技术后,75Ω传输线电路仿真及过冲现象观察

3、采用串联终端匹配技术后,75Ω传输线电路仿真及过冲现象观察。

实现步骤

1、运行ADS,弹出ADS主窗口。利用ADS中的微带线工具进行计算,进行如下设置,可以计算出微带线的长度和宽度。

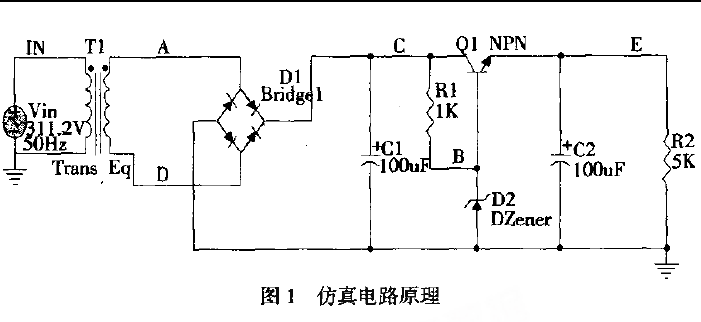

2、建立原理图仿真

3、完成设置后,进行仿真。

再在数据显示窗口中插入一个公式计算器,计算相对过冲电压,单击[Equation]按钮。

可以计算出相对过冲电压0.146

2、戴维南终端匹配技术

通过上一个实验仿真,我们对终端匹配电路造成的过冲电压有了一个直观的认识,要改善这类过冲电压,戴维南终端匹配技术是一个较好的选择。

1、打开原理图“terminal_sim”。将其另存为“terminal_match_parallel”。完成下面的电路图:

2、仿真的结果如下:

3、串联终端匹配技术

相比于戴维南终端匹配技术,串联终端匹配技术实现更为简单,只需要在电路中加入电阻,使输入阻抗与传输线阻抗进行匹配即可。

1、完成下面的电路图

2、开始进行仿真:

-

二极管

+关注

关注

148文章

9852浏览量

168331 -

信号完整性

+关注

关注

68文章

1418浏览量

95845 -

ADS仿真

+关注

关注

1文章

71浏览量

10590 -

直流电源

+关注

关注

8文章

1334浏览量

52826 -

终端电阻

+关注

关注

1文章

95浏览量

11918

发布评论请先 登录

相关推荐

PCB电路板设计仿真不普及的原因

射频电路板设计问题探讨

基于仿真的数字电路板自动测试系统

使用Protel DXP进行电路板级仿真的特点和基本步骤的详细资料说明

射频电路板终端匹配仿真的实现步骤

射频电路板终端匹配仿真的实现步骤

评论