随着半导体行业朝着更先进的制程节点方向发展,静态功耗已成为主要的设计限制因素。为此,亟需开发各种电源管理技术。例如,让开发者可以创建多个电压域,或者使用隔离单元将关断的电源域与上电的电源域隔离。开发者可以在将信号电压从一个域传播到另一个域时,应用电平转换器来放大或缩小信号电压,或者可以使用保留单元来更快地将寄存器恢复到关断前的状态。就像在指定功能设计意图时需要用到硬件描述语言(HDL)一样,这些电源管理技术也需要一种通用语言来指定功耗设计意图,那就是统一电源格式(UPF)。

考虑到当今的SoC非常复杂且通常针对特定的应用,为了设计和实现所需的功能并满足时序和功耗要求,需要付出巨大的努力。但是,仅仅做到这些还是不够。终端用户总是渴望在最短的时间内获得最新的功能,这给IP开发团队带来了压力。为了满足产品上市时间目标,芯片设计公司通常采用并行开发方法,由不同的团队分别编写寄存器传输级(RTL)、新思科技设计约束(SDC)文件、UPF文件等。

尽管设计和UPF的开发是齐头并进的,但它们的时间表可能会有所不同,而这可能会带来一些挑战。本文将介绍如何使用新思科技独立于设计的VC LP UPF检查器(VC UPF)来应对这些挑战。本文还将讨论VC UPF如何帮助开发者在RTL准备好之前清理UPF文件中独立于设计的各种问题。

优化SoC设计的功耗

设计SoC时,UPF的第一个版本可能在RTL最终确定之前就已经准备好了。但只有在设计就绪后,才能验证UPF的准确性和完整性。因此,通常会有一个“等待期”,负责编写UPF的开发者需要等待第一版RTL敲定,才能继续后面的工作。在设计就绪后,开发者会运行一个静态检查器工具来验证UPF与设计的一致性,往往在这时,开发者会发现UPF中存在的一些基本问题,其实这类问题本可以在不读取设计的情况下就能找出。之前的等待实际上已经浪费了一些时间。而反复多次的UPF修复和检查会导致周转时间变得很长。

这就是VC UPF的用武之地。

顾名思义,VC UPF让负责功耗设计意图的开发者能够在RTL就绪之前开始清理UPF文件中独立于设计的问题。该解决方案包括:

UPF语法和语义检查

UPF电源分析检查

PST一致性检查

UPF网络相关一致性检查

方法特定检查(基于允许/不允许的命令和选项)

我们来看几个例子,了解一下该解决方案能提供哪些帮助。

一种情况是UPF电源网络未定义任何电源状态。只有在阅读设计、加载UPF并完成UPF检查之后,用户才会意识到:由于缺少状态,有一些路径无法进行分析。有了VC UPF,开发者将会在几分钟内获得这些信息。

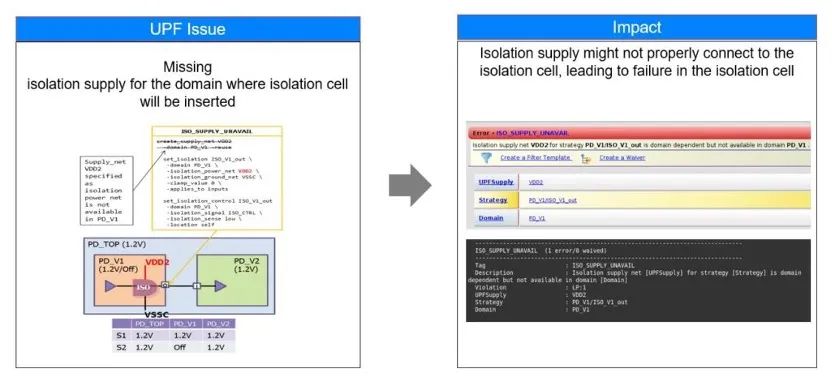

在另一种情况下,用于隔离策略的隔离电源网络在所需的域中可能不可用。

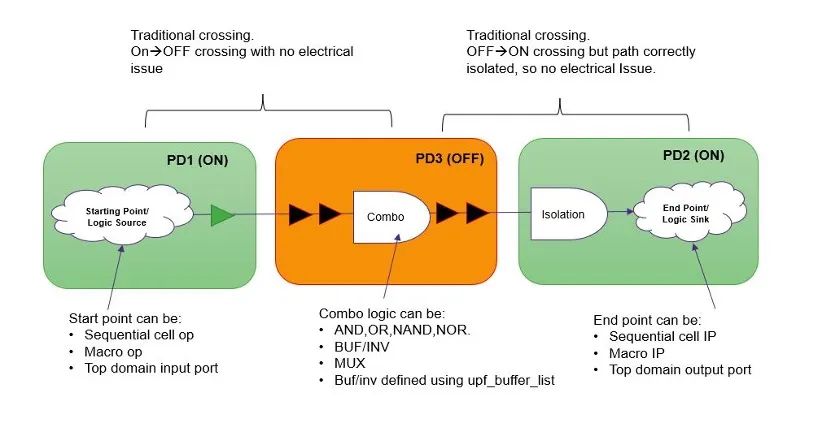

再来看另一个例子,比如从PD3到PD2的路径。由于OFF–>ON交越得到了隔离单元的正确保护,因此不存在电气问题。于是,传统的电气检查不会标记任何违例。但在同一情况下,还存在一个功能问题,即来自PD1的信号会被PD3(电源处于OFF状态)中的组合逻辑电路阻挡。

VC LP中全新的预检查功能可以正确地标记该问题,并提醒开发者:尽管该路径被正确隔离,但来自PD1的信号会被OFF域中的组合逻辑电路阻挡,只有钳位值会到达PD2。

鉴于这一违例,开发者应验证该路径是否要在指示的电源状态期间携带功能信息。如果它在给定的电源状态下不携带功能信息,则无需进一步的操作。但如果该路径需要携带功能信息,则需要为所示的缓冲器/反相器/组合逻辑电路通电,并且需要修复组合逻辑电路的电源连接。通过仿真来识别这些问题非常耗时,而借助VC LP,开发者现在可以在设计周期的早期阶段发现这些问题,从而节省仿真时间。

尽管VC UPF的主要用途是早期清理UPF,但它也可以用于SoC的UPF管理。复杂的SoC具有来自不同供应商/设计团队的IP模块UPF文件,这通常会导致UPF修改推迟、时间表延误,甚至要重新验证。为了避免这些情况,CAD团队可能会强制执行一些GuideWare规则,以符合IP供应商的UPF交付要求,从而确保SoC集成顺利完成。VC UPF可以使用disallow_*命令或allow_*命令来协助执行此类GuideWare UPF架构检查。

类似地,在SoC集成期间,开发者可能不希望某个特定的IP级UPF TCL变量被顶层覆盖。带有设计检查工具的标准UPF不会将这种情况识别为问题。但是,利用VC UPF,开发者可以指定此类受保护变量的列表,并快速发现其中是否有任何变量已被顶层UPF所覆盖。此外,开发者还可以验证IP的UPF版本与SoC UPF的兼容性。根据用户指南中关于允许和禁止的UPF版本组合,VC UPF可以执行IP与SoC的一致性检查。请注意,除此以外,VC LP不考虑UPF版本,使用“upf_version”不会产生任何影响。

经认证的功耗感知静态检查签核

新思科技的VC LP解决方案为UPF提供了准确且经过认证的支持,它与以下工具紧密集成,可用于静态低功耗检查和调试:

总结

毋庸置疑,要设计出满足所需功能、时序和功耗要求的低功耗SoC,需要付出大量精力,而且还面临着产品上市时间紧迫的压力。通常,芯片设计公司选择并行开发方法,由不同的团队分别编写RTL、设计约束文件、UPF文件等。但是,尽管设计和UPF的开发可以齐头并进,但它们的时间表会有所不同。

VC LP解决方案让负责功耗设计意图的开发者能够在RTL就绪之前开始清理UPF文件中独立于设计的问题。该解决方案也可用于SoC的UPF管理,因为复杂的SoC通常具有来自不同供应商的IP UPF文件,而这可能会导致UPF修改推迟、时间表延误,甚至要重新验证。通过在早期阶段清理UPF,开发者可以在低功耗SoC设计周期中节省时间和精力。

原文标题:VC LP解决方案:左手极致低功耗,右手高效验证左移

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

-

新思科技

+关注

关注

5文章

807浏览量

50396

原文标题:VC LP解决方案:左手极致低功耗,右手高效验证左移

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

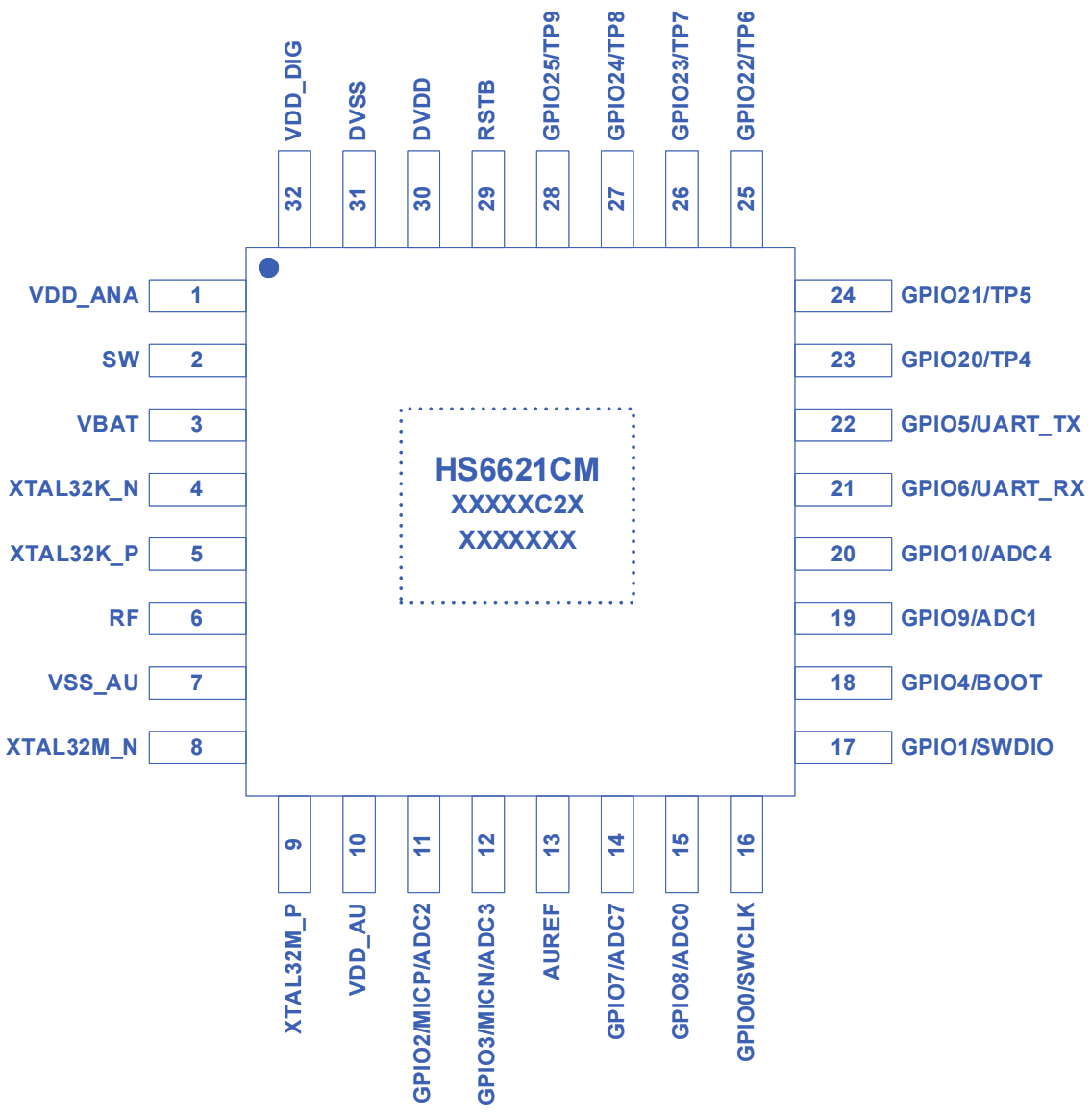

安富利推出S2-LP超低功耗射频收发器

YXC超低功耗时钟解决方案 1.2V超低电平有源晶振 新品发布

引领智能未来:英锐恩科技的国产低功耗单片机ENMCU

低功耗毫米波雷达解决方案使电池供电类接近感应产品实现新功能

适用于超低功耗和低功耗应用的独特高效隔离式DC/DC转换器

炬芯科技低功耗蓝牙SoC通过Apple授权第三方测试机构合规性验证

虹科干货 | 突破功耗限制:PCAN Router设备低功耗模式与高效唤醒

功耗优化的片上系统(SoC)解决方案,引领低功耗蓝牙与2.4GHz应用新潮流

桃芯科技推出的低功耗蓝牙应用方案支持Apple Find My功能

Synopsys推出一款低功耗静态规则检查工具—VCLP

芯原低功耗蓝牙整体IP解决方案已通过LE Audio全部功能认证

新思科技VC LP Advanced静态低功耗验证解决方案

VC LP解决方案:左手极致低功耗,右手高效验证左移

VC LP解决方案:左手极致低功耗,右手高效验证左移

评论