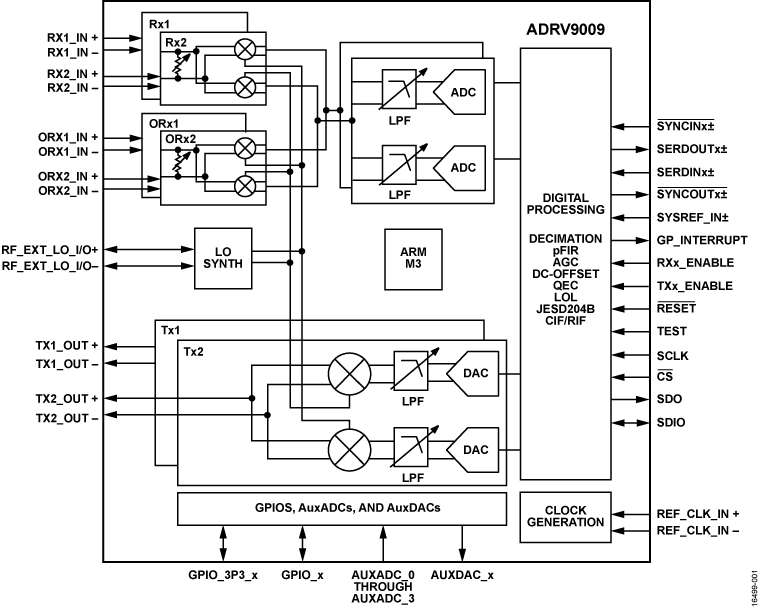

ADRV9009接收链路数字滤波器解读(100MHz带宽)

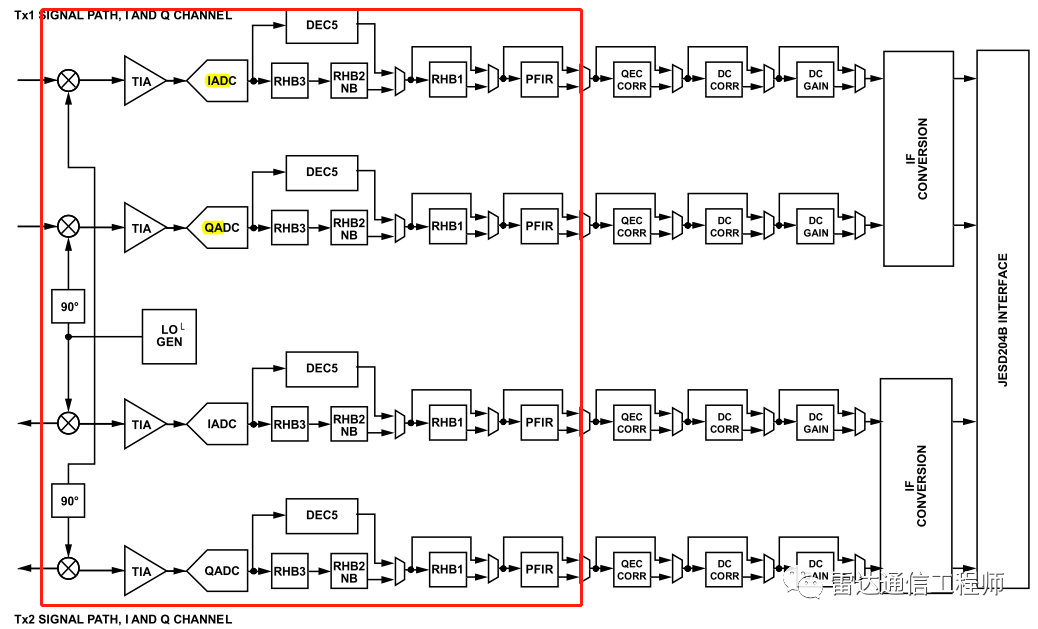

ADRV9009接收链路组成按照信号流向依次为:模拟正交混频(调制与解调)、TIA(跨导放大器)、ADC、第一级抽取、第二级抽取、可编程FIR滤波器(可抽取)、正交校正、直流校正、直流增益、中频变换;

模拟正交混频(解调):

正交混频每通道包含两个混频器和一个正交本振信号,9009中RX1/2、TX1/2共用一个本振产生器,所以只能实现TDD模式,无法实现FDD模式;本振信号由9009内部的PLL以外部参考时钟为基准频率综合而来,本振信号的关键指标“相位噪声”会对发射调制信号的EVM和接收机的性能有重大影响,硬件上设计中需要外部参考时钟的信号质量(相位噪声等),另外一个重要的点是零中频正交解调后I/Q支路的信号的基带带宽只有实信号的一半。关于正交调制解调的更多分析不在本文范围内。

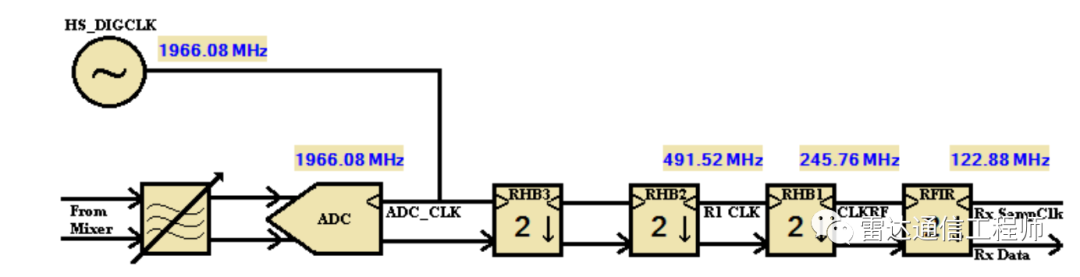

100MHz信号带宽案例(采样率:1966.08MHz)

重点:抽取与抗混叠

采样系统都必须满足奈奎斯特采样定理(即采样率必须大于等于信号带宽的两倍);而工程中一般保持最小约2.5倍的关系,9009中也基本满足这个关系;经过R倍抽取过程后,采样数据多能承载的最大信号带宽(fs/2)将相应的降低 R倍,抽取后的fs/2与信号带宽越接近,该抽取滤波器的过渡带就要越窄(要保证带外抑制度则需要更高的阶数),所以一般越后级的抽取滤波器阶数越高。

第一级抽取(DEC5倍/半带4倍抽取)

第一级抽取系数根据信号带宽参数将选择5倍抽取或者4倍抽取

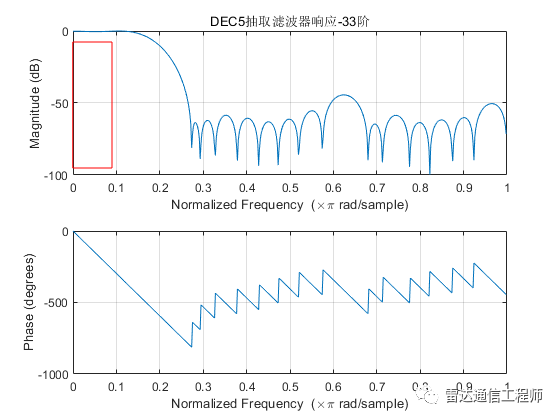

5倍抽取:

- 因是1/5抽取,故无法使用半带滤波器,从系数情况来看DEC5应该是一个FIR滤波器;

- 直接进行5倍抽取,为能有效抗混叠,使用了一个较高的33阶滤波器;

- DEC5从分析来看应该是在信号带宽为100~200MHz之间的某些值时使用,如150MHz;

DEC5=[0.002197, 0.004272, 0.006836, 0.008789, 0.008545, 0.003418, -0.004639, -0.015381, -0.025512, -0.029785, -0.022461, -0.002441,...

0.03125, 0.074707, 0.119141, 0.155396, 0.176758, 0.176758, 0.155396, 0.119141, 0.074707, 0.03125, -0.002441, -0.022461, -0.029785,...

-0.025512, -0.015381, -0.004639, 0.003418, 0.008545, 0.008789, 0.006836, 0.004272, 0.002197];

freqz(DEC5);title('DEC5抽取滤波器响应-33阶');

annotation('rectangle',[.13 .6 .07 .3],'Color','red');%[x y w h]

%% 1.0代表的频率为Fs/10(即Fs/5/2),

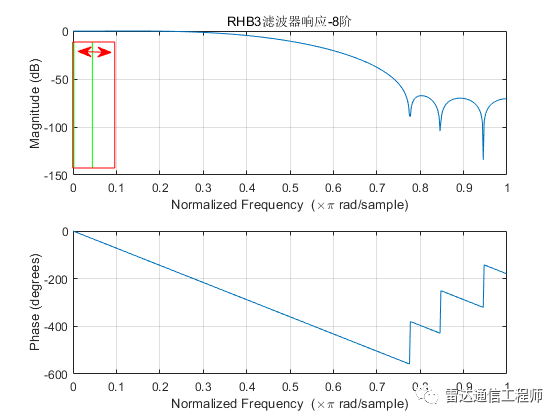

4倍抽取:两级HB

- 4倍抽取使用两级HB半带滤波器级联实现;

- 第一级HB滤波器为8阶,而第二级HB滤波器为18阶;

- 第一级HB滤波器输入的采样率最高(Fs=1966.08MHz),案列中I/Q支路基带信号带宽为50MHz,故可以较低的滤波器阶数(对滚降要求较低)实现抽取滤波而不混叠;

- 此案例中第一级滤波器的通带约0.23归一化频率(约230MHz),DC~100MHz带内平坦度0.2dB;

- 混叠说明:9009为实现最大200MHz带宽,该HB滤波器需要有效阻止DC

100MHz以外的信号在抽取后混叠到带内,2倍抽取中混叠将使0.51.0频率部分的信号混叠进入0.50(即沿0.5对折的关系),该滤波器实际可以有效阻止0.771.0处的混叠到0.230区间(注意前后对应关系),而滤波器在0.771.0区间的抑制大于67dBc,基础消除了混叠的影响,另外0.23~0.77的过度区间一样也会发生混叠,但是该区间位于信号带宽之外较远处,可以由后续的滤波器进行滤除;后续几级滤波器都可用同样的分析思路进行分析,将不再一一说明。

RHB3=[-0.01874, -0.04218, 0.050476, 0.293884, 0.439636, 0.293884, 0.050476, -0.04218, -0.01874];

freqz(RHB3);title('RHB3滤波器响应-8阶');

annotation('rectangle',[.132 .6 .033 .3],'Color','green');%[x y w h],案列中信号带宽

annotation('rectangle',[.13 .6 .075 .3],'Color','red');%[x y w h],9009最大支持带宽

annotation('doublearrow',[0.1393 0.1983],[0.8775 0.8751],'Color','red');

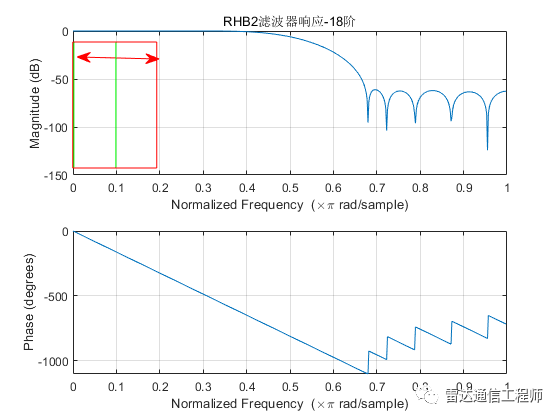

- 第二级HB抽取,滤波器阶数增加到18阶,通带增加,过渡带降低,阻带抑制大于60dBc;

- 此时的输入数据率已经降低为Fs/2,信号带宽所占归一化频率扩大为DC

0.2(即DC50MHz); - HB滤波器定义上的通带为0.32,0.2(即100MHz)的带内平坦度为0.004dB,因此该滤波器同样可以保证IQ支路100MHz(实信号200MHz)的抗混叠;

- 原理同上,该滤波器可以有效阻止0.68

1.0区间信号混叠到0.32DC区间,因此DC0.2的信号带内不会受到混叠影响,且还留有“安全保护带”(0.20.32);

RHB2=[0.003174, 0, -0.01239, 0, 0.03418, 0, -0.08551, 0, 0.310913, 0.5, 0.310913, 0, -0.08551, 0, 0.03418, 0, -0.01239, 0, 0.003174] ;

freqz(RHB2);title('RHB2滤波器响应-18阶');

annotation('doublearrow',[0.284 0.1376],[0.8595 0.8643],'Color','red');

annotation('rectangle',[.132 .6 .075 .3],'Color','green');%[x y w h],案列中I、Q信号带宽:50MHz

annotation('rectangle',[.13 .6 .15 .3],'Color','red');%[x y w h],9009最大支持带宽

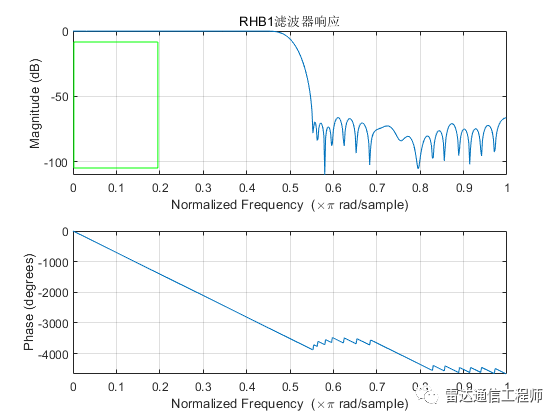

第二级抽取(RHB1半带抽取)

- 经过第一级抽取后,数据率降低为Fs/4(信号带宽不变);

- 为了避免混叠,第二级抽取滤波器需要比第一级更高的阶数,以保证更高的滚降特性(窄的过渡带);

- 9009中第二级抽取采用78阶HB半带滤波器,从频率响应图中可以看出其过渡带很窄(不超过0.1的归一化频率),滚降速率明显高于第一级抽取,且带外抑制达到70dBc;

- 9009配置为200MHz带宽时该滤波器将被旁路,即不进行抽取滤波;

RHB1=[-0.000122, 0, 0.000244, 0, -0.000488, 0, 0.000854, 0, -0.001221, 0, 0.001831, 0, -0.002502, 0, 0.003479, 0,...

-0.004700, 0, 0.006287, 0, -0.008179, 0, 0.010620, 0, -0.013611, 0, 0.017578, 0, -0.022766, 0, 0.030029, 0, -0.040955, 0, 0.059998, 0,...

-0.103027, 0, 0.313721, 0.493652, 0.313721, 0, -0.103027, 0, 0.059998, 0, -0.040955, 0, 0.030029, 0, -0.022766, 0, 0.017578, 0, -0.013611,...

0, 0.010620, 0, -0.008179, 0, 0.006287, 0, -0.004700, 0, 0.003479, 0, -0.002502, 0, 0.001831, 0, -0.001221, 0, 0.000854, 0, -0.000488, 0,...

0.000244, 0, -0.000122];

freqz(RHB1);title('RHB1滤波器响应');

annotation('rectangle',[.132 .6 .15 .3],'Color','green');%[x y w h],案列中I、Q信号带宽:50MHZ

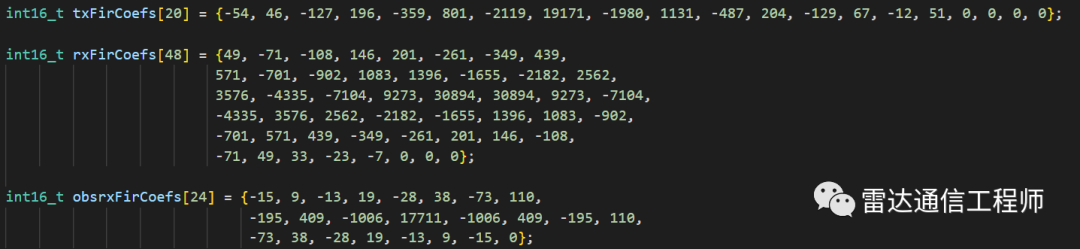

第三级抽取(RFIR可编程FIR滤波器)

-

RFIR滤波器支持1、2、4倍抽取,或者旁路。

-

使用RFIR以补偿模拟TIA低通滤波器的频响衰减。

-

RFIR可以使用24、48或72阶,IQ输出数据率越低则滤波器阶数越高,输出数据率越低RFIR的抽取率越大,为了抗混叠,滤波器阶数要相应增加;

-

RFIR具有可编程增益:+6 dB, 0 dB, −6 dB, or −12 dB;

-

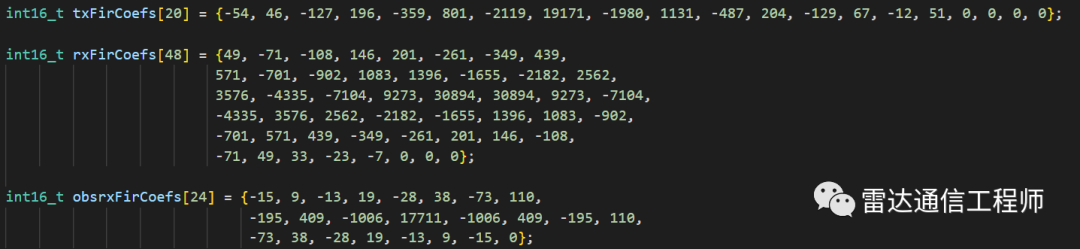

PFIR滤波器的系数是可以通过API接口进行在线参数配置的,而前面的其他滤波器则都是固定滤波器系数,PFIR的滤波器系数来自ADI的配置工具,由其根据用户输入的带宽、采样率等信息的计算后生成滤波器系数,可导出为c代码配置文件,如下图所示

-

最大抽头数受FIR时钟速率(数据处理时钟,DPCLK)限制。最大DPCLK时钟速率为500 MHz。DPCLK时钟速率是ADC时钟速率除以4或5。当使用HB2和HB3时,ADC时钟速率被4除HB3过滤器,并除以5时使用DEC5过滤器。DPCLK时钟速率会影响最大可用的RFIR滤波器抽头数,如下式所示。最大滤波器抽头数 = (DPCLK Clock Rate ÷ Receiver I/Q Data Rate) × 24 ;

-

本案列中RFIR的DPCLK为245.76MHz,接收IQ数据率122.88MHz,故RFIR阶数为48阶;

总结

9009通过灵活控制采样速率和抽取系数实现不同的带宽配置,但为了和JESD204B最低接口速率匹配,9009存在一个最低可配置带宽,从官方的配置软件来看,最小带宽为40MHz;如果用户需要小于40MHz的信号带宽,需要在FPGA的基带处理中实现第二次抽取(RX)和插值(TX)。

-

调制解调器

+关注

关注

3文章

854浏览量

38810 -

混频器

+关注

关注

10文章

679浏览量

45684 -

TDD

+关注

关注

1文章

121浏览量

38189 -

fir滤波器

+关注

关注

1文章

95浏览量

19039 -

跨导放大器

+关注

关注

1文章

16浏览量

10657

发布评论请先 登录

相关推荐

使用FPGA构建的数字滤波器设计方案

ADRV9009板卡学习资料:FMCJ450-基于ADRV9009的射频收发模块

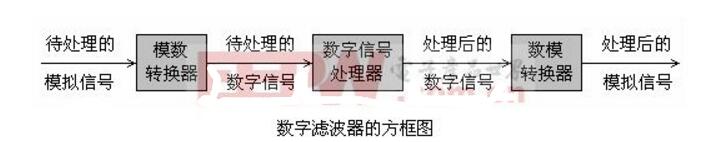

数字滤波器(DF)的基本结构

数字滤波器的结构

数字滤波器的原理及其设计

数字滤波器,数字滤波器原理是什么?

ADRV9009 集成式双射频发射器、接收器和观察接收器

ADRV9009接收链路数字滤波器分析

ADRV9009接收链路数字滤波器分析

评论