建立时间 :时钟上升沿之前数据保持稳定时间

保持时间:在时钟上升沿之后数据保持稳定的时间。

建立时间Tsu

根据时钟周期公式:

Tco+Tdata+Tsu-Tskew< Tcycle

可以推导出建立时间的裕量Sslack为:

Tcycle-(Tco+Tdata+Tsu-Tskew) >0

当Sslack大于等于0时即满足建立时间的要求。

保持时间Th

保持时间的目的是防止下一次的数据传输过快,将本次的数据冲刷掉,是对上次数据时间的约束。经过Tsu建立时间之后,触发器进入建立时间阶段,在该阶段最担心的问题是下一次的数据来的太快,导致还未满足保持时间的要求。

所以要求下一次数据到来的时间要大于Th,而下一次数据到来的时间为:

Tco+Tdata-Tskew

所以保持时间裕量计算公式为:

Hslack=(Tco+Tdata-Tskew) >0

扇入与扇出

扇入 :扇入系数是指门电路允许有几个输入,一般门电路允许的扇入系数为1~5,最多不超过8。

扇出 :扇出系数是指门电路允许驱动同类型的门的个数,也就是负载能力,一般门电路的扇出系数为8,驱动器的扇出系数为25,体现了门电路的驱动能力。

灌电流与拉电流

灌电流:当门电路的输出端为低电平时,逻辑门的输入电流为灌电流。灌电流越大,逻辑门输出低电平就越高。

拉电流:当门电路的输出端为高电平时,逻辑门的输出电流为拉电流。拉电流越大,逻辑门的输出高电平就越低。

上拉电阻和下拉电阻

上拉电阻:上拉电阻就是将一个不确定信号的电平钳位在高电平(拉电流),来增加高电平时的驱动能力,以解决逻辑门驱动能力不足的问题。

下拉电阻:下拉电阻就是将一个不确定信号的电平钳位在低电平(灌电流),其作用是吸收电流,防止灌电流过大提高逻辑门的输出电压大小。

当输出负载大于其负载能力时:

1、 逻辑门输出低电平时,可能灌电流过大,输出电压Vol可能大于规定的Volmax

2、 逻辑门输出高电平时,可能拉电流过大,输出电压Voh可能小于规定的Vohmin

3、 输出的传播延时大于规格说明的延迟值,主要表现为Net_delay(Tdata)

4、 输出的上升和下降时间可能会高于规定值

5、超负载工作,电流较大,降低其可靠性,最终引起器件失效

Setup Violation与Hold Violation

根据建立时间公式Tsu:

Tcycle-(Tco+Tdata+Tsu-Tskew) >0

以及保持时间公式Th:

Hslack=(Tco+Tdata-Tskew) >0

当发生Setup Vioalation或Hold time Violation时,由于Tco是寄存器的固有属性,系统时钟一般也是固定的,可通过减小Tdata(当Sslack<0时)或者增大Tdata(当Hslack<0时),完成时序违例的优化:

举一反二,以保持时间违例进行说明,控制Tdata,Tdata包含数据延迟和布线延迟两部分,其关键在于如何降低数据延迟和布线延迟。

(1)、减小扇出Fanout,根据上文的分析可以分析Fanout较多时增加Net_delay,不利于时序收敛。减小扇出的方法有:

a、寄存器复制,几个寄存器复制原先的驱动信号,分担原本由一个寄存器驱动的多个模块。

b、设置Max_Fanout,在代码中设置信号属性,将对应的Max_Fanout设置为一个合理的值,当实际中fanout超过此值时,综合器极性自动优化,但是过低的扇出可能造成设计阻塞反而不利于约束。

c、BUFG,全局缓冲

(2)、减小逻辑级数Logic Level,一个Logic Level的延迟对应的是一个LUT(查找表)和一个Net的延迟,对应不同的器件,不同频率的设计所能容纳的Logic Level不同,一般可通过重定时(Retiming)解决Logic Level过大问题,使用的方法为:流水线,将过于冗长的组合逻辑增加寄存器进行打拍。对于时钟偏斜△T来说因为不确定正负,其对建立时间和保持时间的影响是相反的,所以我们希望|△T|尽可能的小,所以尽量不要用生成时钟,而采用全局时钟,这样才会有更小的|△T|。

-

驱动器

+关注

关注

54文章

8372浏览量

147683 -

上拉电阻

+关注

关注

5文章

363浏览量

30822 -

寄存器

+关注

关注

31文章

5390浏览量

121901 -

门电路

+关注

关注

7文章

200浏览量

40358 -

触发器

+关注

关注

14文章

2024浏览量

61494

发布评论请先 登录

相关推荐

【FPGA经典试题】电路模块的setup-time和hold-time是正值还是负值

解释下setup和hold time

警告-- Removed fan-out from the always-disabled I/O buffer 是什么意思

allegro PCB editor: 做到BGA Fan out 的时候,怎么设置BGA FAN OUT 的信号点 扇出到第几层 ?

关于quartus上的RTL图的读法,将光标放在线上时,能看到fan-out= 3 ,请问这是什么意思,还有一个问题。

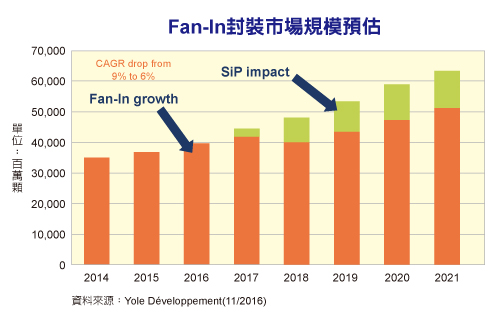

SiP封装需求持续增加威胁Fan-In封装未来发展

建立时间和保持时间(setup time 和 hold time)

为什么setup检查下一个沿而hold检查当前沿

UM2695_用于STM32探索套件和评估板的STMod_ fan_out扩展板

从fan-in、fan-out看setup和hold time violation

从fan-in、fan-out看setup和hold time violation

评论